Микропрограммный УА с естественной адресацией

Структура, предлагаемая в аппарате с принудительной адресацией, удобна, но можно заметить, что большинство МК в ПЗУ идут подряд, а те, которые не подчиняются этому правилу, нередко можно переставлять местами. Это относится к состояниям «с буквами» в предыдущем примере, когда автомат, фактически находясь в одном состоянии, проверяет какой-то набор входных сигналов.

Поэтому логично представить себе автомат, имеющий в своём составе вместо адресного мультиплексора MS2 и регистра РАМК простой счётчик адреса с возможностью предзагрузки, которой мы могли бы воспользоваться для выполнения перехода в несмежное с текущим состояние.

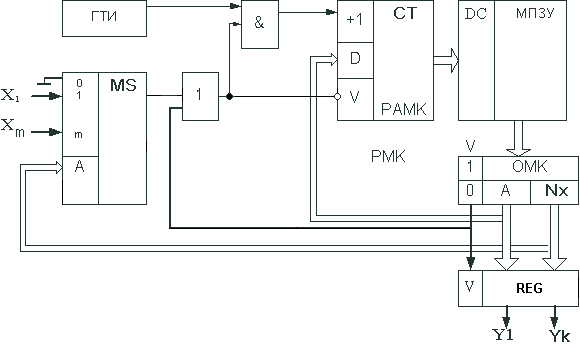

Такие МП автоматы называются автоматами с естественной адресацией – рис 8.

Рис 8. Структура МП УА с естественной адресацией.

Можно заметить, что здесь есть 2 вида микрокоманд (РМК на рисунке), различающихся старшим битом V:

0 – ОМК – операционная микрокоманда, содержащая во всех остальных разрядах сигналы Y.

1 – УМК – управляющая микрокоманда, т.е. МК перехода. Её поле A – адрес перехода, подаётся на входы предзагрузки счётчика. Nx – то же, что и выше – код проверяемого сигнала Xi. Безусловный переход реализуется подобно первому варианту – фиксированным лог. 0 на одном из входов MS. Т.е. автомат выполняет переход, если Xi==0.

Счётчик-РАМК при V=0 выполняет загрузку со входов D, при V=1 выполняется счёт (инкремент – увеличение значения на 1) по тактовым импульсам на входе +1.

В структуре автомата также появился ещё один дополнительный регистр – REG. Его задача – сохранять выходные сигналы автомата, когда тот выполняет команды переходов (V==1). При V==0 регистр прозрачен, передаёт состояние входов на выходы. На выходе REG можно ставить ДШМО, как в первом случае. Соображения по целесообразности его установки совершенно те же, что и для принудительной адресации.

Функционирование такого автомата несколько отличается от предыдущего варианта с принудительной адресацией.

Если автомат выполняет ОМК, то 1 из старшего бита МК блокирует мультиплексор входных сигналов MS элементом ИЛИ и запрещает счётчику-РАМК выполнять предзагрузку адреса перехода. Одновременно выходной регистр сохраняет в себе выходные сигналы автомата. По приходу следующего тактового импульса счётчик увеличится на 1, выбирая следующую МК.

Если выполняется УМК, то выходной регистр блокируется сигналом V=0, а элемент ИЛИ разрешает прохождение сигнала мультиплексора. Далее, если Xi==0, то прохождение тактовых импульсов на счётчик запрещается, но разрешается предзагрузка его значением пола A микрокоманды – выполняется переход. Если Xi==1, то предзагрузка запрещена, разрешен проход тактового импульса – перехода нет.

Рассмотрим разработку МП для такого автомата на примере:

| Сост. | x1 | x2 | y1 | y2 | y3 | y4 |

| * | * | |||||

| * |

Это тот же пример, что и выше, но с двумя доп. состояниями 6 и 7.

Также, как и раньше, нам сначала необходимо закодировать входные сигналы автомата x1, x2 и постоянный лог. 0 на нулевом входе мультиплексора MS1:

| Вход | Поле Nx микрокоманды |

| 0 (лог. 0) | |

| 1 (x1) | |

| 2 (x2) |

Затем составляем микропрограмму автомата (прошивку ПЗУ):

| Адрес МК (состояние) | V | МК |

| 00000 (сост. 0а) | 0 (ОМК) | Y=1011 |

| 00001 (сост. 0б) | 1 (УМК) | Nx=10 (x2), A=00001 |

| 00001 (сост. 0в) | 1 (УМК) | Nx=01 (x1), A=00011 |

| 00010 (сост. 0г) | 1 (УМК) | Nx=00 (лог. 0), A=00001 – безусловный переход |

| 00011 (сост. 1а) | 0 (ОМК) | Y=0001 |

| 00100 (сост. 1б) | 1 (УМК) | Nx=01 (x1), A=00100 |

| 00101 (сост. 1в) | 1 (УМК) | Nx=10 (x2), A=00100 |

| 00110 (сост. 2а) | 0 (ОМК) | Y=0111 |

| 00111 (сост. 2б) | 1 (УМК) | Nx=01 (x1), A=00111 |

| 01000 (сост. 2в) | 1 (УМК) | Nx=10 (x2), A=01011 |

| 01010 (сост. 2г) | 1 (УМК) | Nx=00 (лог. 0), A=00111 – безусловный переход |

| 01011 (сост. 3а) | 0 (ОМК) | Y=0000 |

| 01100 (сост. 3б) | 1 (УМК) | Nx=01 (x1), A=01100 |

| 01101 (сост. 3в) | 1 (УМК) | Nx=10 (x2), A=01100 |

| 01110 (сост. 4а) | 0 (ОМК) | Y=1111 |

| 01111 (сост. 4б) | 1 (УМК) | Nx=01 (x1), A=10001 |

| 10000 (сост. 4в) | 1 (УМК) | Nx=00 (лог. 0), A=01111 – безусловный переход |

| 10001 (сост. 4г) | 1 (УМК) | Nx=10 (x2), A=10011 |

| 10010 (сост. 4д) | 1 (УМК) | Nx=00 (лог. 0), A=01111 – безусловный переход |

| 10011 (сост. 5а) | 0 (ОМК) | Y=0111 |

| 10100 (сост. 5а) | 1 (УМК) | Nx=10 (x2), A=10100 |

| 10101 (сост. 5б) | 1 (УМК) | Nx=01 (x1), A=10111 |

| 10110 (сост. 5в) | 1 (УМК) | Nx=00 (лог. 0), A=10100 – безусловный переход |

| 10111 (сост. 6а) | 0 (ОМК) | Y=0111 |

| 10111 (сост. 7а) | 0 (ОМК) | Y=1011 |

| 10111 (сост. 7б) | 1 (УМК) | Nx=01 (x1), A=00000 |

| 11000 (сост. 7в) | 1 (УМК) | Nx=00 (лог. 0), A=10111 – безусловный переход |

Требуемая адресность ПЗУ равна 5 (5-разрядный адрес), а его разрядность равна 1 + max (4, 2 + 4) =1 + max (4, 6) = 1+6=7.

Полная ёмкость ПЗУ составит 32 ячейки, из которых мы заняли 27.

Отметим, что:

- кол-во состояний автомата с естественной адресацией существенно больше кол-ва состояний даже автомата с принудительной адресацией. Это вызвано невозможностью непосредственного перехода при Xi==1, в таких ситуациях необходимо сочетание условного и безусловного перехода.

- требуемая разрядность ПЗУ меньше, чем для автомата с принудительной адресацией. Адресность – наоборот.