Краткий обзор архитектуры IA-64

Системы команд многих RISC-процессоров во многом похожи друг на друга. Например, говорят, что в этом смысле MIPS и Alpha близки друг к другу. Однако появление архитектуры IA-64, которая претендует на монополию на рынке микропроцессоров, разработчики из HP и Intel характеризуют как наступление эры "пост-RISC". Доступная информация свидетельствует, что IA-64 революционным образом отличается от предшественников, даже от своих прямых предков таких, как HP PA-RISC. Процессоры с архитектурой IA-64 (Merced, McKinley и т.д.) могут обойти RISC-процессоры по производительности. Микроархитектура E2K (разработка СССР), имела близкие к IA-64 архитектурные особенности.

Традиционные части системы команд IA-64 напоминают обычный набор команд RISC, в первую очередь архитектуры PA-RISC. Совместимость с PA-RISC в IA-64 обеспечивается за счет динамической трансляции команд (т.е. подобно Compaq/DEC FX!32). Применительно к прикладным программам такой подход оказывается вполне эффективным благодаря близости части команд PA-RISC к соответствующим командам IA-64.

Наиболее кардинальным нововведением IA-64 по сравнению с RISC является "явный параллелизм команд (EPIC - Explicitly Parallel Instruction Computing), привносящий в IA-64 некоторые элементы, напоминающие архитектуру "сверхбольшого командного слова" (VLIW - Very Large Instruction Word). В обеих архитектурах явный параллелизм представлен уже на уровне команд, управляющих одновременной работой функциональных исполнительных устройств (ФИУ). Соответствующие "широкие команды" HP/Intel назвали связками (bundle).

Рис. 11.1. Формат связки команд IA-64

Связка имеет длину 128 разрядов (рис. 11.1.). Она включает 3 поля - "слота" для команд длиной 41 разрядов каждая, и 5-разрядное поле шаблона. Предполагается, что команды связки могут выполняться параллельно разными ФИУ. Возможные взаимозависимости, препятствующие параллельному выполнению команд связки, отражаются в поле шаблона. Не утверждается, впрочем, что параллельно не могут выполняться и команды разных связок.

Шаблон указывает, какого типа команды находятся в слотах связки. В общем случае команды одного типа могут выполняться в более чем одном типе ФИУ. Шаблоном задаются так называемые остановки, определяющие слот, после начала выполнения команд которого команды последующих слотов должны ждать завершения. Порядок слотов в связке (возрастание справа налево) отвечает и порядку байт - little endian. Однако данные в памяти могут располагаться и в режиме big endian. Режим устанавливается специальным разрядом в регистре маски пользователя.

Последовательность команд от остановки до остановки (или выполняемого перехода) называется группой команд. Она начинается с заданного адреса команды (адрес связки плюс номер слота) и включает все последующие команды - с увеличением номера слота в связке, а затем и адресов связок, пока не встретится остановка.

РЕГИСТРЫ

В их число входят: 128 регистров общего назначения GR; 128 регистров с плавающей запятой FR; 64 регистра предикатов PR; 8 регистров перехода BR; 128 прикладных регистра AR; не менее 4 регистров идентификатора процессора CPUID; счетчик команд IP, указывающий на адрес связки, содержащей исполняемую команду; регистр маркера текущего окна CFM, описывающий окно стека регистров и др.

Регистры CPUID являются 64-разрядными. В CPUID-регистрах 0 и 1 лежит информация о производителе, в регистре 2 находится серийный номер процессора, а в регистре 3 задается тип процессора (семейство, модель, версия архитектуры и т.п.) и число CPUID-регистров. Разряды регистра 4 указывают на поддержку конкретных особенностей IA-64, т.е. тех, которые реализованы в данном процессоре.

Прикладные регистры AR0-AR127 - специализированные (в основном 64-разрядные) регистры, применяемые в IA-64 и IA-32. AR0-7 называются регистрами ядра; запись в них привилегированна, но они доступны на чтение в любом приложении и используются для передачи приложению сообщений от операционной системы.

Среди других прикладных регистров укажем на AR16 (RSC) - регистр конфигурации стека регистров, используемый для управления работой "машиной" стека регистров IA-64 (RSE); AR17 (BSP), в котором находится адрес в памяти, где сохраняется положение GR32 в текущем окне стека; AR40 (FPSR) - регистр состояния для команд с плавающей запятой IA-64; AR44 (ITC) - интервальный таймер; AR64 (PFS) - регистр предыдущего состояния функции, куда автоматически копируются некоторые другие регистры при вызове подпрограмм; AR65 (LC), используемый для организации циклов со счетчиком, и, наконец, 6-разрядный регистр эпилога AR66 (EC). Ряд AR-регистров является фактически регистрами IA-32 (дескриптор сегмента кодов, дескриптор сегмента стека и др.).

64-разрядные регистры GR0-127 применяются не только для целочисленных операций IA-64; GR8-31 в режиме IA-32 используются также под целочисленные регистры и регистры селекторов и дескрипторов сегментов IA-32. GR0-31 называются статическими регистрами, а GR32-127 – регистрами стека. Статические регистры "видны" всем программам. Стекируемые регистры становятся доступными в программной единице через окно стека регистров, включающее локальные и выходные регистры, число которых задается командой alloc.

82-разрядные регистры с плавающей запятой FR0-127 также подразделяются на статические (FR0-31, причем всегда FR0=0.0, FR1=1.0) и вращаемые (FR32-127). FR8-31 в режиме IA-32 содержат числа с плавающей запятой и мультимедийный регистры.

Вращение регистров является в некотором роде частным случаем переименования регистров, применяемого во многих современных суперскалярных процессоров с внеочередным спекулятивным выполнением команд. В отличие от них, вращение регистров в IA-64 управляется программно. К обсуждению вращения регистров мы вернемся ниже, а содержимое FR будет рассмотрено в разделе, посвященном операциям с плавающей запятой.

64-разрядные регистры переходов BR0-7 применяются для указания адреса перехода в соответствующих командах перехода (если адрес перехода не кодируется в команде явно). Регистры предикатов PR0-63 являются одноразрядными; в них помещаются результаты команд сравнения. Обычно эти команды устанавливают сразу два регистра PR в зависимости от условия - соответственно истинность условия и его отрицания. Такая избыточность обеспечивает дополнительную гибкость.

В отечественном микропроцессоре E2K [3] предикатных регистров в два раза меньше. Хотя это позволяет хранить столько же условий, сколько в IA-64, в последней предикатные регистры применяются еще и для организации программно конвейеризованных циклов (Software Pipelining - SWP). Использование предикатных регистров - важнейшая особенность, кардинально отличающая IA-64 от всех других микропроцессоров, кроме E2K.

PR0-15 являются статическими (PR0 всегда равен 1), а PR16-63 - вращаемыми. Статические предикатные регистры используются в командах условного перехода. Кроме того, почти все команды IA-64 могут быть выполнены "под предикатом".

Работа стека регистров

Файл регистров GR отличается от FR и PR тем, что последние содержат фиксированные подмножества статических и вращаемых регистров, в то время как в файле GR вне подмножества статических регистров применяется стек регистров, и программной единице доступна лишь его часть - окно стека регистров. В отличие от статических регистров, стекируемое подмножество локально для любой программной единицы и может иметь размер от 0 до 96 регистров, начиная с GR32.

Использование этого механизма в IA-64 позволяет, как мы увидим, избежать накладных расходов, связанных с сохранением/восстановлением большого числа регистров при вызовах подпрограмм и возвратах из них (однако статические регистры при необходимости все-таки приходится сохранять и восстанавливать, явно кодируя соответствующие команды). Автоматическое сохранение/восстановление стекируемого подмножества регистров осуществляет RSE, и в программе об этом заботиться не надо. В режиме IA-32 работа с этим стеком регистров, естественно, отключается.

Один из регистров IA-64 - 38-разрядный регистр CFM сохраняет состояние "текущего" окна стека регистров. Как и другие маркеры окна, CFM содержит общий размер окна стека, число локальных регистров и (кратное 8) число вращаемых регистров в окне, а также 3 значения базы для переименования регистров - соответственно rrb.gr, rrb.fr и rrb.pr.

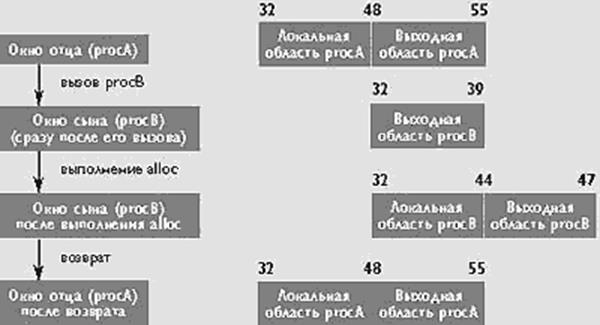

Итак, окно стека имеет две области переменного размера - локальную и выходную. Рассмотрим вызов процедур подробнее. При переходе типа "вызов процедуры" CFM вызывающей подпрограммы сохраняется в поле PFM (Previous Frame Marker) регистра PFS, и создается CFM вызываемой подпрограммы. Сразу после вызова размер локальной области вызываемой подпрограммы равен размеру выходной области вызывающей и перекрывается с ней. При этом стекируемые регистры автоматически переименовываются таким образом, что первый регистр выходной области вызывающей подпрограммы становится регистром GR32 вызываемой (рис.2, где procA - это вызывающая, а procB - вызываемая подпрограмма). Перекрытие их выходных областей позволяет эффективно передавать параметры через регистры.

Рис. 11.2. Стек регистров при вызове procB из procA

Как мы уже указывали, вызываемая подпрограмма может изменить размеры своих локальной и выходной областей командой alloc; соответствующим образом будут изменены и поля в CFM. Команда alloc обычно используется вызываемой подпрограммой для того, чтобы распределить себе определенное число локальных регистров и заиметь выходную область для передачи параметров уже собственному "потомку". Если запрошенное в команде alloc количество регистров оказывается недоступным (переполнение стека), alloc приостанавливает процессор и RSE будет сохранять регистры вызывающей подпрограммы, пока запрошенное alloc число регистров не будет доступным.

При переходе типа "возврат из процедуры" CFM восстанавливается из PFM, а обратное переименование регистров восстанавливает состояние вызывающей подпрограммы. Если некоторые ее регистры были ранее "сброшены" RSE, то при возврате RSE приостановит процессор до тех пор, пока не будут восстановлены эти регистры.

"Непривилегированная часть" системы команд IA-64 определяет наиболее принципиальные особенности IA-64. Среди этих принципиальных особенностей спекулятивное выполнение команд и применение предикатов.

Все рассматриваемые команды можно подразделить на: команды работы со стеком регистров (например, alloc); целочисленные команды; команды сравнения и работы с предикатами; команды доступа в память; команды перехода; мультимедийные команды; команды пересылок между регистрами; "разные" (операции над строками и подсчет числа единиц в слове); команды работы с плавающей запятой.

Целочисленные команды IA-64 включают арифметические операции (add, sub и др.), логические операции (and, or, xor и др.), операции над битами и сдвиги, а также 32-разрядные операции. Большинство этих команд трехадресные, а их аргументы лежат в регистрах; однако встречается и литеральное представление аргументов. Имеются также модификации команд add и sub, которые являются четырехадресными: в них к сумме/разности регистров прибавляется/вычитается 1.

Отметим, что команда умножения целых чисел в регистрах GR отсутствует; для перемножения необходима пересылка целых в регистры FR и применение операции умножения, выполняемой в ФИУ вещественного типа. Некоторые специалисты считают это "наименее удачной" чертой системы команд IA-64.

Команды сравнения и работа с предикатами - это одна из принципиально новых особенностей IA-64 по сравнению с RISC-архитектурой. Приведем сначала несколько типичных примеров команд этой группы. Команда cmp сравнивает два регистра GR (или регистр GR и литерал) на одно из 10 возможных условий (больше, меньше или равно и т.п.). Команда tbit тестирует заданный бит GR. Команда fcmp сравнивает два числа с плавающей запятой. Однако результатом сравнения является не единственный код условия, что типично для обычных процессоров. Логический результат сравнения (1 - истина, 0 - ложь) записывается обычно в пару предикатных регистров (во второй пишется отрицание первого).

Эти значения предикатных регистров используются затем не только в командах условного перехода, как в обычных микропроцессорах. Почти все команды IA-64 выполнимы "под предикатом", т.е. могут выполняться или нет в зависимости от значения указанного в команде PR-регистра. Это позволяет во многих случаях избежать применения условных переходов, которые, как известно, отрицательно сказываются на производительности микропроцессоров. Вместо этого процессор c архитектурой IA-64, имеющий большое число ресурсов (в частности, регистров и ФИУ), может исполнить обе ветви программы.

Рассмотрим теперь команды доступа в память. Прежде всего, это команды загрузки регистров и записи из них в оперативную память. Команда ld загружает в GR 1-, 2-, 4- и 8-байтные целочисленные величины; аналогично ldf загружает в FR числа с плавающей запятой размером 4, 8, 10 байт, а также пары 4-байтных чисел. В этих командах можно указать также на тонкие особенности работы с оперативной памятью и КЭШем. Имеются и специальные команды работы с КЭШем.

Принципиальной является возможность кодирования указанных команд загрузки в специальных спекулятивных формах. Различают загрузку спекулятивную по управлению и спекулятивную по данным.

Спекулятивное по управлению выполнение означает возможность заранее выполнить команды, расположенные за командой условного перехода, до того, как будет известно, будет ли осуществляться этот условный переход на соответствующую ветвь программы. При наличии большого числа ресурсов процессора это позволяет заранее запускать на выполнение команды, которые начнут выполняться одновременно с уже начавшими выполняться другими командами (в других ФИУ). Однако позднее может выясниться, что эти спекулятивно выполненные команды оказались выполненными напрасно, так как переход на эту ветвь не произошел, и нужно произвести "откат".

Поскольку эти спекулятивно выполненные команды могут привести к прерыванию, в IA-64 предусмотрен механизм, позволяющий зафиксировать, что возникло прерывание, но само прерывание "отложить" до тех пор, пока не будет затребован опрос его наличия. Признак отложенного прерывания записывается в регистр результата (затем его можно опросить специальной командой chk.s). В дальнейшем признак отложенного прерывания последовательно "распространяется" на регистры результатов спекулятивных команд, в регистрах исходных данных которых взведен признак отложенного прерывания.

Все команды можно разделить на спекулятивно выполнимые и спекулятивно невыполнимые. Последние могут вызывать прерывания, которые не могут быть отложены. Обычные вычислительные команды, имеющие GR или FR в качестве регистров результата, - спекулятивные. Если же команда изменяет другие типы регистров, она не спекулятивная.

Кроме обычных не спекулятивных команд (ld, ldf...) в IA-64 имеются их спекулятивные модификации (ld.s, ldf.s...). Вычислительные команды в общем случае не вызывают прерываний (операции с плавающей запятой обрабатывают прерывания специальным образом), поэтому единственным способом сгенерировать признак отложенного прерывания являются команды спекулятивной загрузки. Другие команды его могут только "распространять".

В точке программы, где надо использовать результат спекулятивного выполнения, следует применять спекулятивную команду chk.s, проверяющую признак отложенного прерывания. Если оно имелось, chk.s передаст управление по указанному в ней адресу, по которому программист должен расположить коды обработки ситуации. Поскольку стало ясно, что спекулятивное выполнение команды действительно понадобилось, можно закодировать копию спекулятивно выполненного фрагмента программы, но уже с не спекулятивными командами загрузки.

Другой тип спекулятивного выполнения может иметь место, когда вслед за записью в память идет команда загрузки регистра, и невозможно заранее определить, не будут ли перекрываться в памяти используемые этими командами данные. В IA-64 имеются спекулятивные команды загрузки (ld.a, ldf.a...), которые называются "усовершенствованными" (advanced) командами загрузки. Аналогично взаимозависимости между командами по управлению, "расшиваемой" применением спекулятивных команд с "постфиксом" .s, продвинутые команды загрузки вместе с соответствующей командой проверки chk.a (аналог chk.s) позволяют исключить задержки выполнения при наличии взаимозависимости по данным.

Обратимся теперь к командам перехода. Адрес перехода выравнивается всегда на границу связки, т.е. управление передается на ее слот 0. Имеется команда перехода относительно счетчика команд, в которой явно кодируется 21-разрядное смещение. Эти переходы осуществимы в пределах +/-16 Мбайт относительно счетчика. В непрямых командах перехода адрес перехода задается в регистре BR.

Обычный условный переход br.cond, или просто br, использует значение кодируемого в команде предикатного регистра PR для определения истинности условия. Указав в команде PR0, в котором всегда лежит 1, можно получить безусловный переход. PR0 кодируется также в командах вызова процедур/возврата (br.call/br.ret). Имеется 5 типов команд перехода, применяемых для организации циклов. Команда br.cloop используется для организации циклов со счетчиком, в которых адрес перехода кодируется относительно IP. В команде используется регистр LC: если он не равен 0, его содержимое уменьшается на 1, и выполняется переход; если LC = 0, перехода не будет. Применение команд работы с циклами мы рассмотрим позже при обсуждении программно конвейеризованных циклов.

В 2003-2005 годахItanium® 2 лучшей в отрасли ЦП по производительности, по затратами и с более широким выбором конфигураций, чем у закрытых RISC-технологий.

Процессор Itanium® 2, созданный на основе открытых стандартов, является высокомасштабируемым, 64-разрядным решением и поддерживается 40 ведущими производителями аппаратных средств, более чем пятью операционными системами, включающими ОС Windows* Server 2003, HP-UX* и Linux*, и сотнями приложений и пакетов инструментальных средств. Кроме того, процессоры Itanium® 2 совместимы на уровне двоичного кода с существующим ПО для процессора Itanium, что обеспечивает защиту инвестиций.

Приложения для 32-разрядной архитектуры Intel® поддерживаются семейством процессоров Itanium, и эта поддержка будет улучшена после реализации технологии Intel® Architecture-32 Execution Layer. Itanium® 2 совместимы на уровне двоичного кода с существующим ПО для процессора Itanium. Микроархитектура процессора Itanium® 2 обеспечивает быстрый доступ к интегрированной кэш-памяти, высокую пропускную способность при обмене информацией между центральным процессором и системной памятью и обладает значительными вычислительными ресурсами, ускоряющими выполнение команд и повышающими общую производительность системы.

Intel 21 февраля 2004 года наконец-то официально сообщила о выпуске первых процессоров Pentium 4 для настольных систем с поддержкой 64-разрядных расширений Extended Memory 64 Technology (EMT 64).

Это решение лишь стало конкурентно способным по цене и «теплу» 64-х разрядным центральным процессорам AMD.