Регистры состояния и управления

В процессор включены два регистра (рис. 1), постоянно содержащие информацию о состоянии как самого процессора, так и программы, команды которой он в данный момент обрабатывает:

регистр-указатель команд EIP/IP;

регистр флагов EFLAGS/FLAGS.

С помощью этих регистров можно также ограниченным образом управлять состоянием процессора.

Регистр-указатель команд (Instruction Pointer register) EIP/IP имеет разрядность 32(16) бита и содержит смещение следующей подлежащей выполнению команды относительно содержимого регистра сегмента кода CS в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации регистра EIP/IP.

Разрядность регистра флагов (flag register) EFLAGS/FLAGS равна 32(16) битам. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть регистра EFLAGS/FLAGS полностью аналогична регистру FLAGS процессора i8086. На рис. 6 показано содержимое регистра EFLAGS.

Исходя из особенностей использования, флаги регистра EFLAGS/FLAGS можно разделить на три группы.

В первую группу флагов регистра EFLAGS/FLAGS входят 8 флагов состояния. Эти флаги могут изменяться после выполнения машинных команд. Флаги состояния регистра EFLAGS отражают особенности результата исполнения арифметических или логических операций. Это дает возможность анализировать состояние вычислительного процесса и реагировать на него с помощью команд условных переходов и вызовов подпрограмм.

Флаг переноса (carry flag) CF:

1 – арифметическая операция произвела перенос из старшего бита результата, старшим является 7-й, 15-й или 31-й бит в зависимости от размерности операнда;

0 – переноса не было.

Флаг четности (parity flag) PF:

1 – 8 младших разрядов (этот флаг только для 8 младших разрядов операнда любого размера) результата содержат четное число единиц;

0 – 8 младших разрядов результата содержат нечетное число единиц.

Вспомогательный флаг переноса (auxiliary carry flag) AF применяется только для команд, работающих с BCD-числами. Фиксирует факт заёма из младшей тетрады результата:

1 – в результате операции сложения был произведен перенос из разряда 3 в старший разряд или при вычитании был заем в разряд 3 младшей тетрады из значения в старшей тетраде;

0 – переносов и заемов в третий разряд (из третьего разряда) младшей тетрады результата не было.

Флаг нуля (zero flag) ZF;

1 - результат нулевой;

0 – результат ненулевой.

Флаг знака (sign flag) SF отражает состояние старшего бита результата (биты 7, 15 или 31 для 8-, 16- или 32-разрядных операндов соответственно):

1 – старший бит результата равен 1;

0 – старший бит результата равен 0.

Флаг переполнения (overflow flag) OF используется для фиксации факта потери значащего бита при арифметических операциях:

1 – в результате операции происходит перенос в старший знаковый бит результата или заем из старшего знакового бита результата (биты 7,15 или 31 для 8-, 16- или 32-разрядных операндов соответственно);

0 – в результате операции не происходит переноса в старший знаковый бит результата или заема из старшего знакового бита результата.

Уровень привилегированности, ввода-вывода (Input/Output privilege level) IOPL используется в защищенном режиме работы процессора для контроля доступа к командам ввода-вывода в зависимости от привилегированности задачи.

Флаг вложенности задачи (nested task) NT используется в защищенном режиме работы процессора для фиксации того факта, что одна задача вложена в другую.

Во вторую группу флагов (группа флагов управления) регистра EFLAGS/FLAGS входит всего один флаг направления (directory flag) DF. Он находится в десятом бите регистра EFLAGS и используется цепочечными командами. Значение флага DF определяет направление поэлементной обработки в этих операциях: от начала строки к концу (DF = 0) либо, наоборот, от конца строки к ее началу (DF =1). Для работы с флагом DF существуют специальные команды CLD (снять флаг DF) и STD (установить флаг DF), Применение этих команд позволяет привести флаг DF в соответствие с алгоритмом и обеспечить автоматическое увеличение или уменьшение счетчиков при выполнении операций со строками.

В третью группу флагов регистра EFLAGS/FLAGS входит 8 системных флагов, управляющих вводом-выводом, маскируемыми прерываниями, отладкой, переключением между задачами и режимом виртуального процессора 8086. Прикладным программам не рекомендуется модифицировать без необходимости эти флаги, так как в большинстве случаев это ведет к прерыванию работы программы. Далее перечислены системные флаги и их назначение.

Флаг трассировки (trace flag) TF предназначен для организации пошаговой работы процессора:

1 – процессор генерирует прерывание с номером 1 после выполнения каждой машинной команды (может использоваться при отладке программ, в частности отладчиками);

0 – обычная работа.

Флаг прерывания (interrupt enable flag) IF предназначен для разрешения или запрещения (маскирования) аппаратных прерываний (прерываний по входу INTR):

1 – аппаратные прерывания разрешены;

0 – аппаратные прерывания запрещены.

Флаг возобновления (resume flag) RF используется при обработке прерываний от регистров отладки.

Флаг режима виртуального процессора 8086 (virtual 8086 mode) VM является признаком работы процессора в режиме виртуального 8086:

1 – процессор работает в режиме виртуального процессора 8086;

0 – процессор работает в реальном или защищенном режиме.

Флаг контроля выравнивания (alignment check) AC предназначен для разрешения контроля выравнивания при обращениях к памяти. Используется совместно с битом AM в системном регистре CRO. К примеру, Pentium разрешает размещать команды и данные начиная с любого адреса. Если требуется контролировать выравнивание данных и команд по адресам, кратным 2 или 4, то установка данных битов приведет к тому, что все обращения по некратным адресам будут возбуждать исключительную ситуацию.

Флаг виртуального прерывания (virtual interrupt flag) VIF, появившийся в процессоре Pentium, при определенных условиях (одно из которых – работа процессора в v-режиме) является аналогом флага IF. Флаг VIF используется совместно с флагом VIP.

Флаг отложенного виртуального прерывания (virtual interrupt pending flag) VIP, появившийся в процессоре Pentium, устанавливается в 1 для индикации отложенного прерывания. Используется при работе в v-режиме совместно с флагом VIF.

Флаг идентификации (identification flag) ID используется для того, чтобы показать факт поддержки процессором инструкции CPUID. Если программа может установить или сбросить этот флаг, это означает, что данная модель процессора поддерживает инструкцию CPUID.

Архитектура сопроцессора

Аппаратная реализация сопроцессора интересно для программиста лишь в видимой для программ части. Как и в случае с основным процессором, интерес представляет программная модель сопроцессора. С точки зрения программиста, сопроцессор представляет собой совокупность регистров, каждый из которых имеет свое функциональное назначение (рис. 3).

Рис. 3. Программная модель сопроцессора

В программной модели сопроцессора можно выделить три группы регистров:

восемь регистров R0…R7 составляют основу программной модели сопроцессора — стек сопроцессора. Размерность каждого регистра — 80 битов. Такая организация характерна для устройств, специализирующихся на обработке вы числительных алгоритмов;

три служебных регистра:

регистр состояния сопроцессора SWR отражает информацию о текущем состоянии сопроцессора и содержит поля, позволяющие определить, какой регистр является текущей вершиной стека сопроцессора, какие исключения возникли после выполнения последней команды, каковы особенности выполнения последней команды и т. д.;

управляющий регистр сопроцессора CWR управляет режимами работы сопроцессора; с помощью полей в этом регистре можно регулировать точность выполнении численных вычислений, управлять округлением, маскировать исключения;

регистр слова тегов TWR используется для контроля за состоянием каждого из регистров R0.. .R7 (команды сопроцессора используют этот регистр, например, для того, чтобы определить возможность записи значений в указанные регистры);

два регистра указателей — данных DPR и команд IPR — предназначены для запоминания информации об адресе команды, вызвавшей исключительную ситуацию, и адресе ее операнда. Эти указатели используются при обработке исключительных ситуаций (но не для всех команд).

Все эти регистры являются программно доступными. Однако к одним из них доступ получить довольно легко, для этого в системе команд сопроцессора существуют специальные команды, а к другим его получить сложнее, так как специальных команд для этого нет, поэтому необходимо выполнять дополнительные действия.

Общая логика работы сопроцессора заключается в следующем.

Регистровый стек сопроцессора организован по принципу кольца. Это означает, что среди всех регистров, составляющих стек, нет такого, который является вершиной стека. Напротив, все регистры стека с функциональной точки зрения абсолютно равноправны. Но, как известно, в стеке всегда должна быть вершина. И она действительно есть, но является плавающей. Контроль текущей вершины осуществляется аппаратно с помощью трехразрядного поля ТОР регистра SWR (рис. 4). В поле ТОР фиксируется номер регистра стека 0...7 (R0.. .R7), являющегося текущей вершиной стека.

Рис. 4.

Команды сопроцессора не оперируют физическими номерами регистров стека R0...R7. Вместо этого они используют логические номера этих регистров ST(0)... ST(7). С помощью логических номеров реализуется относительная адресация регистров стека сопроцессора. Если текущей вершиной стека является физический регистр R0, то после записи очередного значения в стек сопроцессора его текущей вершиной станет физический регистр R7 (рис. 5, а).

Рис. 5.

На рис. 5, б показан пример, когда текущей вершиной до записи в стек является физический регистр R3, а после записи в стек текущей вершиной становится физический регистр стека R2. То есть по мере записи в стек указатель его вершины движется по направлению к младшим номерам физических регистров (уменьшается на единицу). Что касается логических номеров регистров стека ST(0)...ST(7), то, как следует из рисунка, они «плавают» вместе с изменением текущей вершины стека. Таким образом, реализуется принцип кольца.

Процессор и сопроцессор, являясь двумя самостоятельными вычислительными устройствами могут работать параллельно. Но этот параллелизм касается только их внутренней работы над исполнением очередной команды. Оба процессора подключены к общей системной шине и имеют доступ к одинаковой информации. Инициирует процесс выборки очередной команды всегда основной процессор. После выборки команда попадает одновременно в оба процессора. Любая команда сопроцессора имеет код операции, первые 5 битов которого имеют значение 11011. Когда код операции начинается этими битами, то основной процессор по дальнейшему содержимому кода операции выясняет, требует ли данная команда обращения к памяти. Если это так, то основной процессор формирует физический адрес операнда и обращается к памяти, после чего содержимое ячейки памяти выставляется на шину данных. Если обращение к памяти не требуется, то основной процессор заканчивает работу над данной командой (не делая попытки ее исполнения) и приступает к декодированию следующей команды из текущего входного командного потока. Что же касается сопроцессора, то выбранная команда попадает к нему и к основному процессору одновременно. Сопроцессор, определив по первым пяти битам, что очередная команда принадлежит его системе команд, начинает ее исполнение. Если команда требует операнда в памяти, то сопроцессор обращается к шине данных за чтением содержимого ячейки памяти, которое к этому моменту должно быть предоставлено основным процессором. Из этой схемы и взаимодействия следует, что в определенных случаях необходимо согласовывать работу обоих устройств. Синхронизация работы сопроцессора и процессора производится командами WAIT/FWAIT.

Регистр состояния SWR.

Ранее было отмечено, что регистр SWR отражает текущее состояние сопроцессора после выполнения последней команды. Далее перечислены ноля, из которых структурно состоит регистр SWR:

шесть флагов исключительных ситуаций;

бит SF — ошибка работы стека сопроцессора. Бит устанавливается в единицу, если возникает одна из трех исключительных ситуаций — РЕ, UE, IE. В частности, его установка информирует о попытке записи в заполненный стек или, напротив, попытке чтения из пустого стека. После анализа этого бита, его нужно снова установить в ноль имеете с битами РЕ, UЕ или IЕ (если они не были установлены);

бит ES сигнализирует о суммарной ошибке в работе сопроцессора. Бит устанавливается в единицу, если возникает любая из шести исключительных ситуаций, о которых будет рассказано далее;

четыре бита С0...С3 представляют собой код условия. Эти биты отражают результат выполнения последней команды сопроцессора;

трехразрядное поле ТОР содержит указатель регистра текущей вершины стека.

Почти половину регистра SWR занимают биты (флаги) регистрации исключительных ситуаций. Исключительные ситуации – особый тип прерываний, с помощью которых процессор информирует программу о некоторых особенностях ее реального исполнения. Сопроцессор также обладает способностью возбуждения подобных прерываний при возникновении определенных ситуаций (не обязательно ошибочных). Все возможные исключения сведены к шести типам, каждому из которых соответствует один бит в регистре SWR. Программисту совсем не обязательно писать обработчик для реакции на ситуацию, приведшую к некоторому исключению. Сопроцессор умеет самостоятельно реагировать на многие из них. Это так называемая обработка исключений по умолчанию. Для того чтобы запретить сопроцессору обработку определенного типа исключения по умолчанию, необходимо это исключение замаскировать. Такое действие выполняется путем установки в единицу нужного бита в управляющем регистре сопроцессора CWR. Типы исключений, фиксируемые с помощью регистра SWR:

IE — недействительная операция;

DE — денормализованный операнд;

ZE — ошибка деления на нуль;

OE — ошибка переполнения (возникает в случае выхода порядка числа за максимально допустимый диапазон);

UE — ошибка антипереполнения (возникает, когда результат слишком мал);

PE — ошибка точности (устанавливается, когда сопроцессору приходится округлять результат из-за того, что его точное представление невозможно).

При возникновении любого из этих шести типов исключений устанавливается в единицу соответствующий бит в регистре SWR вне зависимости от того, было ли замаскировано это исключение в регистре CWR или нет.

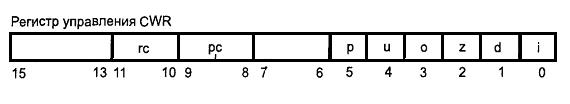

Регистр управления CWR.

Регистр управления сопроцессором CWR определяет особенности обработки численных данных (рис. 6). Он состоит:

из шести масок исключений;

поля управления точностью РС;

поля управления округлением RС:

Рис. 6.

Шесть масок предназначены для маскирования исключительных ситуаций возникновение которых фиксируется с помощью шести битов регистра SWR. Если какие-то биты исключений в регистре CWR установлены и единицу, это означает, что соответствующие исключения будут обрабатываться самим сопроцессором. Если для какого-либо исключения в соответствующем бите масок исключений регистра CWR содержится нулевое значение, то при возникновении исключение этого типа будет возбуждено прерывание 16 (10h). Операционная система должна содержать (или программист должен написать) обработчик этого прерывания.

Поле управления точностью РС предназначено для выбора длины мантиссы. Возможные значения в этом поле означают:

РС = 00 — длина мантиссы 24 бита;

РС = 10 — длина мантиссы 53 бита;

РС = 11— длина мантиссы 64 бита.

По умолчанию устанавливается значение поля РС = 11.

Поле RC позволяет управлять процессом округления чисел в ходе работы сопроцессора. Необходимость округления может возникнуть в ситуации, когда после выполнения очередной команды сопроцессора получается непредставимый результат, например периодическая дробь 3,333... Установив одно из значений в поле RC, можно выполнить округление в необходимую сторону.

Регистр тегов TWR.

Регистр тегов TWR представляет собой совокупность двухразрядных полей. Каждое двухразрядное поле соответствует определенному физическому регистру стека и характеризует его текущее состояние. Изменение состояния любого регистра стека отражается на содержимом соответствующего этому регистру поля регистра тега. Возможны следующие значения в полях регистра тега:

00 — регистр стека сопроцессора занят допустимым ненулевым значением;

01 — регистр стека сопроцессора содержит нулевое значение;

10 — регистр стека сопроцессора содержит одно из специальных численных значений, за исключением нуля;

11 — регистр пуст, и в него можно производить запись (нужно отметить, что это значение в одном из двухразрядных полей регистра тегов не означает, что все биты соответствующего регистра стека обязательно нулевые).

Для работы с приведенной структурой регистров процессора и сопроцессора используются команды Assembler (см. справочное пособие).

II. Перечень вариантов заданий к лабораторной работе №1.

1. Переведите числа в десятичную систему, а затем проверьте результаты, выполнив обратные переводы:

| а) 10110112; | е) 5178; | л) 1F16; |

| б) 101101112; | ж) 10108; | м) ABC16; |

| в) 0111000012; | з) 12348; | н) 101016; |

| г) 0,10001102; | и) 0,348; | о) 0,А416; |

| д) 110100,112; | к) 123,418; | п) 1DE,C816. |

2. Переведите числа из десятичной системы в двоичную, восьмеричную и шестнадцатеричную, а затем проверьте результаты, выполнив обратные переводы:

а) 12510; б) 22910; в) 8810; г) 37,2510; д) 206,12510.

3. Переведите числа из двоичной системы в восьмеричную и шестнадцатеричную, а затем проверьте результаты, выполнив обратные переводы:

| а) 1001111110111,01112; | г) 1011110011100,112; |

| б) 1110101011,10111012; | д) 10111,11111011112; |

| в) 10111001,1011001112; | е) 1100010101,110012. |

4. Переведите в двоичную и восьмеричную системы шестнадцатеричные числа:

а) 2СE16; б) 9F4016; в) ABCDE16; г) 1010,10116; д) 1ABC,9D16.

5. Для десятичных чисел 47 и 79 выполните цепочку переводов из одной системы счисления в другую:

a)

b)

d)

6. Расположите следующие числа в порядке возрастания:

а) 748, 1100102, 7010, 3816;

б) 6E16, 1428, 11010012, 10010;

в) 7778, 1011111112, 2FF16, 50010;

г) 10010, 11000002, 6016, 1418.

7. Запишите числа в прямом коде (формат 1 байт):

а) 31; б) -63; в) 65; г) -128.

8. Запишите числа в обратном и дополнительном кодах (формат 1 байт):

а) -9; б) -15; в) -127; г) -128.

9. Найдите десятичные представления чисел, записанных в дополнительном коде:

а) 1 1111000; б) 1 0011011; в) 1 1101001; г) 1 0000000.

10. Найдите десятичные представления чисел, записанных в обратном коде:

а) 1 1101000; б) 1 0011111; в) 1 0101011; г) 1 0000000.

III. Порядок выполнения, оформления отчета и защиты лабораторной работы

Лабораторная работа выполняется студентами по индивидуальному заданию (варианту). Изменение варианта работы производится с разрешения преподавателя.

Результатом лабораторной работы является программа. Программа разрабатывается на языке Assembler. При этом каждое действие, происходящее в программе, комментируется его описанием. При работе над программой разрешается пользоваться справочной литературой языка программирования.

Отчет по работе оформляется на листах формата А4 в соответствии с требованиями СТП. В содержание отчета в обязательном порядке должны войти следующие разделы:

1. Теоретическая часть – содержит теоретическое описание решение задачи, строго соответствующее полученному варианту. Например, вариант содержит задание: перевести десятичное число в двоичную систему счисления. Тогда в теоретическом описании должна быть представлена методика перевода десятичных чисел в двоичную систему счисления.

2. Описание программы – содержит описание порядка работы над программой и порядок работы самой программы. В описании работы программы обязательно включаются обоснования используемых приемов программирования, действия программных операторов, назначения и вызовы процедур и функций, правила передачи управления и т.д.

3. Листинг программы (или диск с исходным кодом программы) – содержит полную работающую версию программы с комментариями.

При защите полученных результатов программа демонстрируется.

IV. Материальное обеспечение.

Для выполнения лабораторной работы используются компьютеры класса Р-III или выше с установленным программным обеспечением: ОС – MS Windows, пакет разработки программ на Assembler TASM.

V. Литература.

1. Юров В.И. Assembler. Учебник для вузов. 2-е изд. – СПб: Питер, 2004. – 637с.

2. Assembler: практикум / В. Юров – СПб: Питер, 2003. – 400с.