Особенности risc и cisc архитектуры в компьютерных системах

Левшин С.А.

ОРГАНИЗАЦИЯ ЭВМ

Новочеркасск

ЮРГПУ (НПИ) им. М.И. Платова

УДК 004.415.2 (075.8)

ББК 32.973 – 02я73

Л 38

Научный редактор кандидат технических наук, доцент Гринченков Д.В.

Левшин С.А.

Т «Организация ЭВМ». Юж.-Рос. гос. политехн. ун-т. (НПИ) - Новочеркасск: ЮРГПУ (НПИ) им. М.И. Платова, 2013. - 93 с.

Учебное пособие содержит описание микроархитектуры наиболее известных микропроцессоров. Рассматривается варианты построения многопроцессорных систем и области их применения.

Ó Южно-Российский государственный

политехнический университет (НПИ)

имени М.И. Платова

Ó Левшин С.А., 2015

СОДЕРЖАНИЕ

| стр. | ||

| ВВЕДЕНИЕ……………………………………………………….. | ||

| ОСОБЕННОСТИ RISC и CISK АРХИТЕКТУРЫ В КОМПЬЮТЕРНЫХ СИСТЕМАХ | ||

| ОБЗОР МИКРОПРОЦЕССОРОВ с CISK-АРХИТЕКТУРОЙ | ||

| 2.1 | Микроархитектура микропроцессора Intel Pentium (P5) | |

| 2.2 | Микроархитектура микропроцессора Intel Pentium Pro (P6) | |

| 2.3 | Микроархитектура микропроцессора Intel Pentium 4 | |

| 2.4 | Микроархитектура микропроцессора Intel Atom | |

| 2.5 | Микроархитектура микропроцессора AMD Opteron (K8) | |

| ОБЗОР МИКРОПРОЦЕССОРОВ с RISK-АРХИТЕКТУРОЙ | ||

| 3.1 | Микроархитектура микропроцессора IBM Power 4 | |

| 3.2 | Особенности микроархитектуры микропроцессора IBM Power 5 | 52 |

| 3.3 | Особенности микроархитектуры микропроцессора IBM Power 6 | 58 |

| ЭВОЛЮЦИЯ ОПЕРАТИВНОЙ ПАМЯТИ | ||

| 4.1 | Расчет времени обращения микропроцессора к ячейкам памяти | |

| АРХИТЕКТУРА КЭШ-памяти | ||

| АРХИТЕКТУРА МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | ||

| 6.1 | Архитектура SMP-систем | |

| 6.2 | Архитектура MPP-систем | |

| 6.3 | Гибридная архитектура (NUMA) | |

| 6.4 | Кластерная архитектура | |

| 6.5 | Модели памяти многопроцессорных вычислительных систем | |

| 6.6 | Компьютерные системы с архитектурой ccNUMA | |

| 6.7 | Компьютерные системы с архитектурой COMA | |

| 6.8 | Технология Hyper-Threading в компьютерных системах | |

| 6.8.1 | Принцип действия | |

| 6.8.2 | Использование ресурсов | |

| 6.8.3 | Детали микроархитектуры | |

| 6.8.4 | Механизм выборки и доставки | |

| 6.8.5 | Rapid Execution Engine | |

| 6.8.6 | Встроенная кэш-память | |

| 6.8.7 | Блок переупорядочения и изъятия | |

| 6.8.8 | Системная шина | |

| 6.8.9 | Hyper-Threading и серверные платформы | |

| 6.8.10 | Hyper-Threading и приложения |

ВВЕДЕНИЕ

Современные компьютерные системы имеют многоуровневую структуру. Уровень 0 – это аппаратное обеспечение на цифровом логическом уровне. Объекты этого уровня называются вентилями, вычисляющими простые функции, такие как И или ИЛИ. Уровень 1 называется уровнем микроархитектуры. На этом уровне находятся совокупности элементов, обеспечивающих выполнение арифметических, логических и т.д. операций. Уровень 2 называется уровнем архитектуры набора команд, обеспечивающим выполнение системы команд микропрограммой-интерпретатором или аппаратным обеспечением. Уровни 3, 4 и 5 являются соответственно уровнями операционной системы, ассемблера и языка прикладных программистов.

В данном курсе будет рассмотрена компьютерная система как совокупность взаимосвязанных и взаимодействующих процессоров или компьютеров, периферийного оборудования и программного обеспечения, предназначенную для подготовки и решения задач пользователей. При этом будут рассмотрены уровни микроархитектуры для микропроцессоров и архитектуры для компьютерной системы в целом.

ОБЗОР МИКРОПРОЦЕССОРОВ с RISK-АРХИТЕКТУРОЙ

ЭВОЛЮЦИЯ ОПЕРАТИВНОЙ ПАМЯТИ

Все процессоры, начиная с i386 большую часть времени тратят не на вычисления, а на операции обмена медленной оперативной памятью (ОП). Все ВС имеют многоуровневую архитектуру памяти: емкую, дешевую, но медленную основную память и сравнительно небольшой объем быстрой, но дорогой КЭШ-памяти. Основная ОП строится на микросхеме DRAM (динамическая память с произвольным доступом).

Физически DRAM представляет собой массив обыкновенных конденсаторов, наличие заряда соответствует логической 1, а отсутствие – 0. Так как конденсаторы, как элементы достаточно дешевые, поэтому и память относительно не дорогая.

Конденсаторы в силу своей емкости обладают инертностью, что не позволяет мгновенно считать-записать состояние конденсатора.

Память на быстродействующих триггерах называется SRAM (статическая ОЗУ). Ее быстродействие намного выше и единственный недостаток – это стоимость, т. е. 1 триггер – это одна ячейка, каждый триггер – это 6 транзисторов, т. о. 1Мбайт памяти требует 56000 транзисторов.

Первоначально все модули памяти были асинхронными, так как от них не требовали высокой производительности. При асинхронной передаче гарантируется, что определенная операция будет закончена за фиксированный промежуток времени, например 60 нс. Работа асинхронной памяти не привязана к тактовой частоте системной шины, и данные появляются на этой шине в произвольные моменты времени. С системной шины данные считываются контролером, который синхронизирован тактовой частотой, и если данные появляются в ближайший момент за фронтом тактового импульса, то они будут считаны только с началом следующего тактового импульса, т.е. возникает задержка с обработкой данных. Осуществляя специальные режимы доступа, проектировщики памяти смогли улучшить работу динамической памяти с рабочей частотой 4,77 МГц. В новом виде памяти FPM применялся режим постраничной адресации (fast page mode), и при этом удалось увеличить тактовую частоту до 40 МГц.

Следующим шагом на пути улучшения памяти был переход к стандарту EDO (Extended data output), который характеризовался увеличенным по сравнению с FPM временем хранения данных на выходе микросхемы памяти. В сочетании с пакетным режимом передачи данных (Burst Mode) эта память обеспечила хорошую производительность и с успехом применяется и сейчас в системах, не требующих более 66 МГц системной шины.

Как только стало очевидным, что потребуются шины, работающие быстрее, чем 66 МГц, разработчикам DRAM потребовалось найти способ преодоления существенных проблем задержек, которые все еще существовали. Напомним, что быстродействие асинхронных типов DRAM характеризуется временем цикла обращения, т.е. минимальным периодом, с которым можно выполнить циклическое обращение по произвольным адресам. Когда говорят, что модуль 60 нс, именно это время и имеется в виду. Процессор, работающий с асинхронной памятью, вынужден простаивать в ожидании завершения внутренних действий микросхем DRAM, для чего обычно требуется 60 нс.

При синхронной работе с памятью DRAM выдает информацию на системную шину под контролем (с тактами) системного генератора. При этом управление памятью усложняется, так как приходится вводить дополнительные «защелки», которые хранят адреса, данные и управляющие сигналы, в то время как процессор, передав их в память, продолжает работать с другими устройствами. После определенного числа тактовых циклов, количество которых считает специальный счетчик, данные становятся доступными и процессор может получить их с системной шины. При этом для описания быстродействия памяти вместо продолжительности цикла доступа стали применять минимально допустимый период тактовой частоты. Так, если говорят, что модуль 10 нс, это означает, что он тактируется 100 МГц.

Еще одним преимуществом синхронных модулей памяти является то, что именно частота системного генератора является характеристикой любого применяемого в системе модуля. При этом не нужны делители или умножители частоты (как в процессорах), нет необходимости в расчете времени подачи «стробов». Запись информации в модуль также упрощается, так как адреса, данные и управляющие сигналы «защелкиваются» тактовым генератором без вмешательства процессора, который ранее был вынужден контролировать синхронизацию хранения данных в памяти и запись в память. То же самое относится и к процессу считывания данных.

На частотах до 83 МГц не было никакой реальной причины переходить с EDO на SDRAM. Цена SDRAM была значительно выше, а производительность возрастала незначительно. С появлением системной шины 100 МГц все изменилось. EDO DRAM уже не могла устойчиво работать на данной частоте, а производительность SDRAM на частоте 100 МГц уже была значительно выше.

SDRAM разрабатывался, когда считалось, что этот стандарт памяти разрешит многие проблемы производительности, однако быстро стало очевидно, что практическая выгода небольшая, вместе с тем появилось множество дополнительных проблем с совместимостью. Первые SDRAM модули содержали только два входа синхронизирующих импульсов, но вскоре стало понятно, что этого недостаточно. Пришлось создавать две различные модульные конструкции с двумя и четырьмя тактовыми входами. В каждом случае их применения необходимо было знать, какая же из них требуется для вашей материнской платы. Были и аппаратные неполадки с парами SDRAM от разных производителей у чипсетов I430TX и SIS5571. Появившийся чипсет I430TX был улучшен, а на модули памяти стали устанавливать SРD-чип, который позволял считывать всю необходимую информацию с модуля SDRAM при автоконфигурации системы.

Когда компания Intel готовилась к переходу на системную шину 100 МГц и вела разработки революционного чипсета I440BX, стало ясно, что большинство SDRAM-модулей, производившихся в то время, не будут должным образом функционировать на частотах системной шины более чем 83 МГц. Чтобы каким-то образом упорядочить рынок памяти, компанией Intel была введена спецификация PC100 как техническое руководство производителям модулей памяти, которые должны правильно функционировать с чипсетом I440BX. После выхода спецификации достаточно долго оставалось непонимание того, из чего же фактически состоит «настоящий» модуль PC100. Было достаточно много случаев, когда модули, предлагаемые как PC100, работали неустойчиво на системной шине 100 МГц. Для оценки скоростных характеристик модулей SDRAM мало скоростных характеристик чипов, из которых они изготовлены, так как большое значение имеют и другие параметры.

Чипы SDRAM официально оцениваются в мегагерцах (МГц), а не в наносекундах (нс), так что имеется общий знаменатель между скоростью шины и скоростью чипа. Эту скорость определяют путем деления 1 секунды (1 млрд. нс) на выходную скорость чипа. Например, 100 МГц SDRAM-чип оценивается как 10 нс. Это оценка в наносекундах не является мерой той же самой синхронизации, как асинхронного чипа DRAM. Хотя SDRAM внутри содержит DRAM, работающую таким же образом, как в EDO, принцип управления модулем SDRAM совершенно другой и улучшение производительности модуля достигнуто путем «скрытия» внутренней работы DRAM специальными методами.

Основные особенностями микросхем SDRAM является синхронизация всех операций с тактовой частотой системной шины и процессора. SDRAM-модуль разделен на два или более банков. Такое решение позволяет иметь одновременно две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), что позволяет исключить задержки, связанные с регенерацией и устранением фазы восстановления памяти. Этим обеспечивается создание непрерывного потока данных.

Конвейерная обработка данных позволяет производить обращение по новому адресу столбца ячейки памяти на каждом тактовом цикле. Микросхема SDRAM имеет счетчик потока, который используется для наращивания адресов столбцов ячеек памяти с целью обеспечения очень быстрого доступа к ним.

На чипе памяти размещен регистр режимов, который применяется для настройки основных параметров микросхемы, в том числе длины и типа потока (с последовательной выборкой или чередованием).

SDRAM позволяет устанавливать задержку вывода данных, которые определяется числом тактовых импульсов между моментом получения адреса столбца и выводом данных. Значение этого параметра может быть 2 или 3 (латентность).

В настоящее время основным типом памяти является DDR SDRAM. Передача данных такой памяти ведется по обоим фронтам тактирующего сигнала, что дает результирующую пиковую пропускную способность, вдвое превышающую для микросхем SDRAM. DDR SDRAM имеет маркировку означающую пиковую пропускную способность в Мб/с (PC-1600, PC-2100)

DDR II SDRAM является развитием памяти типа DDR SDRAM и имеет результирующую пиковую пропускную способность, вдвое превышающую для микросхем DDR SDRAM.

Память в стандарте RIMM SDRAM работает с результирующей частотой 800 МГц. и использует 16 битную мультиплексируемую шину, что обеспечивает высокую скорость работы в приложениях требующих потоковую передачу данных, но с другой стороны увеличение стоимости как самих модулей, так и предназначенных для них материнских плат.

АРХИТЕКТУРА КЭШ-ПАМЯТИ

Существует понятие КЭШ-попадания, это если нужные данные оказались в КЭШ-памяти, и КЭШ-промах – если они там отсутствуют. При отсутствии данных, необходимо из ОП загрузить следующий блок данных.

Поиск блока данных для замены в КЭШ-памяти называется стратегией замещения. Можно выбрать блок, к которому реже всего обращаются (частотный анализ), можно выбрать по дате последнего обращения, можно по дате взятия из ОП, вернув те данные, которые были получены раньше всех, либо просто выбрать блок случайным образом.

Эффективность работы КЭШ-памяти в значительной мере зависит от интеллектуальности алгоритма замещения. Как правило, используется стратегия выбора по дате последнего обращения. Она относительно проста в реализации, но менее эффективна, чем частотная стратегия так как, современная DRAM память оптимизирована под 32 байтовые циклы чтения. Для этого КЭШ-память разбита на 32 байтовые блоки, называемые КЭШ-линейками или КЭШ-строками.

Каждая КЭШ-строка полностью заполняется за 1 цикл чтения и всегда заполняется или выгружается целиком, даже если процессор обращается к одному байту памяти, КЭШ-контроллер инициирует полный цикл обращения к основной памяти и запрашивает весь 32 байтный блок.

Так как объем КЭШ-памяти значительно меньше объема кэшируемой им оперативной памяти, каждой ячейке КЭШа соответствует множество ячеек кэшируемой памяти. Следовательно, приходится сохранять не только содержимое кэшируемой ячейки, но и ее адрес. Для этой цели каждая КЭШ-линейка имеет специальное поле, называемое тегом. В теге хранится адрес одного байта КЭШ-линейки, называемый базовым адресом. Разрядность тегов определяет объем кэшируемой памяти и если разрядность недостаточна, то часть памяти не сможет кэшироваться.

Рис.20. Архитектура КЭШ-памяти: 1- кэш прямого отображения; 2- полностью ассоциативный кэш; 3- множественно ассоциативный кэш

В КЭШ-памяти прямого отображения одна конкретная ячейка КЭШа соответствует нескольким конкретным ячейкам ОП. Это означает, что когда МП обращается за определенными данными, КЭШ должен найти эту информацию у себя в конкретной одной ячейке. КЭШ этого типа имеет следующий недостаток: так как несколько блоков ОП отображаются на один и тот же блок КЭШа в случае обращения программы за этими данными приходится постоянно перезаполнять КЭШ с доступом к ОП.

В полностью ассоциативной КЭШ-памяти данные блоков ОП могут размещаться в любых свободных блоках КЭШа. Преимущество такого подхода в том, что КЭШ, как правило, содержит информацию, к которой обращалась программа в самое последнее время. Недостаток в том, что поиск информации происходит медленно.

Множественно ассоциативная КЭШ-память сочетает в себе элементы двух предыдущих архитектур. Он делится на 2, 4 или 8 множеств. Эти множества имеют по много ячеек, в каждой из которых может размещаться блок данных. Каждый блок ОП может отображаться на любом из этих множеств. Однако, будет находиться только в одном конкретном месте в каждом множестве. Таким образом, достигается уменьшение времени поиска, причем становится менее вероятным, что часто используемые данные будут накладываться друг на друга.

Информация, содержащаяся в КЭШ-памяти, часто обновляется процессором. КЭШ-память транслирует подобные изменения в основную память, используя один из двух основных алгоритмов: сквозной или обратной записью.

В случае КЭШ-памяти со сквозной записью каждый раз, когда МП будет направлять измененные данные в КЭШ, контроллер КЭШа будет обновлять эти данные как в самом КЭше, так и в основной памяти, причем одновременно.

В случае КЭШ-памяти с обратной записью, измененный блок будет хранится в самом КЭШе, однако его обновление в основной памяти будет происходить только при определенных обстоятельствах:

1. когда необходимо будет записывать весь блок данных в связи с необходимостью размещения более нового блока вместо него;

2. когда другое устройство системы пытается произвести доступ к этому блоку данных в основной памяти;

3. когда контроллер устанавливает, что данные слишком долго ждут своего обновления.

Архитектура SMP-систем

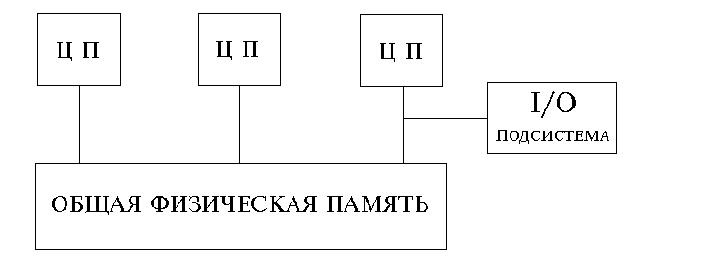

SMP архитектура (symmetric multiprocessing) - cимметричная многопроцессорная архитектура. Главной особенностью систем с архитектурой SMP является наличие общей физической памяти, разделяемой всеми процессорами

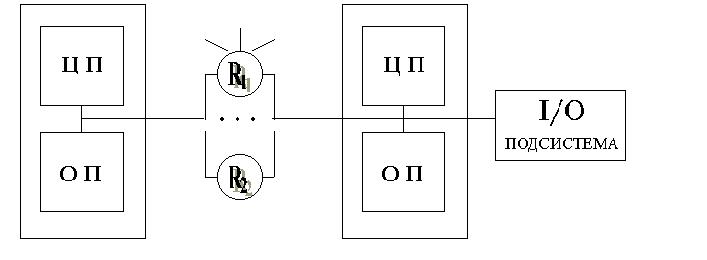

Рис.21. Упрощенная структура SMP-системы

Память является способом передачи сообщений между процессорами, при этом все вычислительные устройства при обращении к ней имеют равные права и одну и ту же адресацию для всех ячеек памяти. Поэтому SMP архитектура называется симметричной. Последнее обстоятельство позволяет очень эффективно обмениваться данными с другими вычислительными устройствами. SMP-система строится на основе высоко скоростной системной шины (SGI PowerPath, Sun Gigaplane, DEC TurboLaser), к слотам которой подключаются функциональные блоки трех типов: процессоры (ЦП), операционная система (ОП) и подсистема ввода/вывода (I/O). Для подсоединения к модулям I/O используются уже более медленные шины (PCI, VME64). Наиболее известными SMP-системами являются машины серий SGI Power Chalenge, DEC Alpha Server, Cray T3D. Вся система работает под управлением единой ОС (обычно UNIX-подобной). ОС автоматически (в процессе работы) распределяет процессы по процессорам, но иногда возможна и явная привязка.

Основные преимущества SMP-систем:

- простота и универсальность для программирования. Архитектура SMP не накладывает ограничений на модель программирования, используемую при создании приложения: обычно используется модель параллельных ветвей, когда все процессоры работают абсолютно независимо друг от друга, - однако, можно реализовать и модели, использующие межпроцессорный обмен. Использование общей памяти увеличивает скорость такого обмена, пользователь также имеет доступ сразу ко всему объему памяти. Для SMP-систем существуют сравнительно эффективные средства автоматического распараллеливания.

- легкость в эксплуатации. Как правило, SMP-системы используют систему охлаждения, основанную на воздушном кондиционировании, что облегчает их техническое обслуживание.

- относительно невысокая цена.

Все процессоры SMP-системы имеют одинаковый доступ к вычислительным ресурсам. Поскольку процессоры одновременно работают с данными, хранящимися в единой памяти, в SMP-архитектурах обязательно должен быть механизм, поддержки когерентности данных. Когерентность данных означает, что в любой момент времени для каждого элемента данных во всей памяти узла существует только одно его значение несмотря на то, что одновременно могут существовать несколько копий элемента данных, расположенных в разных видах памяти и обрабатываемых разными процессорами. Механизм когерентности должен следить за тем, чтобы операции с одним и тем же элементом данных выполнялись на разных процессорах последовательно, удаляя, в частности, устаревшие копии. В современных SMP-архитектурах когерентность реализуется аппаратными средствами.

Механизм когерентности является критичным для эффективной параллельной работы SMP-системы и должен иметь малое время задержки. До сегодняшнего дня самые крупные SMP-системы содержали максимум 32 процессора, что объяснялось требованием малых задержек когерентных связей, приводящим к архитектуре с одной объединительной платой, а это физически ограничивает возможное число подсоединенных процессоров и плат памяти. Поэтому для дальнейшего увеличения числа процессоров приходится вместо аппаратно реализованной техники когерентности применять более медленную программную реализацию, что очень существенно сказывается на программируемости систем и их производительности.

SMP-системы очень удобны для разработчиков приложений: операционная система почти автоматически масштабирует приложения, давая им возможность использовать наращиваемые ресурсы. Само приложение не должно меняться при добавлении процессоров и не обязано следить за тем, на каких ЦП оно работает. Временная задержка доступа от любого ЦП до всех частей памяти и системы ввода-вывода одна и та же. Разработчик оперирует с однородным адресным пространством. Все это приводит к тому, что SMP-архитектуры разных производителей выглядят в основном одинаково: упрощается переносимость программного обеспечения между SMP-системами. Переносимость программ - одно из основных достоинств SMP-платформ.

Типичные SMP-архитектуры в качестве аппаратной реализации механизма поддержки когерентности используют шину слежения (snoopy bus). Каждый процессор имеет свой собственный локальный кэш, где он хранит копию небольшой части основной памяти, доступ к которой наиболее вероятен. Для того чтобы все кэши оставались когерентными, каждый процессор "подглядывает" за шиной, осуществляя поиск тех операций считывания и записи между другими процессорами и основной памятью, которые влияют на содержимое их собственных кэшей. Если процессор "В" запрашивает ту часть памяти, которая обрабатывается процессором "А", то процессор "А" перехватывает этот запрос и помещает свои значения области памяти на шину, где "В" их считывает. Когда процессор "А" записывает измененное значение обратно из своего кэша в память, то все другие процессоры видят, как эта запись проходит по шине и удаляют устаревшие значения из своих кэшей.

Архитектура MPP-систем

MPP архитектура (massive parallel processing) - массивно-параллельная архитектура. Главная особенность такой архитектуры состоит в том, что память физически разделена. В этом случае система строится из отдельных модулей, содержащих процессор, локальный банк операционной памяти (ОП), два коммуникационных процессора (рутера) или сетевой адаптер, иногда - жесткие диски и/или другие устройства ввода/вывода. Один рутер используется для передачи команд, другой - для передачи данных. По сути, такие модули представляют собой полнофункциональные компьютеры. (см. рис.). Доступ к банку ОП из данного модуля имеет только процессоры (ЦП) из этого же модуля. Модули соединяются специальными коммуникационными каналами. Пользователь может определить логический номер процессора, к которому он подключен, и организовать обмен сообщениями с другими процессорами. Используются два варианта работы операционной системы (ОС) на машинах MPP архитектуры. В одном, полноценная операционная система (ОС) работает только на управляющей машине (front-end), на каждом отдельном модуле работает сильно урезанный вариант ОС, обеспечивающий работу только расположенной в нем ветви параллельного приложения. Во втором варианте, на каждом модуле работает полноценная UNIX-подобная ОС, устанавливаемая отдельно на каждом модуле.

Взаимосвязи между узлами (и между копиями ОС, принадлежащими каждому узлу) не требуют аппаратно поддерживаемой когерентности, так как каждый узел имеет собственную ОС и, следовательно, свое уникальное адресное пространство физической памяти. Когерентность реализуется программными средствами, с использованием техники передачи сообщений.

Задержки, которые присущи программной поддержке когерентности на основе сообщений, обычно в сотни и тысячи раз больше, чем те, которые получаются в системах с аппаратными средствами. С другой стороны, их реализация значительно менее дорогая. В некотором смысле в МРР-узлах задержкой приходится жертвовать, чтобы подсоединить большее число процессоров - сотни и даже тысячи узлов.

Известно, что производительность МРР-систем весьма чувствительна к задержкам, определяемым программной реализацией протоколов и аппаратной реализацией среды передачи сообщений (будь то коммутатор, или сеть). Вообще говоря, настройка производительности МРР-систем включает распределение данных для того, чтобы минимизировать трафик между узлами. Приложения, которые имеют естественное разбиение данных, хорошо работают на больших МРР-системах - такие, например, как видео-по-запросу

Современное направление развития МРР-систем заключается в увеличении мощности узла путем подсоединения дополнительных процессоров и, по существу, превращения его в SMP-узел. Именно это делают компании NCR, предлагая соединение Bynet, и Tandem с ServerNet. Компания Pyramid также реализовала собственное соединение - Meshine, которое может использоваться для объединения как SMP-платформ, так и однопроцессорных узлов.

МРР-архитектуры привлекательны в первую очередь для разработчиков аппаратных средств, так как в этом случае возникает меньше проблем и ниже стоимость аппаратуры. Из-за того, что нет аппаратной поддержки ни для разделенной памяти, ни для когерентности кэшей, подсоединить большое число процессоров очень просто. Такие системы обеспечивают высокий уровень производительности для приложений с большой интенсивностью вычислений, со статистически разделяемыми данными и с минимальным обменом данными между узлами. Для большинства коммерческих приложений МРР-системы подходят плохо из-за того, что структура базы данных меняется со временем и слишком велики затраты на перераспределение данных.

Ключевым различием между одиночным SMP-узлом и МРР-системой является то, что внутри SMP-узла когерентность данных поддерживается исключительно аппаратными средствами. Это действительно быстро, но и дорого. В МРР-системе с таким же числом процессоров когерентность между узлами реализуется программными средствами. Поэтому происходит это более медленно, однако и цена значительно ниже.

Рис.22. Упрощенная архитектура MPP-системы

Главным преимуществом систем с раздельной памятью является хорошая масштабируемость: в отличие от SMP-систем в машинах с раздельной памятью каждый процессор имеет доступ только к своей локальной памяти, в связи с чем не возникает необходимости в потактовой синхронизации процессоров. Практически все рекорды по производительности на сегодняшний день устанавливаются на машинах именно такой архитектуры, состоящих из нескольких тысяч процессоров (ASCI Red, Blue Pacific).

При этом отсутствие общей памяти заметно снижает скорость межпроцессорного обмена, поскольку нет общей среды для хранения данных, предназначенных для обмена между процессорами. Требуется специальная техника программирования для реализации обмена сообщениями между процессорами. Каждый процессор может использовать только ограниченный объем локального банка памяти. Вследствие указанных архитектурных особенностей требуются значительные усилия для того, чтобы максимально использовать системные ресурсы. Именно этим определяется высокая цена программного обеспечения для массивно-параллельных систем с раздельной памятью.

Системами с раздельной памятью являются суперкомпьютеры IBM RS/6000 SP2, Intel PARAGON/ASCI Red, SGI/CRAY T3E, Hitachi SR8000, транспьютерные системы Parsytec.

Машины последней серии CRAY T3E от SGI, основанные на базе процессоров Dec Alpha 21164 с пиковой производительностью 1200 Мфлопс/с (CRAY T3E-1200), способны масштабироваться до 2048 процессоров. Другая машина этой серии CRAY T3E-900 в конфигурации 1248 процессоров, инсталлированная в правительстве США, показала на Linpack-тесте производительность, равную 634.2 Гфлопс/с.

Гибридная архитектура (NUMA)

Гибридная архитектура NUMA ( nonuniform memory access). Главная особенность такой архитектуры- неоднородный доступ к памяти.

Гибридная архитектура воплощает в себе удобства систем с общей памятью и относительную дешевизну систем с раздельной памятью. Суть этой архитектуры - в особой организации памяти, а именно: память является физически распределенной по различным частям системы, но логически разделяемой, так что пользователь видит единое адресное пространство. Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т.е. к памяти других модулей. При этом доступ к локальной памяти осуществляется в несколько раз быстрее, чем к удаленной. По существу архитектура NUMA является MPP (массивно-параллельная архитектура) архитектурой, где в качестве отдельных вычислительных элементов берутся SMP (cимметричная многопроцессорная архитектура) узлы.

Структурная схема компьютера с гибридной сетью: четыре процессора связываются между собой при помощи кроссбара в рамках одного SMP узла. Узлы связаны сетью типа "бабочка" (Butterfly).

Рис.23. Упрощенная структура NUMA-системы

Впервые идею гибридной архитектуры предложил Стив Воллох и воплотил в системах, серии Exemplar. Вариант Воллоха - система, состоящая из 8-ми SMP узлов. Фирма HP купила идею и реализовала на суперкомпьютерах серии SPP. Идею подхватил Сеймур Крей (Seymour R.Cray) и добавил новый элемент - когерентный кэш, создав, так называемую архитектуру cc-NUMA(Cache Coherent Non-Uniform Memory Access), которая расшифровывается как "неоднородный доступ к памяти с обеспечением когерентности кэшей". Понятие когерентности кэшей описывает тот факт, что все центральные процессоры получают одинаковые значения одних и тех же переменных в любой момент времени. Это достигается синхронизацией информации, хранящейся в кэш-памяти процессоров.

Для обеспечения подобной когерентности кэшей существуют несколько возможностей:

- Использовать механизм отслеживания шинных запросов (snoopy bus protocol), в котором кэши отслеживают переменные передаваемые к любому из центральных процессоров и, при необходимости, модифицируют собственные копии таких переменных.

- Выделять специальную часть памяти, отвечающую за отслеживание достоверности всех используемых копий переменных.

Наиболее известными системами архитектуры cc-NUMA являются: HP 9000 V-class в SCA-конфигурациях, SGI Origin2000, Sun HPC 10000, IBM/Sequent NUMA-Q 2000, SNI RM600. Масштабируемость NUMA-систем ограничивается объемом адресного пространства, возможностями аппаратуры поддержки когерентности кэшей и возможностями операционной системы по управлению большим числом процессоров. На настоящий момент, максимальное число процессоров в cc-NUMA-системах составляет 512 (серия Origin2000). Обычно вся система работает под управлением единой ОС, как в SMP. Возможны также варианты динамического "подразделения" системы, когда отдельные "разделы" системы работают под управлением разных ОС. При работе NUMA-системами, также как с SMP, используют так называемую парадигму программирования с общей памятью (shared memory paradigm).

Кластерная архитектура

Под кластерной системой понимают набор рабочих станций (или даже персональных компьютеров) общего назначения, соединенных с помощью стандартных сетевых технологий (Fast/Gigabit Ethernet, Myrinet) на базе шинной архитектуры или коммутатора. Такие суперкомпьютерные системы являются самыми дешевыми, поскольку собираются на базе стандартных комплектующих элементов ("off the shelf"), процессоров, коммутаторов, дисков и внешних устройств.

Гетерогенными (неоднородными) кластерами называется объединение в кластер компьютеров разной мощности или разной архитектуры.

Архитектура кластерной системы (способ соединения процессоров друг с другом) в большей степени определяет ее производительность, чем тип используемых в ней процессоров. Критическим параметром, влияющим на величину производительности такой системы, является расстояние между процессорами. Так, соединив вместе 10 персональных компьютеров, мы получим систему для проведения высокопроизводительных вычислений, проблема, однако, будет состоять в нахождении наиболее эффективного способа соединения стандартных средств друг с другом, поскольку при увеличении производительности каждого процессора в 10 раз производительность системы в целом в 10 раз не увеличится.

Рассмотрим, для примера задачу построения симметричной 16-ти процессорной такой системы, в которой все процессора были бы равноправны. Наиболее естественным представляется соединение в виде плоской решетки, где внешние концы используются для подсоединения внешних устройств.

Рис.24. Схема соединения процессоров в виде плоской решетки

При таком типе соединения, максимальное расстояние между процессорами окажется равным 6 (количество связей между процессорами, отделяющих самый ближний процессор от самого дальнего). Теория же показывает, что если в системе максимальное расстояние между процессорами больше 4, то такая система не может работать эффективно. Поэтому, при соединении 16 процессоров друг с другом плоская схема является не эффективной. Для получения более компактной конфигурации необходимо решить задачу о нахождении фигуры, имеющей максимальный объем при минимальной площади поверхности. В трехмерном пространстве таким свойством обладает шар. Но, поскольку, нам необходимо построить узловую систему, то вместо шара приходится использовать куб (если число процессоров равно 8) или гиперкуб, если число процессоров больше 8. Размерность гиперкуба будет определяться в зависимости от числа процессоров, которые необходимо соединить. Так, для соединения 16 процессоров потребуется 4-х мерный гиперкуб. Для его построения следует взять обычный 3-х мерный куб, сдвинуть в еще одном направлении и, соединив вершины, получить гиперкуб размером 4

Рис.25. Примеры гиперкубов

Архитектура гиперкуба является второй по эффективности, но самой наглядной. Используются и дугии топологии сетей связи: трехмерный тор, "кольцо", "звезда" и другие. В отличие от кластеров, в МРР-системах узлы не делят ресурсы для хранения. Это главное отличие между кластерными SMP-системами и традиционными МРР-системами.

Важно отметить, что в кластере отдельные экземпляры приложения должны быть осведомлены о работе друг друга: они должны выполнять блокировку доступа к данным, чтобы поддерживать когерентность внутри базы данных. Механизм блокировок делает кластеры более трудными для управления и масштабирования, чем узел SMP. Однако кластеры имеют и некоторые достоинства: высокую доступность приложений и очень большую производительность.

Добиться дополнительного повышения производительности в кластере тяжелее, чем произвести масштабирование внутри узла. Основным барьером является трудность организации эффективных межузловых связей. Коммуникации, которые происходят между узлами, должны быть устойчивы к большим задержкам программно поддерживаемой когерентности. При<