Тема 7. Изучение триггерных схем

Цель:приобретение и усвоение знаний по практическому использованию триггерных схем.

Теоретические сведения

В ЦВМ в процессе обработки информации необходимо ее промежуточное хранение. Для этого используют триггеры – элементы с двумя устойчивыми состояниями, имеющие соответствующие входы для сигналов управления. Основу триггеров – элементарных цифровых автоматов с двумя устойчивыми состояниями, составляет простейшие запоминающие ячейки, которые получают соединением двух потенциальных элементов И-НЕ (ИЛИ-НЕ). Независимо от того, какую функцию выполняет логический элемент И-НЕ или ИЛИ-НЕ, ячейки могут находится в двух устойчивых состояниях 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 – нулевой сигнал на выходе Q, единичный сигнал на выходе  . Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

1. По способу записи информации триггеры разделяются на:

- асинхронные, запись информации в которых осуществляется непосредственно с поступлением информационного сигнала на его вход;

- синхронные, имеющие специальный синхронизирующий входС, сигнал которого разрешает триггеру принять новую информацию (этот сигнал называется также тактирующим, исполнительным или командным).

Синхронные триггеры в зависимости от того, какая часть синхроимпульса (СИ) оказывает влияние на изменение выходов, делятся на три основные группы:

- триггеры, управляемые уровнем синхроимпульса, когда он равен 1 или 0. Это базовые синхронные триггеры, имеющие дополнительный вход для СИ.

- триггеры, управляемые обоими фронтами СИ. Это триггеры с главной и вспомогательной памятью (JKMS).

- триггеры, управляемые одним фронтом СИ (например, D) синхронные триггеры могут быть одно- или многотактными.

2. По числу ступеней:

- одноступенчатые

- двухступенчатые.

Двухступенчатость позволяет получить эффект задержки информации. Двухступенчатые триггеры называются также триггерами MS, поскольку одна из ступеней – slave [sleіv] (раб, невольник) повторяет состояние другой ступени – master [‘ma:ste] (хозяин, владелец, господин).

3. По способу организации логических связей, определяющихособенности функционирования, различают триггеры RS, T, D, JK и других типов.

Основными параметрами триггеров являются: максимальная длительность входного сигнала, время задержки переключения триггера, разрешающее время триггера.

Рассмотрим свойства лишь наиболее распространенных типов триггеров, используемых при построении сложных логических схем, например таких, как счетчики и регистры.

В таблице переходов, отражающей закон функционирования триггера, будем также обозначать последовательные моменты времени. Момент времени t соответствует состоянию триггера до прихода управляющих сигналов. Момент времени t+1 наступает тогда, когда сигналы на выходе триггера под воздействием сигналов на входах принимают значения, соответствующие последующему состоянию. Состояние триггера, соответствующее моменту времени t, будем обозначать  , а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -

, а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -  .

.

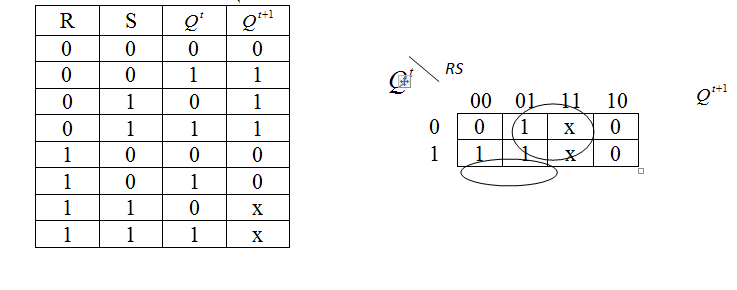

Знак неопределенности «x» в таблице переходов означает, что такая комбинация входных сигналов считается запрещенной, а следовательно, значение функции таких наборов произвольно.

RS-триггер – ячейка хранения информации, триггер с установочным запуском – это логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает состояние 1 (Q=1), а при R=1, S=0 триггер принимает состояние 0 (Q=0).

Рис.7.1–RS-триггер на элементах И-НЕ и временные диаграммы его работы.

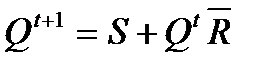

Полная таблица состояний RS-триггера представлена в табл.7.1. Методом карт Карно-Вейча выполним минимизацию переключательной функции для выхода  .

.

Табл.7.1 – Таблица состояний RS-триггера

При доопределении неопределенных значений (х)переключательной функции единицами получим:

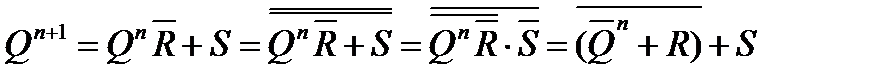

(7.1)

(7.1)

В базисах И-НЕ и ИЛИ-НЕ, функция выхода RS триггера имеет вид:

(7.2)

(7.2)

Рис.7.2 –RS-триггер на злементах ИЛИ-НЕ и его функциональное обозначение

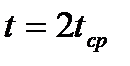

Задержка переключения асинхронных RS-триггеров составит сумму задержек переключения двух логических элементов, на которых выполнены триггеры, т.е.

(7.3)

(7.3)

Действительно для любой схемы при записи информации, например, по входу S (триггер находится в состоянии 0) новое устойчивое состояние триггера Q=1сформируется через интервал времени  , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S.

Для устойчивого функционирования триггера длительность сигнала действующего на его входах R и S, должна быть не меньше суммарной задержки переключения логических элементов обоих плеч триггера для полного установления новых значений выходных уровней. Для вышеприведенных схем длительность входного сигнала должна быть не меньше  , т.е.

, т.е.

Максимальная частота переключения триггера  определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

(7.4)

(7.4)

Следующая maxчастота чередования сигналов на входах определяется интервалом времени  , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

Поскольку сигналы длительностью  являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего

являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего  переключения триггера снижается. Предельная рабочая частота переключения

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS-триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS-триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражением

определяется из выражением

(7.5)

(7.5)

В качестве самостоятельных устройств асинхронныеRS-триггеры находят ограниченное применение, но являются базовыми схемами всех более сложных триггерных устройств. В устройствах цифровой обработки информации в основном применяются синхронизируемые (тактируемые) триггеры.

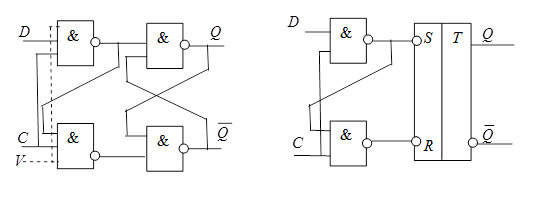

В отличие от асинхронных, синхронные RS-триггеры имеют на входе каждого плеча дополнительные схемы совпадения, первые входы которых объединены и являются входом синхронизирующего импульса (СИ), а вторые входы схем совпадения являются информационными записи 1 (S) и 0 (R). Таким образом, информация, поступающая на входы R и S, может быть передана на собственно триггер только при поступлении СИ.

Рис.7.3 – Варианты схем синхронных RS-триггеров

Использование синхронизации определяет момент приема триггером входной информации и не допускает одновременного действия сигнала, переключающего триггер, и сигнала съема информации с триггера, обеспечивая, тем самым, правильную работу логических каскадов.

Поскольку в потенциальной системе элементов отсутствуют специальные элементы задержки сигналов, для выполнения условий надежной работы логических каскадов на каждый двоичный разряд, хранящий 1 бит информации, использовать 2 триггера, которые управляются двумя сдвинутыми во времени СИ. Таким образом удается информацию, снимаемую с выхода триггера, использовать для управления сигналами на его входах, что необходимо для построения более сложных схем.

ДвойноеТв обозначении триггера означает, что он выполнен по двухступенчатой схеме.

Схема управляется либо от двух СИ, либо, как показано на рис. 7.4, от одного. В составе ИМС RS-триггеры маркируются буквами TP.

Рис. 7.4– Двухступенчатый RS-триггер и его функциональное обозначение

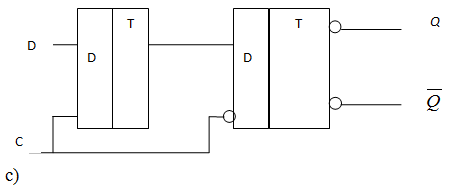

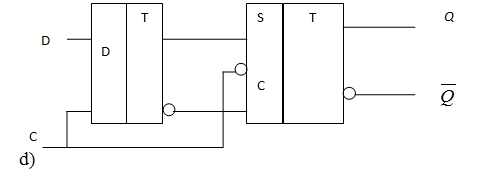

Триггер D-типа, DV-типа – это логическое устройство с двумя устойчивыми состояниями и одним информационным входом D (от delay – задержка, замедление).

Простейшим видом такого триггера является асинхронныйD-триггер.

Табл.7.2 – Таблица состояний D-триггера

|  |

|  |

(7.6)

(7.6)

Уравнение (7.6) показывает, что состояние D-триггера в момент времени  совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

Рис.7.5 – Функциональная схема D-триггера на элементах И-НЕ и инверторах

Схема на инверторах не имеет практического применения, так как функцию D-триггера выполняет схема, состоящая из двух последовательно включенных инверторов. Наибольший интерес представляют синхронные триггеры, нашедшие широкое распространение в ИС.

Рис. 7.6 – D-триггер двухступенчатого типа

По формальной классификации D-триггеры маркируются буквами TM.

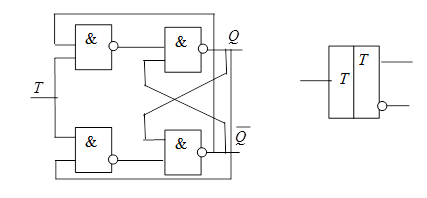

Триггером Т-типа (счетный триггер) называют логическое устройство с двумя устойчивыми состояниями и одним входомТ, изменяющее свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал. Триггер типа Т можно синтезировать как из отдельных логических элементов, так и используя триггер типа D (рис.7.8).

Рисунок 7.7 –Т-триггер на основе RS-триггера.

Рис. 7.8 –Т-триггер на основе D-триггера и его обозначение.

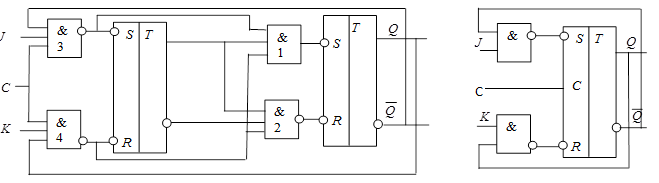

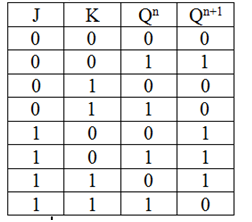

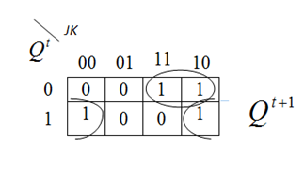

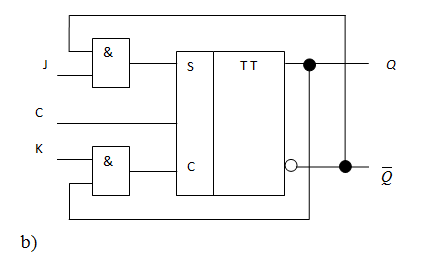

Триггером JK-типа называется устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии  осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS-триггера, при этом вход J эквивалентен входу S, а входК – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS-триггера, при этом вход J эквивалентен входу S, а входК – входу R.

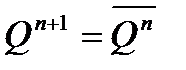

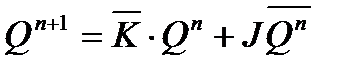

Логическое уравнение триггера, полученное на основе табл.7.3 имеет вид:

(7.7)

(7.7)

Рис. 7.9 –JK-триггер, выполненный по варианту MSс запрещающими связями с элементов 3,4 на 1 и 2

Табл.7.3 – Полная таблица переключений JK-триггера и его карта Карно-

Вейча

Рис. 7.10 – JK- триггер системы ТТЛ

В серии ТТЛ JK-триггер имеет маркировку TB.

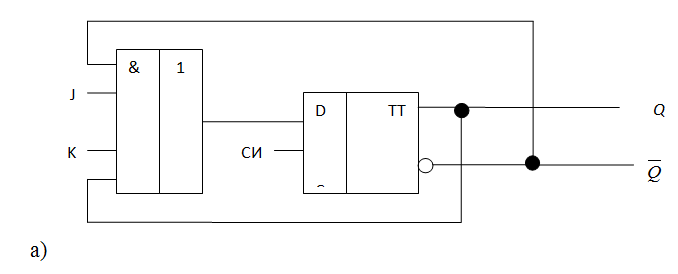

Рис.7.11 – Варианты построения триггерных схем на JK – триггере

Схемные варианты триггеров

Рис.7.12 – Схемные варианты триггеров

Применение универсальных триггеров типа JK и DV, реализованных в одной микросхеме, в пересчетных схемах, регистрах сдвига и т.д. приводит к существенной экономии оборудования.

Естественно, что при построении системы элементов схема триггера может дополняться входной логикой, мощными выходными элементами и т.п. и применяться в нескольких модификациях. Выбор конкретной схемы во многом определяется уровнем разбиения на функциональные узлы.

Задание на самостоятельную работу

1. Выполнить логический анализ и записать переключательную функцию RS и JK триггеров,

2. Выполнить логический анализ и записать переключательную функцию RSсинхронного и асинхронного RS-триггера,

3. Выполнить логический анализ и записать переключательную функцию RSоднотактного и двухтактногоD-триггера,