СтруктурылогическихблоковFPGA.

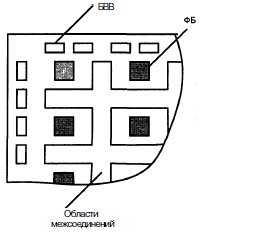

ВнаиболеетипичномвариантеFPGAпредставляетсобоюмикросхемувысокогоуровняинтеграции,содержащуювовнутреннейобластиматрицуидентичныхфункциональныхблоковисистемуихмежсоединений,размещеннуюмеждустрокамиистолбцамиматрицы,авпериферийнойобласти—блокиввода/вывода(рис.1).

Рис.1.ОбобщеннаяструктураFPGA

ВкачествеКЛБ(далеедлякраткостипростоЛБ—логическиеблоки)используются:

· транзисторныепары,простыелогическиевентилиИ-НЕ,ИЛИ-НЕит.п.ТакиеЛБназываютSLC—SimpleLogicCells;

· логическиемодулинаосновемультиплексоров;

· логическиемодулинаосновепрограммируемыхПЗУ,такиеЛБназываютLUTs—Look-UpTables.

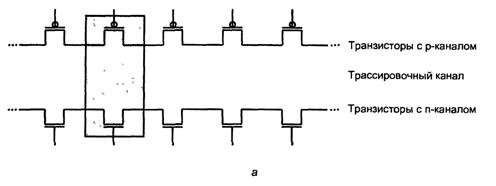

ВажнойхарактеристикойЛБявляетсяих"зернистость"(Granularity).Другойважнойхарактеристикойсчитается"функциональность"(Functionality).Первоесвойствосвязаностем,насколько"мелкими"будуттечасти,изкоторыхможно"собирать"нужныесхемы,второе—стем,наскольковеликилогическиевозможностиЛБ.ПримеромнаиболеемелкозернистогоможетслужитьЛБфирмыCrosspointSolutions(рис.2,а).Блоксодержитцепочкитранзисторовср-иn-каналами(нарисункеиспользованыамериканскиеобозначениятранзисторов,болеепростые,чемотечественные).ЛБ—параизтранзисторовразноготипапроводимости(выделенныйпрямоугольник).Междуцепочкамитранзисторовимеютсятрассировочныеканалы,вкоторыхмогутбытьреализованынеобходимыемежсоединенияэлементов.

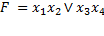

Нарис.2,бпоказанпримермежсоединений,дающихреализациюфункции  -Парытранзистороввпрямоугольникахизштриховыхлинийимеюттакиепостоянныенапряженияназатворах,чтооказываютсязапертыми.Этипарыразделяютцепочкиначасти,изолированныедруготдруга.Втрехсекцияхсобранысхемытипарис.2,в,т.е.ячейкиИ-НЕобычногодлясхемотехникиКМОПтипа.Этиячейкисоединенымеждусобоюкакпоказанонарис.2,г,чтоиприводиткнужномурезультату.МелкозернистостьЛБведеткбольшейгибкостиихиспользования,возможностямреализоватьвоспроизводимыефункцииразнымиспособами,получаяразныевариантывкоординатах"площадькристалла—быстродействие".ВтожевремямелкозернистостьЛБусложняетсистемумежсоединенийFPGAвсвязисбольшимчисломпрограммируемыхточексвязи.

-Парытранзистороввпрямоугольникахизштриховыхлинийимеюттакиепостоянныенапряженияназатворах,чтооказываютсязапертыми.Этипарыразделяютцепочкиначасти,изолированныедруготдруга.Втрехсекцияхсобранысхемытипарис.2,в,т.е.ячейкиИ-НЕобычногодлясхемотехникиКМОПтипа.Этиячейкисоединенымеждусобоюкакпоказанонарис.2,г,чтоиприводиткнужномурезультату.МелкозернистостьЛБведеткбольшейгибкостиихиспользования,возможностямреализоватьвоспроизводимыефункцииразнымиспособами,получаяразныевариантывкоординатах"площадькристалла—быстродействие".ВтожевремямелкозернистостьЛБусложняетсистемумежсоединенийFPGAвсвязисбольшимчисломпрограммируемыхточексвязи.

Рис.2.Схемамелкозернистыхлогическихблоков(а).Реализациямежсоединенийдлявоспроизведенияфункции(б)ипояснениякэтойреализации(в,г)

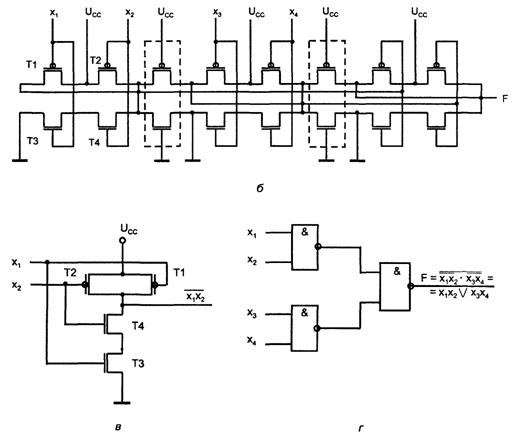

Крупнозернистыеблоки,вчастности,характерныдлясемействFPGAфирмыXilinx.АрхитектурнаяосноваэтихблоковбылазаложенаприсозданиисемействаХС4000,КЛБкоторогосодержиттри.табличныхфункциональныхпреобразователя,дватриггераи16программируемыхмультиплексоров.ВпоследующихFPGAвысокойсложности(семействахVirtex)логическиеблокибылинесколькоупрощены.ТакиеобновленныеКЛБбылизатемиспользованывмикросхемахсемействаSpartan,современногосемействаFPGAсреднейсложности.ЛогическийблокмикросхемсемействаSpartanвнесколькоупрощенномвидепоказаннарис.3.

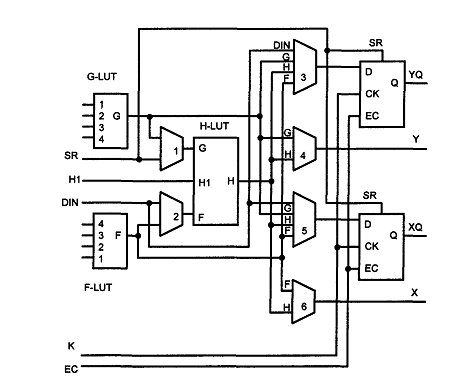

ПосвоейструктуремикросхемыSpartanпродолжаютлиниюразвитияклассическихFPGA,популярнымпредставителемкоторойявляетсясемействоХС4000тойжефирмы.ВфункциональныхблокахэтихмикросхемлогическиепреобразованиявыполняютсятремяLUT-блоками(функциональнымипреобразователямиФП)G,FиН.ПреобразователиGиF—программируемыезапоминающиеустройства(ЗУ)сорганизацией16x1,способныевоспроизводитьлюбыефункциичетырехпеременных,значениякоторыхмогутбытьпереданынавыходыYиXчерезмультиплексоры4и6присоответствующемихпрограммировании(черезлинииверхнихвходовмультиплексоров).

Рис.3.ПримерсхемыфункциональногоблокаFPGA

Черезверхнийвходмультиплексора1инижнийвходмультиплексора2функцииGиFмогутбытьподанынаФП-Н(ЗУсорганизацией8x1)дляобразования"функцииотфункций"сцельюполучениярезультирующейфункции,зависящейотболеечемчетырехаргументов.КтретьемувходуФП-НподключенвходнойсигналHI,такчтоН=/(G,F,HI).АргументамидляФП-Н,поступающимиотмультиплексоров1и2,взависимостиотихпрограммированияможетбытьнетольконаборG,F,HI,нотакженаборыG,HI,DIN;SR,HI,DIN;SR,HI,F.ЛинииDINиSRиспользуютсялибодляпередачивтриггернепосредственновходныхданныхисигналаустановки/сброса(Set/Reset),либокаквходыФП-Н.

ПеречисленныересурсылогическойчастиФБпозволяютвоспроизводить:-любуюфункциюсчисломаргументовдо4включительноплюсвторуютакуюжефункциюплюслюбуюфункциюсчисломаргументовдотрех;-любуюфункцию5аргументов(одну);-любуюфункцию4аргументовиодновременнонекоторыефункции6аргументов,некоторыефункциисчисломаргументовдо9.

СигналыHI,DIN,SR,ЕСявляютсядляФБвходными,ониподаютсянаеговнутренниесхемычерезгруппуизчетырехмультиплексоровMUX"4—1"(нарисункенепоказаны),ккоторымподключены4линиивнешнейшиныуправленияС1...С4.ЭтопозволяетраспределятьсигналыHI,DIN,SRиЕСполиниямС1...С4влюбомжелаемомварианте.

Мультиплексоры3...6направляюттеилииныесигналыданныхуправлениянатриггеры1и2.Триггерымогутиспользоватьсядляфиксацииихранениявыходныхсигналовфункциональныхпреобразователейилижеработатьнезависимоотних.ВходнойсигналФБDINможетбытьпрямымвходомдлялюбоготриггера.СигналHIтожеможнопередаватьлюбомутриггеру,ночерезФПН,чтовноситвцепьегопередачинекоторуюзадержку.

ОбатриггераимеютобщиевходыСКтактированияотсигналаК,разрешениятактированияЕСиустановки/сбросаSR.Внутренниепрограммируемыецепивсхеметриггера(нарис.1.11непоказаны)позволяютиндивидуальнопрограммироватьполярностьтактирующегосигналаСК.СигналЕСсинхронизированссигналомСК,сигналSRасинхронныйидлякаждоготриггерасиспользованиемвнутреннихцепейтриггерапрограммируетсякаксигналустановкиилисброса.Этотсигналопределяетсостояние,вкоторомокажетсятриггерпослепроцессаконфигурациимикросхемы.КонфигурацияопределяетихарактервоздействиянатриггерыимпульсовGSR(GlobalSR)иSRприработесхемы.