Общаяклассификациякристалловпрограммируемойлогики.

ПЛИС–"программируемыелогическиеинтегральныесхемы".

Рассмотримклассификациюпотрем,втомчиследвумкомплексным,признакам:

· архитектуре;

· уровнюинтеграциииоднородности/гибридности;

· числудопустимыхцикловпрограммированияисвязанномусэтимтипупамятиконфигурации.

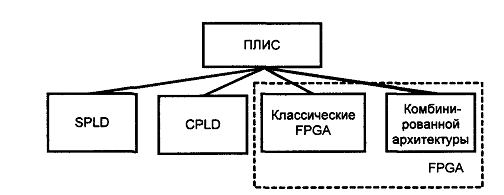

Вклассификациипопервомупризнаку(рис.1)ПЛИСразделенына4класса.

Рис.1.КлассификацияПЛИСпоархитектурнымпризнакам.

Первыйизклассов—SPLD,SimpleProgrammableLogicDevices,т.е.простыепрограммируемыелогическиеустройства.ПоархитектуреэтиПЛИСделятсянаподклассыпрограммируемыхлогическихматрицПЛМ(PLA,ProgrammableLogicArrays)ипрограммируемойматричнойлогикиПМЛ(PAL,ProgrammableArraysLogic,илиGAL,GenericArrayLogic).

ВсложныхпрограммируемыхлогическихсхемахCPLD(ComplexProgrammableLogicDevices)несколькоблоков,подобныхПМЛ,объединяютсясредствамипрограммируемойкоммутационнойматрицы.ВCPLDмогутвходитьсотниблоковидесяткитысячэквивалентныхвентилей.АрхитектурыCPLDразрабатываютсяфирмамиAltera,Atmel,LatticeSemiconductor,CypressSemiconductor,Xilinxидр.ВоздействуянапрограммируемыесоединениякоммутационнойматрицыиПМЛ,входящихвсоставCPLD,можнореализоватьтребуемуюсхему.

МикросхемыпрограммируемыхпользователямивентильныхматрицFPGA(FieldProgrammableGateArrays)всвоейосновесостоятизбольшогочислаконфигурируемыхлогическихблоковЛБ,расположенныхпострокамистолбцамввидематрицы,итрассировочныхресурсов,обеспечивающихихмежсоединения.

СтремлениексочетаниюдостоинствCPLDиFPGAиростуровняинтеграцииБИС/СБИСпривеликпоявлениюПЛИСскомбинированнойархитектурой.КлассПЛИСскомбинированнойархитектуройнеимееттакихчеткихграниц,какклассыCPLDиFPGA,отличаетсябольшимразнообразиемвариантовиразличнойстепеньюблизостиктомуилииномуклассическомутипуПЛИС.Неимеетониобщепринятогоназвания.

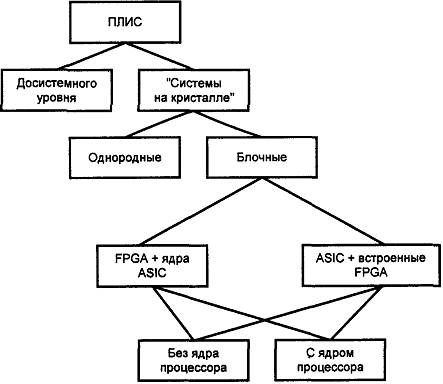

Классификацияпоуровнюинтеграции(рис.2)

Рис.2.КлассификацияПЛИСпоуровнюинтеграции.

ПЛИСсширокимдиапазономизмененияуровняинтеграции(отпростыхдосодержащихсотнитысячвентилей)отнесенык"досистемным"втомсмысле,чтодлянихнерассматривалисьвопросысозданияцелыхсистемнаодномкристалле.

ПЛИСмегавентильногоуровняинтеграцииотнесенык"системамнакристалле",обозначаемымдалеекакSOPC(SystemsOnProgrammableChip).ТерминSOPC(SystemOnProgrammableChip),т.е."системанапрограммируемомкристалле"относитсякПЛИСнаибольшегоуровняинтеграции,содержащимсотнитысячилидажемиллионыэквивалентныхвентилей.Такойвысокийуровеньинтеграциидостигаетсятолькоспомощьюсамыхсовременныхтехнологическихпроцессов(малыетопологическиенормыпроектирования,многослойностьсистемметаллизацииит.д.).НаосновепрогрессивныхтехнологическихпроцессовобеспечиваетсяодновременновысокийуровеньинтеграцииивысокоебыстродействиеБИС/СБИС.Врезультатестановитсявозможнойинтеграциянаодномкристаллецелойвысокопроизводительнойсистемы.

ВоднородныхSOPCразличныеблокисистемыреализуютсяоднимиитемижеаппаратнымисредствами,благодаряпрограммируемоетиэтихсредств.БлочныеSOPCимеютаппаратныеядра,т.е.специализированныеобластикристалла,выделенныедляопределенныхфункций.

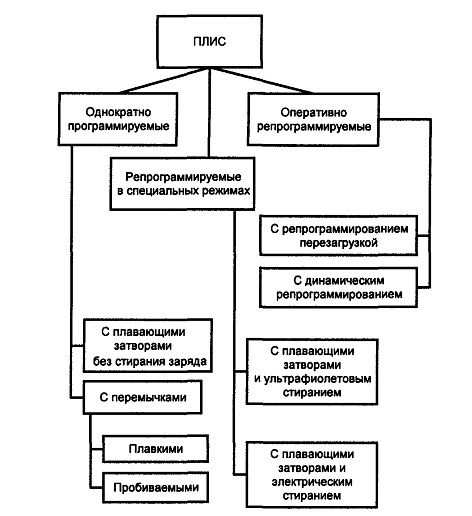

Классификацияпопризнакукратностипрограммирования,определяемойтипомпамятиконфигурации(называемойтакжетеневойпамятью),приведенанарис.3.

Рис.3.КлассификацияПЛИСпопризнакамкратностипрограммирования.(потипутеневойпамяти)

ВоднократнопрограммируемыхПЛИСиспользуютсяэлементыснеобратимымиизменениямисостояний—специальныеперемычкиилиЛИЗМОП-транзисторы.ЛИЗМОП-транзисторыимеютзаряжаемые"плавающие"затворы,которые,вобщемслучае,могуткакзаряжаться,такиразряжаться.ДляоднократнопрограммируемыхПЛИСвозможностиЛИЗМОП–транзисторовиспользуютсялишьчастично:длянихприменяютсятакиеконструкции,вкоторыхотсутствуютвозможностистираниязаписаннойинформации.

МикросхемысвозможностямимногократногопрограммированиясостираниемизаписьюконфигурациивспециальныхрежимахтакжеиспользуютпрограммируемыеэлементыввидеЛИЗМОП–транзисторов.Отпредыдущеговариантаэтимикросхемыотличаютсяналичиемсредствстираниязаписаннойвпамятьинформации.

ВоперативнорепрограммируемыхПЛИСконфигурациязадаетсяспомощьюзагрузкифайлав"теневую"триггернуюпамять,т.е.операций,неимеющихкакого-либоспециальногохарактера.Впротивоположностьпредыдущимвариантамдляпрограммированияненужныниспециальныепрограмматоры,ниспециальныережимысповышенныминапряжениямиидлительностямивоздействийнаэлементыпамяти.Памятьконфигурации—обычнаястатическая(триггерная),т.е.типаSRAM,StaticRandomAccessMemory.

ПринципыпостроенияПЛМнПМЛ.

ПрограммируемыелогическиематрицыПЛМ(PLA,ProgrammableLogicArrays)ипрограммируемаяматричнаялогикаПМЛ(PAL,ProgrammableArraysLogic,илиGAL,GenericArrayLogic).

Обаэтиподклассамикросхемреализуютдизъюнктивныенормальныеформы(ДНФ)переключательныхфункций,аихосновнымиблокамиявляютсядвематрицы:матрицаэлементовИиматрицаэлементовИЛИ,включенныепоследовательно.ТаковаструктурнаямодельПЛМиПМЛ.ТехническионимогутбытьвыполненыикакпоследовательностьдвухматрицэлементовИЛИ-НЕ,новариантыспоследовательностьюматрицИ-ИЛИиспоследовательностьюматрицИЛИ-НЕ—ИЛИ-НЕфункциональноэквивалентны,т.к.второйвариантсогласноправилудеМорганатожереализуетДНФ,нодляинверсныхзначенийпеременных.

Заметим,чтотермин"матрица"обозначаетвданномслучаенеболеечем"набор","множество"иобусловлентем,чтосхемныеэлементыПЛМиПМЛудобнеевсегорасполагатьпострокамистолбцам,обеспечиваятемсамымрегулярностьструктурыБИС.

Навходыпервойматрицыпоступаюттвходныхпеременныхввидекакпрямых,такиинверсныхзначений,такчтоматрицаимеет2твходныхлиний.Наеевыходахформируютсяконъюнктивныетермы,рангкоторыхневышет.Вдальнейшемдлякраткостиконъюнктивныетермыназываютсяпростотермами.Числотермовнеимеетпрямойсвязисвеличинойтиопределяетсяконструктивнымипараметрамиматрицы—числомконъюнкторов,котороеобозначимчерезq.ПерваяматрицаидентичнадляобоихподклассовSPLD,т.е.дляПЛМиПМЛ.

ВыработанныетермыпоступаютнавходматрицыИЛИ.ЭтиматрицыдляПЛМиПМЛразличны.ВПЛМматрицаИЛИпрограммируется,авПМЛонафиксирована.

ПрограммируемаяматрицаИЛИмикросхемПЛМсоставленаиздизъюнкторов,имеющихпоqвходов.Навходыкаждогодизъюнктораприпрограммированииможноподатьлюбуюкомбинациюимеющихсятермов,причемтермыможноиспользоватьмногократно(т.е.одинитотжетермможетбытьиспользовандляподачинавходынесколькихдизъюнкторов).

ЧислодизъюнктороввматрицеИЛИопределяетчисловыходовПЛМ,котороеобозначимчерезл.

Изизложенноговидно,чтоПЛМпозволяетреализоватьсистемуизnпереключательныхфункций,зависящихнеболеечемотmпеременныхисодержащихнеболеечемqтермов.ПоэтомуфункциональныевозможностиПЛМхарактеризуютсятремяцифрами:m,q,n.

ВПМЛвыработанныематрицейИтермыпоступаютнафиксированную(непрограммируемую)матрицуэлементовИЛИ.Этоозначаетжесткоезаранеезаданноераспределениеимеющихсятермовмеждуотдельнымидизъюнкторами.Каждомудизъюнкторупридаютсясвоисобственныетермы,иеслидляразныхдизъюнкторовокажутсянужнымиодинаковыетермы,придетсявырабатыватьихвматрицеИнесколькораз.ОднакоприэтомпрограммируемостьматрицыИЛИисключается,чтодлямногихзадачвитогесущественноупрощаетсхемуПМЛвсравнениисосхемойПЛМ.

ПЛМобладаютбольшейфункциональнойгибкостью,всевоспроизводимыеимифункциимогутбытькомбинациямилюбогочислатермов,формируемыхматрицейИ.Этополезноприреализациисистемпереключательныхфункций,имеющихбольшиевзаимныепересеченияпотермам.Такиесистемысвойственны,например,задачамформированиясигналовуправлениямашиннымицикламипроцессоров.Дляширокораспространенныхвпрактикезадачпостроения"произвольнойлогики"большоепересечениефункцийпотермамнетипично.ДлянихпрограммируемостьматрицыИЛИиспользуетсямалоистановитсяизлишнейроскошью,неоправданноусложняющеймикросхему.ПоэтомуПМЛраспространеныбольше,чемПЛМ,икихчислуотноситсябольшинствоSPLD.

СтруктурыПМЛполнееосвещенынижеприописанииCPLD.

ОбщаяструктураCPLD.

CPLD—микросхемывысокогоуровняинтеграции,основнымичастямикоторыхявляются:

· PAL(GAL)—подобныефункциональныеблоки;

· системакоммутации,позволяющаяобъединятьфункциональныеблокивединоеустройство,выполненнаяввидематрицысоединений.

· блокиввода/вывода.

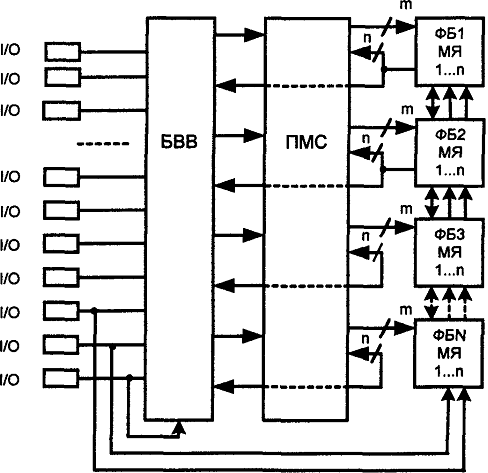

ВсесоставныечастиCPLDпрограммируются.ОбобщеннаяструктураCPLDпоказананарис.1.

Вструктурнойсхемепринятыследующиеобозначения.ЧерезФБ(FB)обозначеныфункциональныеблоки,числокоторыхNзависитотуровняинтеграциимикросхемыиизменяетсявдовольноширокихпределах.ВкаждомФБимеетсяпмакроячеекМЯ(МС,Macrocells).ФункциональныеблокиполучаютвходныесигналыотпрограммируемойматрицысоединенийПМС(PIA,ProgrammableInerconnectArray).Числотакихсигналовт.ВыходныесигналыФБпоступаюткаквПМС,такивблокиввода/выводаCPLD(IOBs,Input/OutputBlocks,БВВ).ПМСобеспечиваетполнуюкоммутируемостьфункциональныхблоков,т.е.возможностьподаватьсигналыслюбогоихвыходаналюбойвход.

Рис.1.ОбобщеннаяструктураCPLD

Блокиввода/выводасвязанысвнешнимидвунаправленнымивыводамиI/O,которые,взависимостиотпрограммирования,могутбытьиспользованыкаквходыиликаквыходы.ТринижнихвыводалибоспециализируютсядляподачинаматрицуфункциональныхблоковсигналовGCK(GlobalClocks)глобальноготактирования,сигналовGSR(GlobalSet/Reset)глобальнойустановки/сбросаисигналовGTS(Global3-stateControl)глобальногоуправлениятретьимсостояниемвыходныхбуферов,либоэтижевыводымогутбытьиспользованыдляоперацийввода/вывода.Здесьидалеетермин"глобальный"применяетсядлясигналов,общихдлявсеймикросхемы.

Числоконтактовввода/выводаможетсовпадатьсчисломвыходоввсехФБ,номожетбытьименьшим.Впоследнемслучаечастьмакроячеекможетбытьиспользованатолькодлявыработкивнутреннихсигналовустройства(вчастности,сигналовобратнойсвязи).Необходимостьвтакихсигналахтипичнадляструктурбольшинствацифровыхустройств.

Структуранарис.1несколькоупрощена.КромепоказанныхблоковвCPLDмогутприсутствоватьконтроллерыдляуправленияоперациямипрограммированиянепосредственновсистеме(InSystemProgrammability,ISP),контроллерыдляработысинтерфейсомJTAGидр.

СтруктурамакроячейкиCPLD.

Макроячейкасодержитвкачествеосновыпрограммируемыемультиплексоры,триггер(илитриггеры)иформируетгруппувыходныхсигналовФБвнесколькихихвариантах.

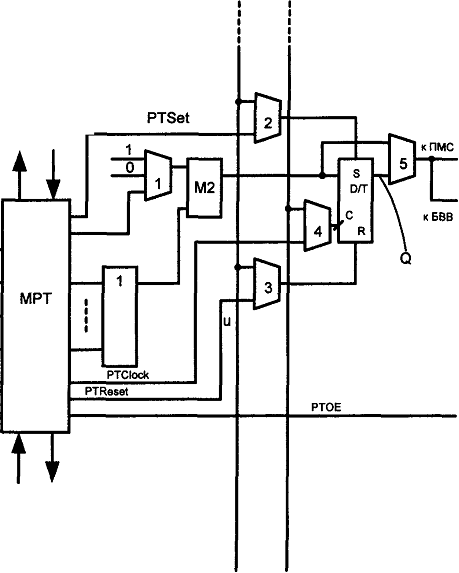

Нарис.1раскрытасхемаоднойизидентичныхмакроячеекФБ.ПрообразомпоказаннойсхемыявляетсямакроячейкаCPLDXC9500фирмыXilinx,неимеющаяразделяемого(общего)логическогорасширителя.

Рис.1.ПримерсхемымакроячейкифункциональногоблокаCPLD

Программируемостьмультиплексороввэтойсхемеивсехдальнейшихнеотображается,т.к.онаприсущавсемимеющимсявсхемемультиплексорам,еслинеоговоренопротивоположное.Взависимостиотпрограммированиякаждыймультиплексорпередаетнавыходсигналстогоилииноговхода.

ТриггерможетпрограммироватьсянарежимыработытриггератипаDилиТ.Заметим,кстати,чтоприописаниимикросхемпрофаммируемойлогикитриггерывиностраннойлитературечащевсегоназываютрегистрами.ТриггерытактируютсяположительнымифронтамисинхросигналовиимеютвходыустановкиSисбросаR.ВыходныесигналыФБпередаютсявПМСивблокиввода/выводаБВВ.

Аргументых1,...,хМреализуемоймакроячейкойфункциипоступаютнаматрицуМиизПМС.АргументамидляМЯмогутбытькаквходныесигналы,поступающиеизвнечерезБВВ,такисигналыобратныхсвязей,подаваемыевматрицуИсвыходовмакроячеек.Нарис.1.входныесигналыматрицынезависимоотиххарактераобозначенычерезx1,...,хМ.Входныебуферыпреобразуютсигналывпарафазные,представляякаждыйсигналегопрямымиинверснымзначениями,такчтовматрицеимеется2твертикальныхлинийиобразующиеееконъюнкторыимеютпо1твходов.ПятьтермовизматрицыИпоступаютнаэлементИЛИдляобразованиялогическойфункции.Дляуправлениятриггеромибуферамиблокаввода/выводавырабатываютсятакжетермыPTSet,PTClock,PTReset,которыемогутбытьиспользованыкаксигналыустановки,синхронизацииисбросатриггера.ТермРТОЕ—программируемыйтермуправлениятретьимсостояниембуфераБВВ(ОЕ,OutputEnable).ВсеговматрицеИнарис.1.программируются9Nтермов.

НавыходеэлементаИЛИвырабатываетсялогическаяфункциявформеДНФранганеболеет.Еезначениепередаетсядальшечерезэлементсложенияпомодулю2,навторойвходкоторого,взависимостиотпрограммированиямультиплексора1,можетбытьподанлогическийнуль,логическаяединицаилитермРТ1.Впервомслучаефункцияпередаетсябезизменений(F=F*),вовтороминвертируется(F=!F*),втретьемпередаетсявпрямомвидевовсехситуацияхзаисключениемтакой,вкоторойРТ1=1.

МультиплексорMUX5программируетсядляпередачинавыходМЯлибонепосредственнозначенияфункцииF(комбинационныйвыход),либосостояниятриггера(регистровыйвыход).ХарактертактированиятриггераопределяетсяпрограммированиеммультиплексораMUX4,приэтомвозможноиспользованиеглобальногосинхросигнала(GCK,GlobalClock)илисигнала,порождаемоготермомPTClock.Асинхронныеустановкаисбростриггерапроизводятсялибоглобальнымсигналом(GSR,GlobalSet/Reset),либотермамиPTSetиPTReset,чтоопределяетсяпрограммированиеммультиплексоровMUX2иMUX3.Самтриггерпрограммируетсянарежимытриггеразадержки(типаD)илисчетного(типаТ).

ОсновнойвыходнойсигналмакроячейкипоступаеткаквПМС,котораяможетнаправлятьегополюбомутребуемомумаршруту,такивблокиввода/вывода.

Принципыпостроениявентильныхматриц(GA).Общаяклассификация.

Базовыематричныекристаллыназываюттакжевентильнымиматрицами(ВМ),чтосоответствуетпринятомудляБМКанглийскомутерминуGA(GateArray).ТерминБМКпреобладаетвотечественнойлитературеипоэтомуиспользуетсявэтойкниге,хотятермин"вентильнаяматрица"былбыпредпочтителенкакнепротиворечащиймеждународнойтерминологии.

Базовыематричныекристаллыизвестныс1975года,когдаамериканскаяфирмаAmdahlCorpприменилаихвсоставевысокопроизводительнойЭВМсцельюисключенияизнеемикросхеммалогоисреднегоуровнейинтеграции.Результатыоказалисьудачными,ивпоследующиегодыБМКполучилиширокоераспространение.

БМК—кристалл,напрямоугольнойповерхностикоторогоразмещенывнутренняяипериферийнаяобласти(ВОиПО).Вовнутреннейобластипострокамистолбцам(ввидематрицы)расположеныбазовыеячейки—группынескоммутированныхсхемныхэлементов(транзисторов,резисторов).

Элементныйсоставбазовойячейкиприразныхвариантахмежсоединенийэлементовдопускаетреализациюнекоторогомножествасхемопределенногокласса,каждаяизкоторыхсоответствуетопределеннойфункциональнойячейке(ФЯ).ДлявыпускаемоговпродажуБМКсоздаетсябиблиотекафункциональныхячеек,т.е.,всущности,рисунковмежсоединений,дающихтуилиинуюсхему.БиблиотекифункциональныхячеекБМКнасчитываютобычнодесяткиилисотнитиповыхузлов,реализованныхнаоднойилинесколькихбазовыхячейках.

ВБМКканальнойструктурымеждустрокамиистолбцамибазовыхячеекилиихкомпактныхгруппоставляютсягоризонтальныеивертикальныесвободныезоны(каналы)длямежсоединений.

Впериферийнойобластикристалларазмещаютсяпериферийныеячейки,выполняющиеоперацииввода/выводасигналовчерезконтактныеплощадки,расположенныепокраямкристалла.

ПереходотбиполярнойсхемотехникикМОП-транзисторнымсхемамсделалвозможнымболееплотноеразмещениесхемныхэлементовнакристалле.Приростесложностилогическойчастисхемы,т.е.числалогическихэлементовнакристалле,ещебыстреерастетсложностьмежсоединений.Длясниженияпотерьплощадикристалла,затрачиваемойнатрассировочныеканалы,быларазработанабесканальнаяструктураБМКтипа"моревентилей"или"моретранзисторов",вкоторойконструкторыотказалисьотсвободныхзонкристалла,заранееотведенныхдлямежсоединений.ВтакихБМКвсявнутренняяобластьплотнозаполняетсябазовымиячейками,амежсоединенияпроводятсятолькотам,гдеэтонеобходимо,причемнаходящиесяподнимибазовыеячейкиоказываютсявданнойконкретнойсхеменеиспользуемыми.

ЕщеоднойразновидностьюБМКявляютсяблочные,вкоторыхнакристаллевыделяютсяспециализированныеобласти-подматрицыдлявыполнениязаранееопределенныхфункций(логическойобработкиданных,памятиидр.).

Междуподматрицамиразмещаютсяспециальныетрассировочныеканалы,напериферииподматрицизготовляютсявнутренниепериферийныеячейкидляпередачисигналовпомежблочнымсвязям.

ИзобретениебазовыхматричныхкристалловозначалопоявлениеновогоклассаспециализируемыхБИС/СБИС—полузаказных.

ДляреализацииконкретнойполузаказнойсхемынаосновеБМК(такиесхемыназываютМАБИС,т.е.матричныеБИС,илиБИСМ,т.е.БИСматричные)нужнытолькошаблонырисунковмежсоединений.Например,привнедрениипервыхБМКвфирмеAmdahlCorpдлязаказныхсхемтребоваласьразработка13шаблонов,адляполузаказныхМАБИСтолькотрех.

Взаключениеотметим,чтодляболеечеткогоотраженияместаБМКвиерархиимикросхемполезнодополнитьанглийскуюаббревиатуруGAдоаббревиатурыMPGA,MaskProgrammableGateArray.

Заметимтакже,чтонарядусописаннымвышевариантомБМКсуществуютиБМКслазернымпрограммированиеммежсоединений(LPGA,LaserProgrammableGateArrays).ВэтихБМКпервоначальноизготовляютсяметаллизированнымидорожкамивсевозможныемежсоединенияэлементов,априпрограммированиичастьсоединенийподвоздействиемточносфокусированныхуправляемыхлазерныхлучейразрывается.ТакиеБМКподобныобычнымвтом,чтодляконфигурированияМАБИСпотребительдолженобращатьсякизготовителю,т.е.напредприятиеэлектроннойпромышленности,однакосрокиистоимостьвыполнениязаказавсравнениисобычнымиБМКоказываютсяиными.Срокивыполнениязаказасокращаются,чтоблагоприятносточкизренияускорениявыходапродукциинарынок,однаковнастоящеевремяБМКслазернымпрограммированиемраспространеныменьше,чемобычные,хотяимеютсяфирмы,развивающиеихпроизводство,вчастностифирмаChipExpress.