Комбинационныецифровыеустройства.Шифраторидешифратор.Определение,принципфункционирования.

Типыцифровыхустройств.Определениепринадлежностиустройствакпервомуиливторомутипу.Примерыустройств,относящихсякпервомуивторомутипу.

Типыбазовыхцифровыхустройств(БЦУ):

· Комбинационныецифровыеустройства(КЦУ)

· Конечныеавтоматы(последовательностныесхемы)

КЦУ–этоустройства,неимеющиевсвоейструктуреобратныхсвязей.Вкаждыймоментвременисостояниевыходовзависитотвходноговоздействия(памятьотсутствует).КЦУописываютсяпростымилогическимиуравнениями,всеаргументыкоторых–входныезначения.Такиеустройстваслужатдляпреобразованияинформацииидлякоммутации.ОтсюдадватипаКЦУ:кодопреобразующиеикоммутационные.

ВсеКЦУстроятсяметодомпростогосинтезапозаданнойтаблицефункционированияилипологическомууравнению,заданномувканоническойформе.

КкодопреобразующимКЦУотносятсясумматоры,кодопреобразователи,шифраторыидешифраторы.

КкоммутационнымКЦУотносятсямультиплексорыидемультиплексоры.

Конечныеавтоматы–устройства,содержащиевсвоейструктуреобратныесвязи(ОС).Такимобразом,вкаждыймоментвременисостояниевыходовзависитнетолькоотвходноговоздействия,ноиотсостояниявыходавпредыдущиймоментвремени.Онислужатдляхраненияинформациииеепреобразованиясучетомпредыдущегосостояния.

ОднастепеньОСпозволяетхранитьинформацию–этосвязьвнутрипростейшейячейки.ВтораястепеньОСпозволяетпреобразовыватьинформацию.Этосвязимеждупростейшимиячейками.Простейшейячейкойилипростейшимконечнымавтоматомявляетсятриггер.

Устройства–триггеры,счетчики,регистры.

Комбинационныецифровыеустройства.Мультиплексорндемультиплексор.Определение,принципфункционирования.

Длянаправленияилираспространенияпотоковинформациислужаткоммутационныесхемы.Книмотносятсямультиплексорыидемультиплексоры.

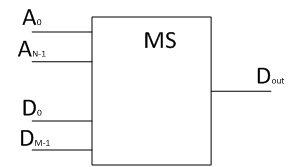

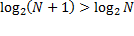

Мультиплексор–устройство,коммутирующееодинизвходовданных,адрескоторогоуказаннаадресныхвходахсединственнымвыходом.ТакоеустройствоимеетNадресныхвходов(A0…AN-1),Mвходовданных(D0…DM-1)иодинвыходданных–Dout.Соотношениемеждуколичествомвходовданныхиколичествомадресныхвходов  .

.

Пример:мультиплексорначетыревходаданных.Такоеустройствоимеетдваадресныхвхода.

Таблицафункционирования

| A1 | A0 | D3 | D2 | D1 | D0 | Dout |

| - | - | - | 0/1 | 0/1 | ||

| - | - | 0/1 | - | 0/1 | ||

| - | 0/1 | - | - | 0/1 | ||

| 0/1 | - | - | - | 0/1 |

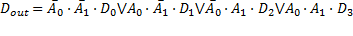

Изтаблицыполучаемвыражениедляпостроениясхемы:

Схема

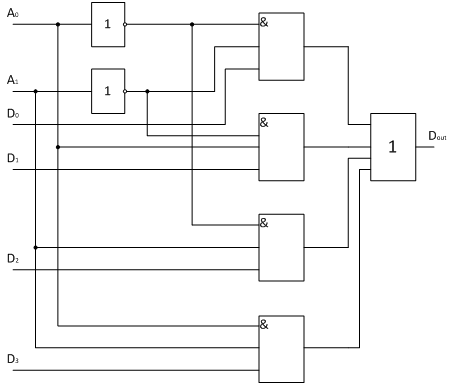

Демультиплексор–устройство,распределяющееинформациюсединственноговходанаодинизвыходов,адрескоторогоуказаннаадресныхвходах.

Вэтомустройствеодинвходданных,N(A0…AN-1)адресныхвходовиM(D0…DM-1)выходовданных.

.

.

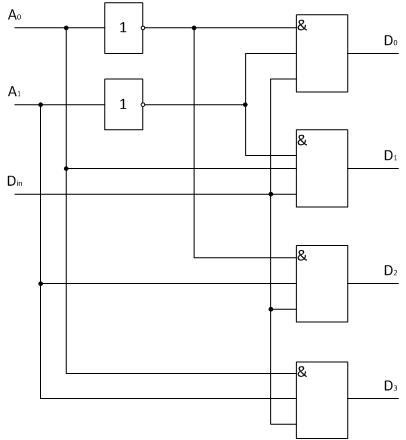

Пример.Демультиплексорначетыревыходаданных.Такоеустройствоимеетдваадресныхвхода.

Таблицафункционирования

| A1 | A0 | Din | D3 | D2 | D1 | D0 |

| 0/1 | - | - | - | 0/1 | ||

| 0/1 | - | - | 0/1 | - | ||

| 0/1 | - | 0/1 | - | - | ||

| 0/1 | 0/1 | - | - | - |

Выражениядлякаждоговыхода:     | Схемаустройства:  |

Регистры.Классификация.

Регистры–конечныеавтоматы,служащиедляхраненияилидлясдвигаинформации.Основапостроениярегистров–D-триггеры.

Пофункцииразличаютдватипарегистров:

· Последовательные(сдвигинформации)

· Параллельные(хранение,записаннойинформации)

Последовательныерегистрыработаютпооднопроводнойсистеме.

Параллельные–подключаютсяпараллельнопошине.Шина–группапроводов,несущиходнуинформацию.

Поспособуподключениявходов/выходовсуществуют:

· Параллельно-последовательные

· Последовательно-параллельные

Поспособузаписиисчитываниярегистрыклассифицируютсякакпоследовательные,параллельные,параллельно-последовательныеипоследовательно-параллельные.Впоследовательно-параллельныхрегистрахзаписьпроисходитпоследовательнымспособоми,призаполнениирегистра,включаетсяпараллельныйбуферчтения.Впараллельно-последовательныхрегистрахзаписьпроисходитпараллельнымспособомчерезбуферзаписи,которыйвдальнейшемотключается,ивключаютсяобратныесвязипоследовательногорегистра.Считываниепроизводитсяпоследовательнымспособом.

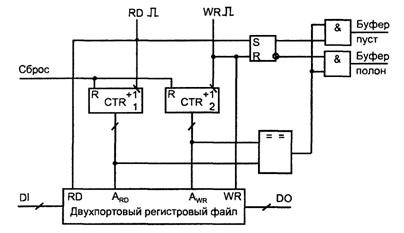

БуферFIFO

БуферFIFO,примерструктурыкоторогоприведеннарис.1,представляетсобоюЗУдляхраненияочередейданных(списков)спорядкомвыборкислов,такимже,чтоипорядокихпоступления.Интервалымеждусловамимогутбытьсовершенноразличными,т.к.моментызаписисловавбуферисчитыванияизнегозадаютсявнешнимисигналамиуправлениянезависимодруготдруга.

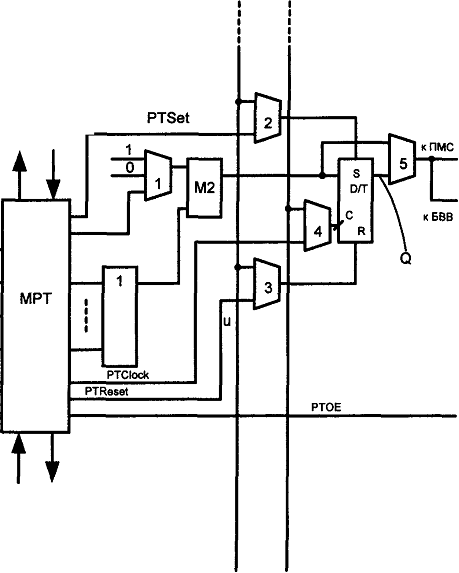

Рис.1.СтруктурабуфераFIFO

Возможностьиметьразныйтемпприемаивыдачисловнеобходима,например,еслиприемникспособенприниматьданные,поступающиерегулярноснекоторойчастотой,аисточникинформациивыдаетсловавболеебыстромтемпеи,можетбыть,ктомуженерегулярно.ТакиеданныепоступаютвихтемпевбуферFIFO,аизнегосчитываютсярегулярноснеобходимойдляприемникаданныхчастотой.Новоесловоставитсявконецочереди,считываниеосуществляетсясначалаочереди.

Всхеме(рис.1)передначаломработыобасчетчикаадресовCTR1иCTR2сбрасываются.Призаписиадресаувеличиваютсянаединицуприкаждомобращении,т.е.возрастают,начинаяснулевого.Тожепроисходитпричтениислов,такчтоадресчтениявсегда"гонится"заадресомзаписи.Еслиадресасравняютсяпричтении,тобуферпуст.Еслиадресасравняютсяпризаписи,тобуферполон(адресамизанятавсяемкостьсчетчика).Этиситуацииотмечаютсясоответствующимисигналами.Еслибуферполон,тонужнопрекратитьприемданных,аеслипуст,тонужнопрекратитьчтение.Очередьудлиняетсяилиукорачиваетсявзависимостиотразностичиселзаписанныхисчитанныхслов.Переходчерезнульосложненийневызывает.

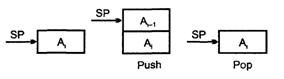

Стек

Стек(магазиннаяпамять)удобендлязапоминаниямассиваслов,т.к.приэтомнетребуетсяадресоватькаждоесловоотдельно.Словазагружаютсявстеквопределенномпорядке,присчитываниитакжезаранееизвестенпорядокихследования.Вчастности,стекудобенпризапоминаниисостоянийрегистроввмоментпрерыванияпрограммы.Порядоквводасловвстекиихсчитыванияпредопределеныегоустройством.ПриорганизациитипаLIFO(LastIn—FirstOut)последнеезаписанноевстексловоприсчитываниипоявляетсяпервым.СтекLIFOпопорядкузаписи-считыванияподобенстопкетарелок—дляиспользованияснимаетсяверхняя,т.е.последняяположенная,затемвтораяит.д.Интересноотметить,чтосамтермин"стек"произошелименноотобозначениятакойстопки.

Стекимеетдноиверхушку,направлениевозрастанияномеровячееквнемможетбытьразличным(обычныйиперевернутыйстеки).Операциисостеком—Push(записьслова)иPop(считываниеслова).

АппаратностекреализуетсявОЗУ,гдедлянеговыделяетсяопределеннаяобласть.УказательстекаSPсодержитадреспоследнейзанятойячейки(рис.2).ПривыполненииоперацийPushиPopзначениеSPуменьшаетсяилиувеличивается.ЗадаваявSPначальноезначение,можноразмещатьстеквтойилиинойобластиОЗУ,следяприэтомзатем,чтобыэтаобластьнеиспользоваласьдлядругихцелей.ПрибайтовойорганизациипамятиизанесениивстексодержимогорегистровойпарыстаршийбайтзапоминаетсяпоадресуSP-1,амладший—поадресуSP-2,содержимоеSPуменьшаетсяна2.Привыборкесодержимоедвухверхнихячеекстекапомещаетсявсоответствующиерегистры,асодержимоеSPувеличиваетсяна2.

Рис.2.Реализациястекавмикропроцессорнойсистеме

Основноеназначениестека—обслуживаниепрерыванийпрограммыивыполненияподпрограмм.

ПринципыпостроенияПЛМнПМЛ.

ПрограммируемыелогическиематрицыПЛМ(PLA,ProgrammableLogicArrays)ипрограммируемаяматричнаялогикаПМЛ(PAL,ProgrammableArraysLogic,илиGAL,GenericArrayLogic).

Обаэтиподклассамикросхемреализуютдизъюнктивныенормальныеформы(ДНФ)переключательныхфункций,аихосновнымиблокамиявляютсядвематрицы:матрицаэлементовИиматрицаэлементовИЛИ,включенныепоследовательно.ТаковаструктурнаямодельПЛМиПМЛ.ТехническионимогутбытьвыполненыикакпоследовательностьдвухматрицэлементовИЛИ-НЕ,новариантыспоследовательностьюматрицИ-ИЛИиспоследовательностьюматрицИЛИ-НЕ—ИЛИ-НЕфункциональноэквивалентны,т.к.второйвариантсогласноправилудеМорганатожереализуетДНФ,нодляинверсныхзначенийпеременных.

Заметим,чтотермин"матрица"обозначаетвданномслучаенеболеечем"набор","множество"иобусловлентем,чтосхемныеэлементыПЛМиПМЛудобнеевсегорасполагатьпострокамистолбцам,обеспечиваятемсамымрегулярностьструктурыБИС.

Навходыпервойматрицыпоступаюттвходныхпеременныхввидекакпрямых,такиинверсныхзначений,такчтоматрицаимеет2твходныхлиний.Наеевыходахформируютсяконъюнктивныетермы,рангкоторыхневышет.Вдальнейшемдлякраткостиконъюнктивныетермыназываютсяпростотермами.Числотермовнеимеетпрямойсвязисвеличинойтиопределяетсяконструктивнымипараметрамиматрицы—числомконъюнкторов,котороеобозначимчерезq.ПерваяматрицаидентичнадляобоихподклассовSPLD,т.е.дляПЛМиПМЛ.

ВыработанныетермыпоступаютнавходматрицыИЛИ.ЭтиматрицыдляПЛМиПМЛразличны.ВПЛМматрицаИЛИпрограммируется,авПМЛонафиксирована.

ПрограммируемаяматрицаИЛИмикросхемПЛМсоставленаиздизъюнкторов,имеющихпоqвходов.Навходыкаждогодизъюнктораприпрограммированииможноподатьлюбуюкомбинациюимеющихсятермов,причемтермыможноиспользоватьмногократно(т.е.одинитотжетермможетбытьиспользовандляподачинавходынесколькихдизъюнкторов).

ЧислодизъюнктороввматрицеИЛИопределяетчисловыходовПЛМ,котороеобозначимчерезл.

Изизложенноговидно,чтоПЛМпозволяетреализоватьсистемуизnпереключательныхфункций,зависящихнеболеечемотmпеременныхисодержащихнеболеечемqтермов.ПоэтомуфункциональныевозможностиПЛМхарактеризуютсятремяцифрами:m,q,n.

ВПМЛвыработанныематрицейИтермыпоступаютнафиксированную(непрограммируемую)матрицуэлементовИЛИ.Этоозначаетжесткоезаранеезаданноераспределениеимеющихсятермовмеждуотдельнымидизъюнкторами.Каждомудизъюнкторупридаютсясвоисобственныетермы,иеслидляразныхдизъюнкторовокажутсянужнымиодинаковыетермы,придетсявырабатыватьихвматрицеИнесколькораз.ОднакоприэтомпрограммируемостьматрицыИЛИисключается,чтодлямногихзадачвитогесущественноупрощаетсхемуПМЛвсравнениисосхемойПЛМ.

ПЛМобладаютбольшейфункциональнойгибкостью,всевоспроизводимыеимифункциимогутбытькомбинациямилюбогочислатермов,формируемыхматрицейИ.Этополезноприреализациисистемпереключательныхфункций,имеющихбольшиевзаимныепересеченияпотермам.Такиесистемысвойственны,например,задачамформированиясигналовуправлениямашиннымицикламипроцессоров.Дляширокораспространенныхвпрактикезадачпостроения"произвольнойлогики"большоепересечениефункцийпотермамнетипично.ДлянихпрограммируемостьматрицыИЛИиспользуетсямалоистановитсяизлишнейроскошью,неоправданноусложняющеймикросхему.ПоэтомуПМЛраспространеныбольше,чемПЛМ,икихчислуотноситсябольшинствоSPLD.

СтруктурыПМЛполнееосвещенынижеприописанииCPLD.

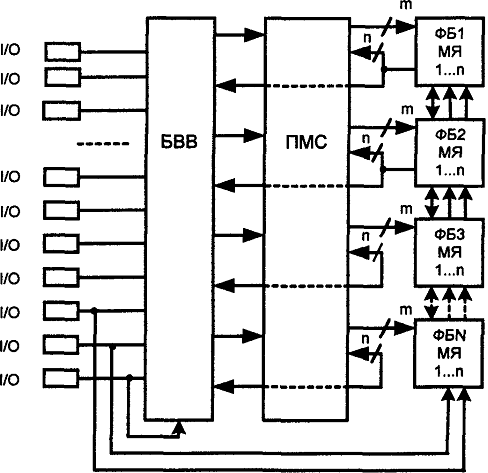

ОбщаяструктураCPLD.

CPLD—микросхемывысокогоуровняинтеграции,основнымичастямикоторыхявляются:

· PAL(GAL)—подобныефункциональныеблоки;

· системакоммутации,позволяющаяобъединятьфункциональныеблокивединоеустройство,выполненнаяввидематрицысоединений.

· блокиввода/вывода.

ВсесоставныечастиCPLDпрограммируются.ОбобщеннаяструктураCPLDпоказананарис.1.

Вструктурнойсхемепринятыследующиеобозначения.ЧерезФБ(FB)обозначеныфункциональныеблоки,числокоторыхNзависитотуровняинтеграциимикросхемыиизменяетсявдовольноширокихпределах.ВкаждомФБимеетсяпмакроячеекМЯ(МС,Macrocells).ФункциональныеблокиполучаютвходныесигналыотпрограммируемойматрицысоединенийПМС(PIA,ProgrammableInerconnectArray).Числотакихсигналовт.ВыходныесигналыФБпоступаюткаквПМС,такивблокиввода/выводаCPLD(IOBs,Input/OutputBlocks,БВВ).ПМСобеспечиваетполнуюкоммутируемостьфункциональныхблоков,т.е.возможностьподаватьсигналыслюбогоихвыходаналюбойвход.

Рис.1.ОбобщеннаяструктураCPLD

Блокиввода/выводасвязанысвнешнимидвунаправленнымивыводамиI/O,которые,взависимостиотпрограммирования,могутбытьиспользованыкаквходыиликаквыходы.ТринижнихвыводалибоспециализируютсядляподачинаматрицуфункциональныхблоковсигналовGCK(GlobalClocks)глобальноготактирования,сигналовGSR(GlobalSet/Reset)глобальнойустановки/сбросаисигналовGTS(Global3-stateControl)глобальногоуправлениятретьимсостояниемвыходныхбуферов,либоэтижевыводымогутбытьиспользованыдляоперацийввода/вывода.Здесьидалеетермин"глобальный"применяетсядлясигналов,общихдлявсеймикросхемы.

Числоконтактовввода/выводаможетсовпадатьсчисломвыходоввсехФБ,номожетбытьименьшим.Впоследнемслучаечастьмакроячеекможетбытьиспользованатолькодлявыработкивнутреннихсигналовустройства(вчастности,сигналовобратнойсвязи).Необходимостьвтакихсигналахтипичнадляструктурбольшинствацифровыхустройств.

Структуранарис.1несколькоупрощена.КромепоказанныхблоковвCPLDмогутприсутствоватьконтроллерыдляуправленияоперациямипрограммированиянепосредственновсистеме(InSystemProgrammability,ISP),контроллерыдляработысинтерфейсомJTAGидр.

СтруктурамакроячейкиCPLD.

Макроячейкасодержитвкачествеосновыпрограммируемыемультиплексоры,триггер(илитриггеры)иформируетгруппувыходныхсигналовФБвнесколькихихвариантах.

Нарис.1раскрытасхемаоднойизидентичныхмакроячеекФБ.ПрообразомпоказаннойсхемыявляетсямакроячейкаCPLDXC9500фирмыXilinx,неимеющаяразделяемого(общего)логическогорасширителя.

Рис.1.ПримерсхемымакроячейкифункциональногоблокаCPLD

Программируемостьмультиплексороввэтойсхемеивсехдальнейшихнеотображается,т.к.онаприсущавсемимеющимсявсхемемультиплексорам,еслинеоговоренопротивоположное.Взависимостиотпрограммированиякаждыймультиплексорпередаетнавыходсигналстогоилииноговхода.

ТриггерможетпрограммироватьсянарежимыработытриггератипаDилиТ.Заметим,кстати,чтоприописаниимикросхемпрофаммируемойлогикитриггерывиностраннойлитературечащевсегоназываютрегистрами.ТриггерытактируютсяположительнымифронтамисинхросигналовиимеютвходыустановкиSисбросаR.ВыходныесигналыФБпередаютсявПМСивблокиввода/выводаБВВ.

Аргументых1,...,хМреализуемоймакроячейкойфункциипоступаютнаматрицуМиизПМС.АргументамидляМЯмогутбытькаквходныесигналы,поступающиеизвнечерезБВВ,такисигналыобратныхсвязей,подаваемыевматрицуИсвыходовмакроячеек.Нарис.1.входныесигналыматрицынезависимоотиххарактераобозначенычерезx1,...,хМ.Входныебуферыпреобразуютсигналывпарафазные,представляякаждыйсигналегопрямымиинверснымзначениями,такчтовматрицеимеется2твертикальныхлинийиобразующиеееконъюнкторыимеютпо1твходов.ПятьтермовизматрицыИпоступаютнаэлементИЛИдляобразованиялогическойфункции.Дляуправлениятриггеромибуферамиблокаввода/выводавырабатываютсятакжетермыPTSet,PTClock,PTReset,которыемогутбытьиспользованыкаксигналыустановки,синхронизацииисбросатриггера.ТермРТОЕ—программируемыйтермуправлениятретьимсостояниембуфераБВВ(ОЕ,OutputEnable).ВсеговматрицеИнарис.1.программируются9Nтермов.

НавыходеэлементаИЛИвырабатываетсялогическаяфункциявформеДНФранганеболеет.Еезначениепередаетсядальшечерезэлементсложенияпомодулю2,навторойвходкоторого,взависимостиотпрограммированиямультиплексора1,можетбытьподанлогическийнуль,логическаяединицаилитермРТ1.Впервомслучаефункцияпередаетсябезизменений(F=F*),вовтороминвертируется(F=!F*),втретьемпередаетсявпрямомвидевовсехситуацияхзаисключениемтакой,вкоторойРТ1=1.

МультиплексорMUX5программируетсядляпередачинавыходМЯлибонепосредственнозначенияфункцииF(комбинационныйвыход),либосостояниятриггера(регистровыйвыход).ХарактертактированиятриггераопределяетсяпрограммированиеммультиплексораMUX4,приэтомвозможноиспользованиеглобальногосинхросигнала(GCK,GlobalClock)илисигнала,порождаемоготермомPTClock.Асинхронныеустановкаисбростриггерапроизводятсялибоглобальнымсигналом(GSR,GlobalSet/Reset),либотермамиPTSetиPTReset,чтоопределяетсяпрограммированиеммультиплексоровMUX2иMUX3.Самтриггерпрограммируетсянарежимытриггеразадержки(типаD)илисчетного(типаТ).

ОсновнойвыходнойсигналмакроячейкипоступаеткаквПМС,котораяможетнаправлятьегополюбомутребуемомумаршруту,такивблокиввода/вывода.

Принципыпостроениявентильныхматриц(GA).Общаяклассификация.

Базовыематричныекристаллыназываюттакжевентильнымиматрицами(ВМ),чтосоответствуетпринятомудляБМКанглийскомутерминуGA(GateArray).ТерминБМКпреобладаетвотечественнойлитературеипоэтомуиспользуетсявэтойкниге,хотятермин"вентильнаяматрица"былбыпредпочтителенкакнепротиворечащиймеждународнойтерминологии.

Базовыематричныекристаллыизвестныс1975года,когдаамериканскаяфирмаAmdahlCorpприменилаихвсоставевысокопроизводительнойЭВМсцельюисключенияизнеемикросхеммалогоисреднегоуровнейинтеграции.Результатыоказалисьудачными,ивпоследующиегодыБМКполучилиширокоераспространение.

БМК—кристалл,напрямоугольнойповерхностикоторогоразмещенывнутренняяипериферийнаяобласти(ВОиПО).Вовнутреннейобластипострокамистолбцам(ввидематрицы)расположеныбазовыеячейки—группынескоммутированныхсхемныхэлементов(транзисторов,резисторов).

Элементныйсоставбазовойячейкиприразныхвариантахмежсоединенийэлементовдопускаетреализациюнекоторогомножествасхемопределенногокласса,каждаяизкоторыхсоответствуетопределеннойфункциональнойячейке(ФЯ).ДлявыпускаемоговпродажуБМКсоздаетсябиблиотекафункциональныхячеек,т.е.,всущности,рисунковмежсоединений,дающихтуилиинуюсхему.БиблиотекифункциональныхячеекБМКнасчитываютобычнодесяткиилисотнитиповыхузлов,реализованныхнаоднойилинесколькихбазовыхячейках.

ВБМКканальнойструктурымеждустрокамиистолбцамибазовыхячеекилиихкомпактныхгруппоставляютсягоризонтальныеивертикальныесвободныезоны(каналы)длямежсоединений.

Впериферийнойобластикристалларазмещаютсяпериферийныеячейки,выполняющиеоперацииввода/выводасигналовчерезконтактныеплощадки,расположенныепокраямкристалла.

ПереходотбиполярнойсхемотехникикМОП-транзисторнымсхемамсделалвозможнымболееплотноеразмещениесхемныхэлементовнакристалле.Приростесложностилогическойчастисхемы,т.е.числалогическихэлементовнакристалле,ещебыстреерастетсложностьмежсоединений.Длясниженияпотерьплощадикристалла,затрачиваемойнатрассировочныеканалы,быларазработанабесканальнаяструктураБМКтипа"моревентилей"или"моретранзисторов",вкоторойконструкторыотказалисьотсвободныхзонкристалла,заранееотведенныхдлямежсоединений.ВтакихБМКвсявнутренняяобластьплотнозаполняетсябазовымиячейками,амежсоединенияпроводятсятолькотам,гдеэтонеобходимо,причемнаходящиесяподнимибазовыеячейкиоказываютсявданнойконкретнойсхеменеиспользуемыми.

ЕщеоднойразновидностьюБМКявляютсяблочные,вкоторыхнакристаллевыделяютсяспециализированныеобласти-подматрицыдлявыполнениязаранееопределенныхфункций(логическойобработкиданных,памятиидр.).

Междуподматрицамиразмещаютсяспециальныетрассировочныеканалы,напериферииподматрицизготовляютсявнутренниепериферийныеячейкидляпередачисигналовпомежблочнымсвязям.

ИзобретениебазовыхматричныхкристалловозначалопоявлениеновогоклассаспециализируемыхБИС/СБИС—полузаказных.

ДляреализацииконкретнойполузаказнойсхемынаосновеБМК(такиесхемыназываютМАБИС,т.е.матричныеБИС,илиБИСМ,т.е.БИСматричные)нужнытолькошаблонырисунковмежсоединений.Например,привнедрениипервыхБМКвфирмеAmdahlCorpдлязаказныхсхемтребоваласьразработка13шаблонов,адляполузаказныхМАБИСтолькотрех.

Взаключениеотметим,чтодляболеечеткогоотраженияместаБМКвиерархиимикросхемполезнодополнитьанглийскуюаббревиатуруGAдоаббревиатурыMPGA,MaskProgrammableGateArray.

Заметимтакже,чтонарядусописаннымвышевариантомБМКсуществуютиБМКслазернымпрограммированиеммежсоединений(LPGA,LaserProgrammableGateArrays).ВэтихБМКпервоначальноизготовляютсяметаллизированнымидорожкамивсевозможныемежсоединенияэлементов,априпрограммированиичастьсоединенийподвоздействиемточносфокусированныхуправляемыхлазерныхлучейразрывается.ТакиеБМКподобныобычнымвтом,чтодляконфигурированияМАБИСпотребительдолженобращатьсякизготовителю,т.е.напредприятиеэлектроннойпромышленности,однакосрокиистоимостьвыполнениязаказавсравнениисобычнымиБМКоказываютсяиными.Срокивыполнениязаказасокращаются,чтоблагоприятносточкизренияускорениявыходапродукциинарынок,однаковнастоящеевремяБМКслазернымпрограммированиемраспространеныменьше,чемобычные,хотяимеютсяфирмы,развивающиеихпроизводство,вчастностифирмаChipExpress.

ПротоколJTAG.СтруктураТАР.

Термином JTAG обозначают совокупность средств и операций, позволяющих проводить тестирование БИС/СБИС без физического доступа к каждому ее выводу. Аббревиатура JTAG возникла по наименованию разработчика — объединенной группы по тестам JointTestActionGroup. Термином"периферийное сканирование" (ПС) или по-английски BoundaryScanTesting (BST) называют тестирование по JTAG стандарту (IEEE Std 1149.1).Такое тестирование возможно только для микросхем, внутри которых имеется набор специальных элементов — ячеек периферийного сканирования(ячеек ПС), в английской терминологии BSC (BoundaryScanCells) и схемуправления их работой.

Интерфейс JTAG проектировался для организации информационной связимежду произвольным количеством БИС на печатной плате, в приборе и т. д.Основное требование при этом состояло в минимизации числа контактовБИС, необходимого для организации информационного обмена. Обычноиспользуется четыре (реже пять) выделенных для JTAG -интерфейса контакта БИС. Эти контакты образуют так называемый порт доступа (TestAccessPort, TAP) контроллера управления портом доступа (ТАР Controller).

Контакты порта доступа:

· ТСК (TestClockInput) — синхронизация передачи данных и команд;

· TMS (TestModeSelect) — выбор режима передачи (считывание по переднему фронту СК);

· TDI (TestDataInput) — вход данных и команд (считывание по переднему фронту ТСК);

· TDO (TestDataOutput) — выход данных, команд или состояния (изменение по заднему фронту ТСК);

· TRST (TestReSeT) — сброс в исходное состояние контроллера (ТАР Controller).

CISC-процессоры

Complexinstructionsetcomputer—вычислениясосложнымнаборомкоманд.Процессорнаяархитектура,основаннаянаусложнённомнаборекоманд.ТипичнымипредставителямиCISCявляютсямикропроцессорысемействаx86.

CISC—концепцияпроектированияпроцессоров,котораяхарактеризуетсяследующимнаборомсвойств:

· нефиксированноезначениедлиныкоманды;

· арифметическиедействиякодируютсяводнойкоманде;

· небольшоечислорегистров,каждыйизкоторыхвыполняетстрогоопределённуюфункцию.

НедостаткиCISCархитектуры:

· высокаястоимостьаппаратнойчасти;

· сложностисраспараллеливаниемвычислений.

RISC-процессоры

Reducedinstructionsetcomputer—вычислениясупрощённымнаборомкоманд.Архитектурапроцессоров,построеннаянаосновеупрощённогонаборакоманд,характеризуетсяналичиемкомандфиксированнойдлины,большогоколичестварегистров,операцийтипарегистр-регистр,атакжеотсутствиемкосвеннойадресации.КонцепцияRISCразработанаДжономКокомизIBMResearch,названиепридуманоДэвидомПаттерсоном(DavidPatterson).

Упрощениенаборакомандпризваносократитьконвейер,чтопозволяетизбежатьзадержекнаоперацияхусловныхибезусловныхпереходов.Однородныйнаборрегистровупрощаетработукомпилятораприоптимизацииисполняемогопрограммногокода.Крометого,RISC-процессорыотличаютсяменьшимэнергопотреблениемитепловыделением.

СредипервыхреализацийэтойархитектурыбылипроцессорыMIPS,PowerPC,SPARC,Alpha,PA-RISC.ВмобильныхустройствахширокоиспользуютсяARM-процессоры.

MISC-процессоры

Minimuminstructionsetcomputer—вычислениясминимальнымнаборомкоманд.ДальнейшееразвитиеидейкомандыЧакаМура,которыйполагает,чтопринциппростоты,изначальныйдляRISC-процессоров,слишкомбыстроотошёлназаднийплан.Впылуборьбызамаксимальноебыстродействие,RISCдогналиперегналмногиеCISCпроцессорыпосложности.АрхитектураMISCстроитсянастековойвычислительноймоделисограниченнымчисломкоманд(примерно20-30команд).

VLIW-процессоры

VLIW(англ.verylonginstructionword—«оченьдлиннаямашиннаякоманда»)—архитектурапроцессоровснесколькимивычислительнымиустройствами.Характеризуетсятем,чтооднаинструкцияпроцессорасодержитнесколькоопераций,которыедолжнывыполнятьсяпараллельно.Фактическиэто«видимоепрограммисту»микропрограммноеуправление,когдамашинныйкодпредставляетсобойлишьнемногосвёрнутыймикрокоддлянепосредственногоуправленияаппаратурой.

Всуперскалярныхпроцессорахтакжеестьнескольковычислительныхмодулей,нозадачараспределениямеждунимиработырешаетсяаппаратно.Этосильноусложняетдизайнпроцессора,иможетбытьчреватоошибками.ВпроцессорахVLIWзадачараспределениярешаетсявовремякомпиляцииивинструкцияхявноуказано,какоевычислительноеустройстводолжновыполнятькакуюкоманду.ПримеромVLIW-процессораявляетсяIntelItanium.

Архитектура фон Неймана

Дж.фонНейманпридумалсхемупостройкикомпьютерав1946году.

ОтличительнойособенностьюархитектурыфонНейманаявляетсято,чтоинструкциииданныехранятсяводнойитойжепамяти.

Вразличныхархитектурахидляразличныхкомандмогутпотребоватьсядополнительныеэтапы.Например,дляарифметическихкомандмогутпотребоватьсядополнительныеобращениякпамяти,вовремякоторыхпроизводитсясчитываниеоперандовизаписьрезультатов.

Этапыциклавыполнения:

1.) Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса и отдаёт памяти команду чтения.

2.) Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных и сообщает о готовности.

3.) Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её.

4.) Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды.

Данныйциклвыполняетсянеизменно,иименноонназываетсяпроцессом(откудаипроизошлоназваниеустройства).

Вовремяпроцессапроцессорсчитываетпоследовательностькоманд,содержащихсявпамяти,иисполняетих.Такаяпоследовательностькомандназываетсяпрограммойипредставляеталгоритмработыпроцессора.Очерёдностьсчитываниякомандизменяетсявслучае,еслипроцессорсчитываеткомандуперехода,—тогдаадресследующейкомандыможетоказатьсядругим.Другимпримеромизмененияпроцессаможетслужитьслучайполучениякомандыостановкаилипереключениеврежимобработкипрерывания.

Командыцентральногопроцессораявляютсясамымнижнимуровнемуправлениякомпьютером,поэтомувыполнениекаждойкомандынеизбежноибезусловно.Непроизводитсяникакойпроверкинадопустимостьвыполняемыхдействий,вчастности,непроверяетсявозможнаяпотеряценныхданных.Чтобыкомпьютервыполнялтолькодопустимыедействия,командыдолжныбытьсоответствующимобразоморганизованыввиденеобходимойпрограммы.

Скоростьпереходаотодногоэтапациклакдругомуопределяетсятактовымгенератором.Тактовыйгенераторвырабатываетимпульсы,служащиеритмомдляцентральногопроцессора.Частотатактовыхимпульсовназываетсятактовойчастотой.

Суперскалярная архитектура

Способностьвыполнениянесколькихмашинныхинструкцийзаодинтактпроцессорапутемувеличениячислаисполнительныхустройств.Появлениеэтойтехнологиипривелоксущественномуувеличениюпроизводительности,втожевремясуществуетопределенныйпределростачислаисполнительныхустройств,припревышениикоторогопроизводительностьпрактическиперестаетрасти,аисполнительныеустройствапростаивают.

Гарвардская архитектура

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются:

1) Хранилище инструкций и хранилище данных представляют собой разные физические устройства.

2) Канал инструкций и канал данных также физически разделены.

Архитектура была разработана ГовардомЭйкеном в конце 1930-х годов в Гарвардском университете.

Классическаягарвардскаяархитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

· выборку двух операндов,

· выбор инструкции и её выполнение,

· и, наконец, сохранение результата.

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими.

Параллельная архитектура

АрхитектурафонНейманаобладаеттемнедостатком,чтоонапоследовательная.Какойбыогромныймассивданныхнитребовалосьобработать,каждыйегобайтдолженбудетпройтичерезцентральныйпроцессор,дажееслинадвсемибайтамитребуетсяпровестиоднуитужеоперацию.ЭтотэффектназываетсяузкимгорлышкомфонНеймана.

Дляпреодоленияэтогонедостаткапредлагалисьипредлагаютсяархитектурыпроцессоров,которыеназываютсяпараллельными.Параллельныепроцессорыиспользуютсявсуперкомпьютерах.

Возможнымивариантамипараллельнойархитектурымогутслужить(поклассификацииФлинна):

· SISD — один поток команд, один поток данных;

· SIMD — один поток команд, много потоков данных;

· MISD — много потоков команд, один поток данных;

· MIMD — много потоков команд, много потоков данных.

Типыцифровыхустройств.Определениепринадлежностиустройствакпервомуиливторомутипу.Примерыустройств,относящихсякпервомуивторомутипу.

Типыбазовыхцифровыхустройств(БЦУ):

· Комбинационныецифровыеустройства(КЦУ)

· Конечныеавтоматы(последовательностныесхемы)

КЦУ–этоустройства,неимеющиевсвоейструктуреобратныхсвязей.Вкаждыймоментвременисостояниевыходовзависитотвходноговоздействия(памятьотсутствует).КЦУописываютсяпростымилогическимиуравнениями,всеаргументыкоторых–входныезначения.Такиеустройстваслужатдляпреобразованияинформацииидлякоммутации.ОтсюдадватипаКЦУ:кодопреобразующиеикоммутационные.

ВсеКЦУстроятсяметодомпростогосинтезапозаданнойтаблицефункционированияилипологическомууравнению,заданномувканоническойформе.

КкодопреобразующимКЦУотносятсясумматоры,кодопреобразователи,шифраторыидешифраторы.

КкоммутационнымКЦУотносятсямультиплексорыидемультиплексоры.

Конечныеавтоматы–устройства,содержащиевсвоейструктуреобратныесвязи(ОС).Такимобразом,вкаждыймоментвременисостояниевыходовзависитнетолькоотвходноговоздействия,ноиотсостояниявыходавпредыдущиймоментвремени.Онислужатдляхраненияинформациииеепреобразованиясучетомпредыдущегосостояния.

ОднастепеньОСпозволяетхранитьинформацию–этосвязьвнутрипростейшейячейки.ВтораястепеньОСпозволяетпреобразовыватьинформацию.Этосвязимеждупростейшимиячейками.Простейшейячейкойилипростейшимконечнымавтоматомявляетсятриггер.

Устройства–триггеры,счетчики,регистры.

Комбинационныецифровыеустройства.Шифраторидешифратор.Определение,принципфункционирования.

Шифратор–устройство,определяющееадреснаправления,покоторомупоступилзапрос.

ТакоеустройствоимеетNвходов(x0…xN-1)иMвыходов(A0…AM-1).Вкаждыймоментвремениактивнымможетбытьтолькоодинвход.Навыходахприэтомпоявляетсядвоичнаякомбинация,соответствующаяадресуактивноговхода.  –дляполнодоступногошифратораи

–дляполнодоступногошифратораи  –длянеполнодоступного.Неполнодоступнымшифраторомназываетсяустройство,имеющееколичествовходовнекратноестепенидвух.

–длянеполнодоступного.Неполнодоступнымшифраторомназываетсяустройство,имеющееколичествовходовнекратноестепенидвух.

Еслинавходахпоявитсяколичествоактивныхуровней>1или<1,тосостояниевыходовнеопределено.

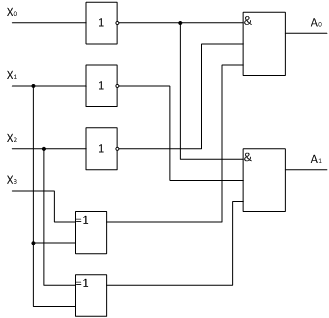

Пример:шифраторна4входа.

Таблицафункционированиятакогоустройстваприусловииактивногоуровня«1»

| X3 | X2 | X1 | X0 | A1 | A0 |

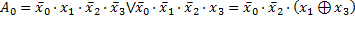

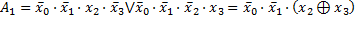

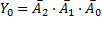

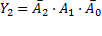

ИзтаблицывыводимвыражениядляA0иA1:

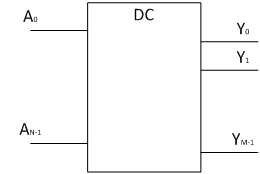

Дешифратор–устройство,посылающеезапроспонаправлению,адрескоторогоустановленнавходах.ТакоеустройствоимеетNадресныхвходов(A0…AN-1)иMвыходов(y0…yM-1).

Вкаждыймоментвремениактивныйуровеньможетпоявитьсятольконаодномвыходе,адрескотороговвидедвоичнойкомбинацииустановленнаадресныхвходах.Дляполногодешифратораколичествовыходов  ,длянеполного–

,длянеполного–  .

.

Вкачествепримерарассмотримсинтездешифраторанатриадресныхвхода.

Таблицафункционирования

| A2 | A1 | A0 | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 |

Изтаблицы:    |