Представление двоичных чисел в ЭВМ.

Для представления разрядов двоичных чисел в ВМ с помощью импульсов применяют 2 способа (рис. 2.14).

|

Статический способ[5]: двоичные цифры изображаются уровнями напряжения, которые сохраняются в течение всего времени следования данной цифры. При этом обычно для изображения «1» используется высокий уровень сигнала, а для изображения «0» -низкий.

Динамический способ: двоичные цифры изображаются импульсами определённой длительности. Обычно «1» изображается наличием импульса, а для «0» -отсутствием

Наибольшее распространение получил статический способ, как более надёжный в работе.

1.10.2. Способы передачи информации в ВМ.

Для передачи информации используются три способа, они представлены на рис 2.15.

Параллельный способ передачи информации. Параллельный код отображения и передачи информации предполагает параллельную и одновременную фиксацию всех разрядов данных на различных шинах, т.е. параллельный код данных развернут в пространстве. Это дает возможность ускорить обработку во времени, но затраты на аппаратурные средства (количество каналов) при этом возрастают пропорционально числу обрабатываемых разрядов.

|

При последовательном способе представления данных используются одиночные шины или линии передачи, в которых сигналы, соответствующие отдельным разрядам данных, разнесены во времени. Обработка такой информации производится последовательно разряд за разрядом. Разряды должны поступать в строго определённые моменты времени. Отметки времени прохождения каждого числа задаются специальными синхронизирующими импульсами. Такой вид представления и передачи данных требует весьма экономичных по аппаратурным затратам схем обработки данных. Время обработки определяется числом обрабатываемых сигналов (разрядов).

Недостатки обоих способов сказываются тем сильнее, чем больше разрядность числа, поэтому во всех вычислительных машинах чаще всего применяют последовательно-параллельный способ, при котором число разбивается на группы и передаётся отдельными группами. Группы поступают на обработку последовательно, разряды каждой группы передаются параллельно.

1.11. Вентили, интегральные схемы.

Основные элементы, из которых конструируются цифровые компьютеры, чрезвычайно просты. Цифровые схемы могут конструироваться из небольшого числа простых элементов в различных комбинациях.

Цифровая схема – это схема, в которой определены только два логических состояния. Обычно сигнал от 0 до 1вольта представляет одно значение (например, 0), а сигнал от 2 до 5 вольт – другое значение (например, 1). Напряжение за пределами указанного диапазона недопустимо. Крошечные электронные устройства - вентили могут вычислять различные функции от этих двух сигналов.

Логический элемент ВМ(вентиль) – это часть электронной логической схемы, которая реализует элементарную логическую функцию.

Все узлы ВМ реализованы с помощью логических элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. В таблице 2.1 приведены условные изображения 5 основных вентилей и таблицы истинности для каждого вентиля. С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств ЭВМ. Вентили характеризуются не состоянием контактов, а наличием сигналов на входе и выходе элемента. Из вентилей составляют более сложные схемы, которые позволяют выполнять арифметические операции и хранить информацию. Алгебра логики (булева алгебра) является средством разработки, анализа и совершенствования логических схем.

Логический элемент на схеме изображается прямоугольником, линии с левой стороны элемента представляют собой входы данного элемента, а с правой выходы. Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности – это табличное представление логической схемы (операции), в которой перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

Табл. 2.1

| Логический элемент | Обозначение на схеме | Таблица истинности | Название схемы | ||||||||||||||||||

| А | В | X | |||||||||||||||||||

| И |

| схема совпадения, конъюнкция | |||||||||||||||||||

| ИЛИ |

| собирательная схема, дизъюнкция | |||||||||||||||||||

| НЕ |

| - - | инвертор | ||||||||||||||||||

| И - НЕ |

| исключающее И | |||||||||||||||||||

| ИЛИ - НЕ |

| исключающее ИЛИ |

Пять вентилей составляют основу цифрового логического уровня. Вентили И–НЕ, ИЛИ–НЕ требуют два транзистора каждый, а вентили И и ИЛИ – три транзистора каждый. По этой причине во многих компьютерах используются вентили И–НЕ, ИЛИ–НЕ.

/При производстве вентилей используются две основные технологии – биполярная и МОП(металл – оксид - полупроводник). Среди биполярных технологий можно назвать ТТЛ (транзисторно – транзисторную логику), котрая служила основой цифровой электроники на протяжении многих лет, и ЭСЛ (эммитерно - связанную логику), которая используется при требовании высокой скорости выполнения операции.

Вентили МОП работают медленнее, чем ТТЛ и ЭСЛ, но потребляют гораздо меньше энергии, занимают значительно меньше места, поэтому можно компактно расположить большое количество таких вентилей. Современные процессоры и память производятся с использованием технологии комплементарных МОП./

На практике схемы очень редко конструируются вентиль за вентилем. Сейчас стандартные блоки представляют собой модули, которые содержат ряд вентилей. Модули называются интегральными схемами (ИС) или микросхемами./*. Все современные вычислительные машины строятся на комплексах интегральных микросхем.*/ Электронная микросхема называется интегральной, если ее компоненты и соединения между ними выполнены в едином технологическом цикле, на едином основании и имеют общую герметизацию и защиту от механических воздействий. Каждая микросхема представляет собой миниатюрную электронную схему, сформированную послойно в кристалле полупроводника/* (квадратную пластину кремния размером примерно 5х5 мм, на котором находится несколько вентилей). Маленькие интегральные схемы помещаются в прямоугольные пластиковые или керамические корпуса размером от 5 до 15 мм в ширину и от 20 до 50 мм в длину. Вдоль длинных сторон располагается два параллельных ряда выводов около 5 мм в длину, которые можно втыкать в разъемы или впаивать в печатную плату. Каждый вывод соединяется с входом или выходом какого - нибудь вентиля, или с источником питания, или с «землей». Большинство корпусов имеют 14, 16, 18, 20, 22, 24, 40, 64 или 68 выводов. Для больших микросхем часто используются корпуса, у которых выводы расположены со всех четырех сторон или снизу.

В состав микропроцессорных наборов включаются различные типы микросхем, но все они должны иметь единый тип межмодульных связей, основанный на стандартизации параметров сигналов взаимодействия (амплитуда, полярность, длительность импульсов и т.п.).

Микросхемы можно разделить на несколько классов с точки зрения количества вентилей, которые они содержат:

§ МИС (малая интегральная схема): от 1 до 10 вентилей;

§ СИС (средняя интегральная схема): от 1 до 100 вентилей;

§ БИС (большая интегральная схема): от 100 до 100 000 вентилей;

§ СБИС (сверхбольшая интегральная схема): более 100 000 вентилей.

В настоящее время стало возможным помещать до 10 млн транзисторов на одну микросхему. Стандартный вывод имеет определенную физическую ширину, то микросхема с выводами всех вентилей должна иметь колоссальные размеры (несколько километров). Поэтому разрабатываются схемы, у которых число вентилей, значительно превышает количество выводов, группы вентилей объединены для вычисления некоторой функции. */

Функционально микросхемы могут соответствовать устройству, узлу или блоку, но каждая из них состоит из комбинации простейших логических элементов, реализующих функции формирования, преобразования, запоминания сигналов и т.д.

Основные элементы ВМ

Архитектурой компьютера считается его представление на некотором общем уровне, включающее описание пользовательских возможностей программирования, системы команд, системы адресации, организации памяти и т.д. Архитектура определяет принципы действия, информационные связи и взаимное соединение основных логических узлов компьютера. Общность архитектуры разных компьютеров обеспечивает их совместимость с точки зрения пользователя.

При рассмотрении структуры любой ВМ обычно проводят ее детализацию. Как правило, в структуре ВМ выделяют следующие структурные единицы: устройства, узлы, блоки и элементы. Такая детализация соответствует вполне определенным операциям преобразования информации, заложенным в программах пользователей.

Нижний уровень обработки реализуют элементы. Каждый элемент предназначается для обработки единичных электрических сигналов, соответствующих битам информации. Элементы образуют узлы. Они обеспечивают одновременную обработку группы сигналов - информационных слов. Блоки реализуют некоторую последовательность в обработке информационных слов - функционально обособленную часть машинных операций (блок выборки команд, блок записи-чтения и др.). Устройства предназначаются для выполнения отдельных машинных операций и их последовательностей.

По своему назначению элементы делятся на формирующие, логические и запоминающие.

К формирующим элементам относятся различные формирователи, усилители, усилители-формирователи и т.п. Данные элементы служат для выработки определенных электрических сигналов, восстановления их параметров (амплитуды, полярности, мощности, длительности).

В каждой ВМ имеются специальные блоки, формирующие сигналы тактовой частоты, серии синхронизирующих и управляющих сигналов, координирующих работу всех схем ВМ. Интервал времени между импульсами основной частоты называется тактом. Длительность такта является важной характеристикой ВМ, определяющей ее потенциальную производительность. Время выполнения любой операции ВМ связано с определенным числом тактов.

Простейшие логические элементы преобразуют входные сигналы в соответствии с элементарными логическими функциями. В свою очередь, полученные сигналы могут формировать следующий уровень сигналов и т. д. Сложные преобразования в соответствии с требуемыми логическими зависимостями могут приводить к построению многоуровневых схем. Каждая такая схема представляет собой композицию простейших логических схем.

Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры (единицы или нуля). Элементы памяти могут запоминать и сохранять исходные значения некоторых величин, промежуточные значения обработки и окончательные результаты вычислений. Только запоминающие элементы в схемах ВМ позволяют проводить обработку информации с учетом ее развития.

В самом низу иерархической схемы построения компьютера находится цифровой логический уровень. Рассмотрим основные элементы, из которых конструируются компьютеры.

Триггер.

Триггер– это устройство, которое имеет два устойчивых состояния. В одном из устойчивых состояний триггер может находиться неограниченно долгое время, до тех пор, пока на него не воздействует другой входной сигнал. При поступлении такого сигнала триггер (Тг) скачком переходит в другое устойчивое состояние. В вычислительной технике одно устойчивое состояние условно принимается за 1, а другое за 0. 29.10

Способность триггера устойчиво сохранять свое состояние сделало возможным использовать триггер в качестве простейшего запоминающего элемента (ЗЭ). Схемы с памятью являются сложными преобразователями информации. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. В связи с успешным применением микроэлектроники в схемах основных устройств ВМ (процессоров и оперативной памяти) исчезли в качестве запоминающихся элементов схемы, использующие остаточную намагниченность, - ферритовые сердечники.

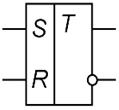

В общем случае триггер должен иметь вход R (Reset - сброс) для установки элемента в "нулевое состояние" и вход S (Sеt - установка) - для установки элемента в "единичное" состояние. При отсутствии сигналов R=S=0 элемент должен сохранять свое состояние до тех пор, пока не будут получены новые сигналы на входе R или S. Условия работы триггера могут быть представлены в виде таблицы переходов (табл. 2.2), представляющей собой модификацию таблицы истинности.

Табл. 2.2 Условия работы триггера

| R | S | Q | _ Q |

| Хранение бита | |||

| Запрещено |

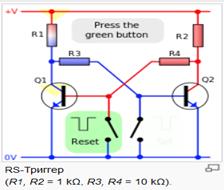

RS-триггер нашел широкое распространение в схемах ВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения (см. табл. 2.2), т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-триггеры, Т-, JK-, D- триггеры и целый ряд комбинированных RST-, JKRS-, DRS-триггеров.

Прописные буквы в названиях триггеров обозначают:

• R (Reset - сброс) - вход установки триггера в нулевое состояние Q=0;

• S (Set - установка) - вход установки триггера в единичное состояние 0=1;

• Т (Toggle - релаксатор) - счетный вход триггера;

• J (Jerk - внезапное включение) - вход установки JK-триггера в единичное состояние Q=1;

• К (Kill - внезапное выключение) - Q=0;

• D (Delay - задержка) - вход установки триггера в единичное или нулевое состояние на время, равное одному такту.

Двухкаскадная схема RS-триггера нашла наиболее широкое применение для построения n-разрядных схем запоминания - всевозможных регистровых схем. Наиболее сложным типом триггера является JK-тригтер. Он, по существу, является объединением двухтактного RS- и Т-триггеров.

D-триггер обычно строится на основе двухтактного RS- или JK-тригера. Он предназначается для хранения состояния (1 или 0) на один период тактовых импульсов (с задержкой на 1 такт). Все перечисленные элементы памяти позволяют хранить одну единицу информации - бит или одну двоичную цифру.

Рассмотрим подробнее RS триггер. Триггер имеет два симметричных входа (R,S) и два симметричных выхода (Q,Q), триггер может быть выполнен на двух вентилях ИЛИ-НЕ либо И-НЕ.

Состояние выходов триггера зависит от того, в какой последовательности на входы подаются комбинации входных сигналов, каково было предшествующее состояние триггера.

Переходы триггера из исходного состояния (в триггер записан 0) в состояние записи 1 в триггер, а затем сброса 1 в триггере описаны в табл. 2.3. Состояние выхода Q рассматривается в текущий момент времени t (на входе триггера появился единичный сигнал) и последующий момент времени t+1 (время, необходимое для перехода триггера в устойчивое состояние). Табл. 2.3

| № состояния | Входы | Выход | Состояние триггера | ||

| R | S | Qt | Q t+1 | ||

| Исходное, в Тг записан 0 | |||||

| Запись 1, подача сигнала на запись S | |||||

| Хранение 1, сняли сигнал записи 1 | |||||

| 4[6] | Повторная запись 1, подача сигнала записи | ||||

| Выдача сигнала на сброс 1, подача сигнала сброс | |||||

| Переход в исходное состояние, сохранение 0 | |||||

| Повторная запись 0, подача сигнала сброс | |||||

| - | - | Состояние неустойчивое, неопределенно |

Содержание таблицы расшифровывается следующим образом. Элемент памяти может сохранять значение Qt=0 или Qt=1 в зависимости от установки ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R =0 и S =0) значения Qt+1 1 и 6 строк таблицы в точности повторяют значения Qt .При поступлении сигнала R=l (сигнала установки "нуля") элемент независимо от своего состояния принимает значение, равное нулю, Qt+1=0 (состояния 5, 7). Если же на вход S поступает сигнал установки "единицы" (S=1), то Qt+1=1 независимо от предыдущего состояния Qt. Одновременное поступление сигналов на входы R и S является запрещенной ситуацией, так как она может привести к непредсказуемому состоянию. В схемах формирования сигналов R и S должны быть предусмотрены блокировки, исключающие их совпадения, S=R=1.

На рис. 2.16 приводятся схемы RS триггера на основе вентилей ИЛИ-НЕ для состояний 1 и 5 с учетом переходных процессов в триггере. Рассмотрим эти состояния более подробно.

Состояние 1 - запись 1 в триггер:

a)исходное состояние - S=R=Qt=0, Qt=1;

b)в момент времени t на вход триггера подается сигнал S=1;

в момент времени t+1 на выходе вентиля ИЛИ-НЕ со входами S=1, Qt= 0 после выполнения логической операции ИЛИ-НЕ появляется 0, т.е. Qt+1=0 (стрелка 1) на рис.2.16);

c)на выходе вентиля ИЛИ-НЕ со входами R= Qt+1= 0 после выполнения логической операции ИЛИ-НЕ появляется 1, т.е. Qt+1 =1 (стрелка 2) на рис.2.16 );

| Исходное состояние, момент времени t | Момент времени t+1 | |||||||||||||||||||||||||

|

| |||||||||||||||||||||||||

|

|

|

С

Состояние 5- запись 0 в триггер:

a)исходное состояние - S=R= Qt=0, Qt=1;

b)в момент времени t на вход триггера подается сигнал R=1;

c)в момент времени t+1 на выходе вентиля ИЛИ-НЕ со входами R=1, Qt= 0 после выполнения логической операции ИЛИ-НЕ появляется 0, т.е. Qt+1=0 (стрелка 3) на рис.2.16);

d)на выходе вентиля ИЛИ-НЕ со входами S=Qt+1= 0 после выполнения логической операции ИЛИ-НЕ появляется 1, т.е. Qt+1 =1 (стрелка 4) на рис.2.16).

Передача значения Q между моментами времени t и (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ).

Регистры.

При построении ВМ широко используются функциональные схемы, обеспечивающие операции хранения и преобразования информации над группами битов (машинными словами). Такие сложные схемы называются узлами. К типовым узлам относят: регистры, счетчики, сумматоры. Все они также принадлежат к регулярным структурам, состоящим из одинаковых параллельно работающих одноразрядных схем.

Регистры самые распространенные узлы ЭВМ.

Регистром называют узел, предназначенный для приема, временного хранения и выдачи одного машинного слова.

Регистры используются также для выполнения некоторых операций над словами: сдвиг слова на определенное число разрядов вправо или влево, образование обратного кода числа, выполнение логических операций над несколькими словами, преобразование последовательного кода слова в параллельный и обратно, ряд других операций. Эти дополнительные функции регистров обеспечиваются путем усложнения схем хранения, выбора более сложных триггеров и подключения дополнительных логических схем на их входах и выходах.

Регистры строятся на различных элементах, имеющих два устойчивых состояния, чаще всего это триггера. Таким образом, регистры представляют собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение различных операций над словом.

Регистры классифицируются по способам приема и выдачи данных, по количеству каналов передачи слов (парафазные - передается прямой и обратный код каждого разряда числа и однофазные - передается один из кодов числа), по способу тактирования (однотактные и многотактные).

По способам приема и выдачи данных регистры делятся на:

· параллельные(статические). В них прием и выдача слов производятся по всем разрядам одновременно по собственным шинам для каждого разряда. Основная функция - хранение слова, поразрядные операций над словами;

· последовательные (сдвигающие). В них слова принимаются и выдаются разряд за разрядом, их называют сдвигающими, поскольку тактирующие сигналы перемещают слова в разрядной сетке;

· последовательно- параллельные регистры имеют одновременно входы последовательного и параллельного приема (выдачи) слов и могут выполнять взаимные преобразования последовательных кодов в параллельные и наоборот.

Рассмотрим схему параллельного парафазногорегистра, используемого для запоминания двоичного трехразрядного числа рис. 2.17.

Регистр состоит из триггерных ячеек и схем совпадений, которые служат для управления приемом и выдачей числа. Каждая триггерная ячейка предназначена для запоминания одного разряда числа. Предварительно перед установкой кода на регистр на все разряды входов R триггеров подается сигнал сброса (Установ «0»), переводящий все триггеры в состояние «0» (очистка регистра). Информация в регистр записывается под действием сигнала «Запись», подаваемого на один из входов схем &1, на второй вход схем &1 подаются разряды числа Xi, представленные высокими (1) и низкими (0) потенциалами (наличие или отсутствие импульса). С поступлением импульса приема числа (записи) открываются те схемы &1, на входы которых подан высокий потенциал, и соответствующие триггеры переходят в состояние «1».

Регистр состоит из триггерных ячеек и схем совпадений, которые служат для управления приемом и выдачей числа. Каждая триггерная ячейка предназначена для запоминания одного разряда числа. Предварительно перед установкой кода на регистр на все разряды входов R триггеров подается сигнал сброса (Установ «0»), переводящий все триггеры в состояние «0» (очистка регистра). Информация в регистр записывается под действием сигнала «Запись», подаваемого на один из входов схем &1, на второй вход схем &1 подаются разряды числа Xi, представленные высокими (1) и низкими (0) потенциалами (наличие или отсутствие импульса). С поступлением импульса приема числа (записи) открываются те схемы &1, на входы которых подан высокий потенциал, и соответствующие триггеры переходят в состояние «1».

Для чтения числа, записанного в регистре в прямом коде, на входы схем совпадения &3 ,подключенных к выходам Q триггеров, подается импульс выдачи числа («Чтение прямой код»). При этом сигналы, соответствующие коду «1», появляются на выходах тех схем совпадений &3 , на которые подаются высокие потенциалы с выходов триггеров, находящихся в единичном состоянии. При подаче сигнала « Чтение обратный код» на входы схем совпадения &2 число снимается в обратном коде. Если оба эти сигнала поступают одновременно, то считывается парафазный код хранящейся информации.

Более сложная логика на входе и выходе запоминающих элементов позволяет строить сдвигающие регистры.

Сумматоры

Сумматор – это основная часть АЛУ, которая служит для сложения чисел.

Суммирование производится на основании правил поразрядного сложения с учетом переноса 1 в старшие разряды. Перенос возникает, если сумма двух цифр равна или превышает основание системы счисления.

| Переносы | 1*1* 1** | * - сумма двух цифр равна основанию СС; **- сумма двух цифр превышает основание СС. |

| 1-ое слагаемое | 1 0 1 1 | |

| 2-ое слагаемое |  0 1 1 1 0 1 1 1 | |

| Сумма | 1 0 0 1 0 |

Следовательно, при построении сумматора следует учитывать возникновение переноса в следующий разряд и получение 1 переноса из предыдущего разряда.

Сумматоры делятся на два основных типа:

· комбинационные(последовательные и параллельные). Сумматоры данного типа не содержат запоминающих элементов, реализуют микрооперацию сложения в виде:С = А+В. Используются наиболее часто для построения сумматоров. Обычно у такого сумматора на входе и выходе имеются регистры для хранения и преобразования кодов операндов и результата;

· накапливающие. Сумматоры данного типа имеют память, в которой аккумулируют результаты суммирования так, что очередное слагаемое добавляется к результату, содержащемуся в регистре-аккумуляторе, т.е. накапливающий сумматор реализует микрооперацию сложения в виде: С = С+А. Сумматоры накапливающего типа строят на сложных JKRS-триггерах, дополняя их выходы достаточно сложными схемами формирования и распространения переносов. Процесс сложения при этом осуществляется поэтапно. Сначала на триггерах сумматора фиксируется код первого операнда, затем на счетные коды разрядов подается код второго операнда. На каждом триггере формируются одноразрядные суммы и значения переносов между разрядами. Учет возникающих переносов задерживает формирование окончательного результата суммы и может требовать дополнительных тактов сложения. Из-за этого многоразрядные схемы сумматора накапливающего типа используются достаточно редко.

| |||

| |||

Условное изображение сумматора на 3 входа приведено на рис.2.18 на нем приняты следующие обозначения:

ai – цифра i-ого разряда I –ого слагаемого;

bi - цифра i-ого разряда II–ого слагаемого;

pi-1- цифра переноса из предыдущего разряда;

pi- - цифра переноса в следующий разряд;

Si - цифра суммы i-ого разряда.

Рассмотрим схему комбинационного сумматора параллельного действия (рис.2.19). Сумматор параллельного действия содержит количество одноразрядных суммирующих схем равное количеству разрядов суммируемых чисел.

|

|

Достоинство: высокое быстродействие (причем у асинхронных сумматоров выше чем у синхронных).

Недостаток: схема дорогостоящая из-за большого количества сумматоров.

1.12.4. Счетчики.

Счетчик - узел ЭВМ, позволяющий осуществлять подсчет поступающих на его вход сигналов и фиксацию результата в виде многоразрядного двоичного числа. Счетчик, состоящий из n-триггеров, дает возможность подсчитывать до N сигналов, связанных зависимостью: n = log2 N или N = 2n.

Содержимое счетчика изменяется на единицу после прихода очередного импульса на вход. В ВМ счетчики используются для подсчета импульсов, сдвигов, формирования адресов, учета количества циклов при выполнении программы, подсчета количества шагов при выполнении операций умножения деления и т.д. Функционально различают суммирующие, вычитающие, реверсивные счетчики.

Счетчик , на котором реализуется микрооперация счета вида С = С + 1, называется суммирующим .

Если на счетчике реализуется микрооперация счета вида С = С - 1 ,то счетчик называется вычитающим.

Счетчик, на котором реализуются обе указанные операции, называется реверсивным.

Счетчики отличаются друг от друга логикой работы дополнительных логических элементов, подключаемых к триггерам. В основу построения любого счетчика положено свойство Т-триггеров (триггер со счетным входом) изменять свое состояние при подаче очередного сигнала на счетный вход Т.

| |||

|

На рис.2.20 показана схема трех разрядов суммирующего счетчика, построенного на Т-триггерах. Логика его работы представлена в табл. 2.4.

Таблица 2.4 Таблица переходов трехразрядного счетчика

| Вход х | Состояние | ||||||||

| Режим | |||||||||

| Хранение Счет |

1.12.5. Шифраторы и дешифраторы.

Для выполнения операций кодирования, т.е. преобразования поступающей информации в двоичную форму, и декодирования – преобразование информации в первоначальную форму, в ЭВМ используются избирательные комбинационные схемы, которые называются шифраторами и дешифраторами. На рис.2.21 приводятся обозначение дешифратора и шифратора на принципиальных электрических схемах.

|

Дешифратор - логическое устройство, преобразующее обыкновенный двоичный код в унитарный (позиционный).

Унитарный код - двоичная последовательность 0, за исключением 1 в одной из позиций. Номер позиции соответствует кодируемому числу.

Дешифратор является преобразователем кода. Дешифратор имеет n входов и 2n выходов. Каждому набору на входе соответствует только одно возбуждение на выходе. Дешифраторы широко используются в ВМ для выбора информации по определенному адресу, для расшифровки кода операции и др.

Дешифраторы могут быть линейными и многокаскадными. Простейший линейный дешифратор можно построить на диодной матрице.

Шифраторы кодируют информацию, т.е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов. Полный двоичный шифратор имеет 2n входов и n выходов.Одно из основных применений шифратора – ввод данных с клавиатуры, при котором нажатие клавиши с десятичной цифрой должен приводить к передаче в устройство двоичной цифры (тетрады двоично-десятичного кода). Процесс шифрования описывается таблицей истинности (табл. 2.4) и логическими зависимостями.

Таблица 2.5

Таблица функционирования шифратора.

| Возбужденный вход | Выход | |||

| а3 | а2 | а1 | а0 | |

| F0 | ||||

| F1 | ||||

| F2 | ||||

| F3 | ||||

| F4 | ||||

| F5 | ||||

| F6 | ||||

| F7 | ||||

| F8 | ||||

| F9 |

Выходы шифратора описываются логическими формулами по наличию единицы:

а0=F1 V F3 V F5 V F7 V F9; а1=F2 V F3 V F6 V F7;

а2=F4 V F5 V F6 V F7; а3= F8 V F9.

Основываясь на описании выходов, построим схему шифратора (рис.2.22).

Тактовые генераторы.

Во многих цифровых схемах всё зависит от порядка, в котором выполняются действия. Для обеспечения синхронизации работы цифровых схем используются тактовыегенераторы – это схемы, которые вызывают серию импульсов. Все импульсы одинаковы по длительности. /*Интервалы между последовательными импульсами также одинаковы. */ Временной интервал между началом одного импульса и началом следующего называется временем такта. Частота импульсов от 1 до 500 МГц (время такта от 1000 нс до 2 нс). Частота тактового генератора обычно контролируется кварцевым генератором.

| |||||||