Обработка прерываний в персональной ЭВМ.

Микропроцессоры типа х86 имеют два входа запросов внешних аппаратных прерываний:

NMI – немаскируемое прерывание, используется обычно для запросов прерываний по нарушению питания;

INT – маскируемое прерывание, запрос от которого можно программным образом замаскировать путем сброса флага IF в регистре флагов.

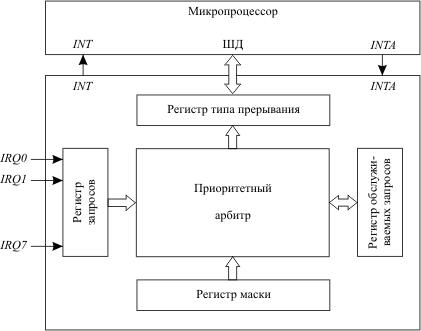

Единственный вход запроса маскируемых прерываний микропроцессора не позволяет подключить к нему напрямую сигналы запросов от большого числа различных внешних устройств, которые входят в состав современного компьютера: таймера, клавиатуры, "мыши", принтера, сетевой карты и т.д. Для их подключения к одному входу INT микропроцессора используется контроллер приоритетных прерываний (рис. 8). Его функции:

· восприятие и фиксация запросов прерываний от внешних устройств;

· определение незамаскированных запросов среди поступивших запросов;

· проведение арбитража: выделение наиболее приоритетного запроса из незамаскированных запросов в соответствии с установленным механизмом назначения приоритетов;

· сравнение приоритета выделенного запроса с приоритетом запроса, который в данный момент может обрабатываться в микропроцессоре, формирование сигнала запроса на вход INT микропроцессора в случае, если приоритет нового запроса выше;

· передача в микропроцессор по шине данных типа прерывания, выбранного в процессе арбитража, для запуска соответствующей программы-обработчика прерывания; это действие выполняется по сигналу разрешения прерывания INTA от микропроцессора, который выдается в случае, если прерывания в регистре флагов микропроцессора не замаскированы (IF=1).

Рис. 8. Структура контроллера приоритетных прерываний

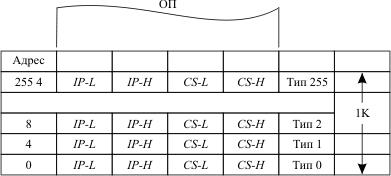

Переход к соответствующему обработчику прерывания осуществляется (в реальном режиме работы микропроцессора) посредством таблицы векторов прерываний. Эта таблица (рис. 9) располагается в самых младших адресах оперативной памяти, имеет объем 1 Кбайт и содержит значения сегментного регистра команд (CS) и указателя команд (IP) для 256 обработчиков прерываний.

Рис. 9. Структура таблицы векторов прерываний

Обращение к элементам таблицы осуществляется по 8-разрядному коду – типу прерывания.

| Тип прерывания | Источник прерывания |

| Деление на 0 | |

| Пошаговый режим выполнения программы | |

| Запрос по входу NMI | |

| · · · | |

| Запрос по входу IRQ0 (системный таймер) | |

| Запрос по входу IRQ1 (контроллер клавиатуры) | |

| · · · | |

| Отсутствие сегмента в оперативной памяти | |

| · · · | |

| Пользовательское прерывание |

Различные источники задают тип прерывания по-разному:

· программные прерывания вводят его изнутри процессора или содержат его в номере команды INT n;

· аппаратные маскируемые прерывания вводят его от контроллера приоритетных прерываний по шине данных;

· немаскируемому аппаратному прерыванию назначен тип 2.

Память (Лекция 6)

Определения

Младшими адресами памяти называется часть памяти компьютера (с самыми младшими адресами), которая отводится для некоторых важных применений, определяющих функционирование компьютера. В специальном применении младшей области памяти можно выделить три области:

1. Таблица векторов прерываний, которая определяет местоположение подпрограмм обработки прерывания. Первые 1024 байтов памяти специально отводятся для таблиц векторов прерываний, предусматривается место для 256 различных прерываний – несколько больше, чем обычно используется. Эти таблицы занимают область памяти с абсолютными адресами от 0 до 400 (значение шестнадцатеричное).

2. Рабочее места для подпрограмм ROM-BIOS. Поскольку ROM-BIOS управляет основной деятельностью компьютера и составляющих его компонент, то для хранения его собственных записей требуется определенная область памяти. Такой областью является область данных ROM-BIOS. Среди всего того многого, что хранится в области данных ROM-BIOS, имеется буфер, в котором хранится информация о клавишах, нажатых до того, как наши программы готовы принять такую информацию, а также информация об объеме имеющейся памяти в компьютере и индикатор режима использования. Для области данных ROM-BIOS устанавливается отдельная область размером в 256 байтов и с адресами от 400 до 500.

3. Рабочая область операционной системы, которая находится между абсолютными адресами 500 и 600. Эта область используется ей в качестве рабочей области, аналогично рабочей области ROM-BIOS, которая предшествует ей.

Ключевой рабочей областью памяти является та часть, которая используется для программ и соответствующих данных: эта область состоит из первых десяти блоков (0-9). Эту область часто называют областью памяти пользователя для того, чтобы отличать ее от остальной части адресного пространства. Когда мы говорим об объеме имеющейся в PC памяти, фактически речь идет об объеме памяти пользователя, которая устанавливается в этой области. Память пользователя может иметь размеры от 16К (четвертая часть первого блока в 64К) до 640К.

Тот вид памяти, который определяется здесь, является обычной памятью с произвольным доступом. Она используется для выполнения чтения и записи и называется также RAM. Память эту отличает следующее: во-первых, данные, хранящиеся в этой памяти, могут изменяться (записываться), а, во-вторых, эта память непостоянна, что означает, что данные, хранящиеся в ней, сохраняются только на время работы компьютера. Эта память предназначена для хранения программ и данных, пока компьютер обрабатывает их. Объем установленной памяти RAM во многом определяет размер и диапазон задач, которые могут решать компьютеры.

Кэш-память (Cache – запас) обозначает быстродействующую буферную память между процессором и основной памятью. Кэш служит для частичной компенсации разницы в скорости процессора и основной памяти – туда попадают наиболее часто используемые данные. Когда процессор первый раз обращается к ячейке памяти, ее содержимое параллельно копируется в кэш и в случае повторного обращения в скором времени может быть с гораздо большей скоростью выбрано из кэша. При записи в память значение попадает в кэш, и либо одновременно копируется в память (схема Write Through – прямая или сквозная запись), либо копируется через некоторое время (схема Write Back – отложенная или обратная запись). При обратной записи, называемой также буферизованной сквозной записью, значение копируется в память в первом же свободном такте, а при отложенной (Delayed Write) – когда для помещения в кэш нового значения не оказывается свободной области; при этом в память вытесняется наименее используемая область кэша. Вторая схема более эффективна, но и более сложна за счет необходимости поддержания соответствия содержимого кэша и основной памяти.

Сейчас под термином Write Back, в основном, понимается отложенная запись, однако это может означать и буферизованную сквозную.

Память для кэша состоит из собственно области данных, разбитой на блоки (строки), которые являются элементарными единицами информации при работе кэша, и области признаков (tag), описывающей состояние строк (свободна, занята, помечена для дозаписи и т.п.). В основном используются две схемы организации кэша: с прямым отображением (direct mapped), когда каждый адрес памяти может кэшироваться только одной строкой (в этом случае номер строки определяется младшими разрядами адреса), и n-связный ассоциативный (n-way associative), когда каждый адрес может кэшироваться несколькими строками. Ассоциативный кэш более сложен, однако позволяет более гибко кэшировать данные; наиболее распространены 4-связные системы кэширования.

Процессоры 486 и выше имеют также внутренний (Internal) кэш нелбольшого объёма. Он также обозначается как Primary (первичный) или L1 (Level 1 – кэш первого уровня) в отличие от внешнего (External), расположенного на плате и обозначаемого Secondary (вторичный) или L2. В большинстве процессоров внутренний кэш работает по схеме с прямой записью, а в Pentium и более новых он может работать и с отложенной записью. Последнее требует специальной поддержки со стороны системной платы, чтобы при обмене по DMA можно было поддерживать согласованность данных в памяти и внутреннем кэше.

Shadow memory, или теневая память. В адресах памяти от 640 кб до 1 Мб (A0000-FFFFF) находятся «окна», через которые видно содержимое различных системных ПЗУ. Например, окно F0000-FFFFF занимает системное ПЗУ, содержащее системный BIOS, окно C0000-C7FFF - ПЗУ видеоадаптера (видео-BIOS) и т.п. При включении для каких-либо окон режима Shadow содержимое их ПЗУ копируется в участки ОЗУ, которые затем подключаются к этим же адресам вместо ПЗУ, «затеняя» их; запись в эти участки аппаратно запрещается для полной имитации ПЗУ. Это дает в первую очередь ускорение работы с программами/данными ПЗУ за счет более высокого быстродействия микросхем ОЗУ. Кроме этого, появляется возможность модифицировать видимое содержимое ПЗУ (почти все современные системные BIOS используют это для самонастройки). В области видео-BIOS можно поменять экранные шрифты и т.п.

Управлением теневой памятью занимается чипсет платы. Существуют различные программы для создания средствами теневой памяти UMB-блоков в MS DOS или для загрузки экранных шрифтов в область видео-BIOS.

Перенос памяти (Memory Relocation) – это перенос неиспользуемой памяти из системной области (диапазон 640 кб – 1 Мб) в область расширенной (Extended) памяти. В первых IBM PC устанавливалось 640 кб основной памяти и отдельно – расширенная память, поэтому со старшими 384 кб проблем не возникало. В современных платах вся память представляет собой непрерывный массив, поэтому системную область приходится аппаратно исключать, теряя при этом 384 кб. Большинство Chiрset'ов позволяют использовать часть этой памяти под Shadow Memory, однако некоторые могут переносить ее за пределы первого мегабайта, присоединяя к расширенной памяти. Одни Chipset'ы могут переносить все свободные от теневой памяти участки, другие – только все 384 кб целиком (в этом случае теневая память должна быть выключена).

Для управления внешним кэшем и системной памятью существуют модифицируемые параметры, описывающие временные диаграммы циклов чтения/записи. Все значения задаются в тактах – периодах системной тактовой частоты (частоты платы, а не внутренней частоты процессора).

Простой цикл обращения к памяти выполняется за два такта. В пакетном цикле (burst) первый обмен занимает два такта, остальные – по одному такту. Например, диаграмма 2-1-1-1 обозначает четырехсловный пакетный цикл без дополнительных задержек, 3-1-1-1 - с одной задержкой после первого обращения, 3-2-2-2 – с задержками после каждого обращения, и т.п.

Поскольку задержки задаются дискретно, при увеличении системной тактовой частоты общая производительность иногда может упасть. Например, при частоте 40 МГц длительность такта – 25 нс, что позволяет обмениваться с внешним кэшем 20 нс без задержек, а при 50 МГц такт занимает 20 нс, и такой кэш может перестает успевать. Добавление же одного такта задержки резко снижает пиковую производительность системы, хотя средняя производительность за счет достаточно медленной памяти изменяется незначительно.

Полный перечень всех возможных пунктов настройки слишком велик, к тому же он постоянно меняется. Кроме этого, для сознательного управления этими параметрами нужно хорошо представлять себе механизмы работы статических и динамических микросхем памяти, организации страничного обмена, конвейеризации и т.п. Описание параметров конкретной платы обычно можно найти на FTP/WWW-сервере производителя платы или ее BIOS.

В то время как обычные члены семейства PC, использующие микропроцессор 8088, ограничивались адресацией лишь одного мегабайта памяти, ветвь AT семейства может работать с памятью гораздо большего объема. Чаще всего, когда говорят «оперативная память», в виду имеется расширенная память. В современных персональных компьютерах объём расширенной памяти обычно достигает гигабайта и более.

Виртуальная память представляет собой определенную организованную взаимосвязь между микропроцессором, программой поддержки виртуальной памяти и диском компьютера. По существу, виртуальная память действует следующим образом. Когда программа устанавливается на выполнение в компьютере, операционная система создает «пространство виртуальной памяти», которое является моделью памяти и адресов памяти, которые программа имеет в своем расположении. Затем часть «реальной» или фактической физической (расширенной) памяти компьютера передается в виртуальную память.

Программа начинает работать в некотором (большом) пространстве виртуальной памяти, отображаемом в часть реальной памяти (обычно меньшего объема) компьютера. Пока программа работает только в этой части своей виртуальной памяти, все идет хорошо. Программа фактически использует адреса памяти, отличные от тех, которые определяются в программе, но это не имеет значения. Что происходит, когда программа пытается использовать несколько больше виртуальной памяти, чем было выделено реальной памяти? В этом случае таблица отображения микропроцессора обнаруживает, что программа пытается использовать адрес, который не существует в текущий момент; микропроцессор генерирует так называемое прерывание из-за отсутствия страницы.

Когда происходит прерывание из-за отсутствия страницы (означающее, что программа пытается использовать виртуальный адрес, который фактически не отображается в реальной памяти), вступает в действие специальная программа поддержки виртуальной памяти. Она временно помещает программу в состояние блокировки, пока занимается этим кризисом. Программа поддержки выбирает определенную часть виртуальной памяти, которая в текущий момент находится в реальной памяти, и временно помещает ее содержимое на диск; это называется откачкой. Эта часть реальной памяти задействуется в качестве понадобившейся части виртуальной памяти (подкачка). Когда откачанная часть памяти требуется вновь, она подкачивается обратным копированием с диска.

В зависимости от хода вычислительного процесса, функционирование виртуальной памяти может протекать очень гладко, либо оно может включать столько операций откачки и подкачки, что на ожидание перекачки данных между памятью и диском будет тратиться слишком много времени. Когда это происходит, то такая ситуация называется «пробуксовкой»: когда система виртуальной памяти начинает пробуксовывать, производительность компьютера резко падает.

Система управления памятью

Система управления памятью выполняет следующие основные функции:

· учет состояния свободных и уже распределенных областей памяти и модернизация этой информации всякий раз, когда в распределении памяти производятся изменения;

· распределение памяти для выполнения задач (определение, какой задаче, когда и в каком количестве выделить оперативную память);

· непосредственное выделение задаче оперативной памяти; если свободные области оперативной памяти отсутствуют, то предварительное их освобождение путем сохранения информации в виртуальной памяти.

Все доступное множество адресов элементов хранения, упорядоченное по какому-либо признаку, называют адресным пространством памяти. Физическое адресное пространство организовано просто как одномерный массив ячеек, каждой из которых присвоен свой номер, называемый физическим адресом.

В общем случае, под адресом понимают некий идентификатор, однозначно определяющий расположение элемента хранения среди прочих элементов в составе среды хранения.

Для адресации данных в физическом адресном пространстве программы используют логическую адресацию. Процессор автоматически транслирует логические адреса в физические, выдаваемые на адресную шину и воспринимаемые схемами управления (контроллерами) памяти.

Существуют две стратегии распределения оперативной памяти, как и любого ресурса: статическое и динамическое распределение.

При статическом распределении вся необходимая оперативная память выделяется процессу в момент его порождения. При этом память выделяется единым блоком необходимой длины, начало которого определяется базовым адресом. Программа пишется в адресах относительно начала блока, а физический адрес команды или операнда при выполнении программы формируется как сумма базового адреса блока и относительного адреса в блоке. Значение базового адреса устанавливается при загрузке программы в оперативную память. Так как в разных программах используются блоки разной длины, то при таком подходе возникает проблема фрагментации памяти, то есть возникают свободные участки памяти, которые невозможно без предварительного преобразования использовать для вычислительного процесса.

Данную проблему можно частично решить перераспределением памяти после завершения выполнения каждой программы с целью формирования единого свободного участка, который может быть выделен новой программе, поступающей на обработку (дефрагментация памяти). Однако это требует трудоемкой работы системных средств и практически не используется.

При динамическомраспределении памяти каждой программе в начальный момент выделяется лишь часть от всей необходимой ей памяти, а остальная часть выделяется по мере возникновения реальной потребности в ней. Такой подход базируется на следующих предпосылках.

Во-первых, при каждом конкретном исполнении в зависимости от исходных данных некоторые части программы вообще не используются. Следует стремиться к тому, чтобы эти фрагменты кода не загружались в оперативную память.

Во-вторых, исполнение программы характеризуется так называемым принципом локальности ссылок. Он подразумевает, что при исполнении программы в течение некоторого относительно малого интервала времени происходит обращение к памяти в пределах ограниченного диапазона адресов (как по коду программы, так и по данным). Следовательно, на протяжении этого времени нет необходимости хранить в памяти другие блоки программы.

При этом системные средства должны отслеживать возникновение требований на обращение к тем частям программы, которые в данный момент отсутствуют в памяти, выделять этой программе необходимый блок памяти и помещать туда требуемую часть программы. Для этого может потребоваться предварительное перемещение некоторых блоков информации в виртуальную память.

Перемещение блоков информации из оперативной памяти в виртуальную с целью освобождения места для новой информации происходит обычно по одному из следующих алгоритмов:

· LRU (least recently used) – наиболее давно не использовавшийся;

· FIFO – самый давний по пребыванию в оперативной памяти;

· Random – случайным образом.

В ЭВМ на основе 32-разрядного микропроцессора при работе в так называемом защищенном режиме, поддерживающем мультипрограм-мирование и обеспечивающем адресацию операндов в максимально возможном для данной архитектуры диапазоне до 232 байт, виртуальная память организуется на основе сегментно-страничного представления памяти. При этом память разбивается на сегменты переменной длины, выделяемые пользователю под размещение его программ и данных. Сегменты, в свою очередь, делятся на страницы фиксированной длины (4К = 212 байт), используемые системой управления памятью для ее виртуализации.

Начало каждого сегмента устанавливается операционной системой через соответствующий сегментный регистр и скрыто от пользователя. Пользователь пишет свои программы в адресах относительно начала сегмента, полагая, что он располагает сегментом максимально возможной для данной архитектуры длины (232 байт). Аппаратные средства микропроцессора сначала проводят сегментное преобразование адреса, а затем – страничное.

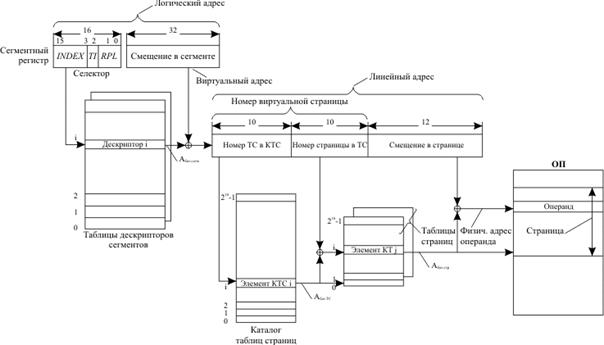

Механизм формирования физического адреса при сегментно-страничной организации памяти показан на рис. 10.

Основой получения физического адреса, выдаваемого на адресную шину микропроцессора, служит логический адрес. Он состоит из двух частей: селектора, являющегося идентификатором сегмента, и смещения в сегменте.

Смещение в сегменте (32 разряда) (эффективный адрес) вычисляется по задаваемому в команде режиму адресации операнда и является виртуальным адресом операнда. При обращении к команде в качестве смещения выступает значение регистра-указателя команд.

Селектор размещается в сегментном регистре (см. рис. 10). Основная его часть представляет собой номер (INDEX), по которому в одной из специальных таблиц дескрипторов можно найти дескриптор (descriptor) данного сегмента. Вид используемой таблицы определяется битом TI (Table Indicator) селектора. Селектор содержит также двухразрядное поле RPL, используемое при организации защиты памяти по привилегиям.

Рис. 10. Формирование физического адреса при сегментно-страничной организация памяти в 32-разрядном микропроцессоре

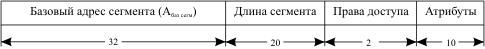

Дескриптор содержит сведения о сегменте. В одном из его полей содержится базовый адрес сегмента, в остальных находится дополнительная информация о сегменте: длина, допустимый уровень прав доступа к данному сегменту с целью защиты находящейся в нем информации, тип сегмента (сегмент кода, сегмент данных, специальный системный сегмент и т.д.) и некоторые другие атрибуты.

Сумма полученного из дескриптора базового адреса сегмента и вычисленного смещения дает линейный адрес операнда, который при включенном механизме страничного преобразования представляет собой номер виртуальной страницы (старшие 20 разрядов) и смещение операнда в странице (младшие 12 разрядов линейного адреса в соответствии с объемом страницы в 4 Кбайт).

При преобразовании номера виртуальной страницы в номер физической используются следующие системные объекты: каталог таблиц страниц (КТС) и таблицы страниц (ТС). Структуры этих таблиц сходны между собой.

Преобразование проводится в два этапа.

1. Сначала по разрядам А31-А22 линейного адреса в КТС выбирается нужный элемент. Каталог таблиц страниц всегда присутствует в оперативной памяти и содержит указания по размещению таблицы страниц, относящейся к тому или иному процессу.

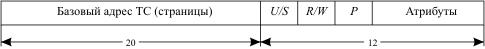

Элемент КТС содержит:

· адрес начала таблицы страниц;

· бит присутствия (P) таблицы страниц в оперативной памяти;

· бит разрешения чтения/записи (R/W);

· бит защиты страницы (пользователь/супервизор (U/S)) и некоторые другие атрибуты.

После получения из выбранного элемента КТС начального адреса таблицы страниц происходит обращение к ТС. В выбранной таблице страниц находится элемент, номер которого определяется разрядами А21-А12 линейного адреса. Структура элемента таблицы страниц аналогична структуре элемента КТС. Элемент ТС в соответствующем поле содержит адрес начала требуемой физической страницы и другие атрибуты, аналогичные элементу КТС.

При P=0 возникает прерывание, необходимая страница подкачивается в оперативную память, ее адрес заносится в соответствующий элемент ТС, и команда выполняется повторно.