Внеочередное исполнение операций, функциональные устройства

Подсистему внеочередного исполнения операций вместе с функциональными устройствами объединяют под названием «Back End», чтобы подчеркнуть её обособленность и самостоятельность. Внутри этой подсистемы обработка операций ведётся асинхронно, с учётом зависимостей между ними, готовности операндов и наличия требуемых ресурсов (устройств и очередей). При внеочередной обработке операций в этой подсистеме гарантируется, что результаты такого выполнения программы совпадут с результатами «правильного» последовательного выполнения.

Отставка выполненных машинных инструкций после их выхода из подсистемы внеочередного исполнения производится строго последовательно. Таким образом, восстанавливается натуральный порядок следования операций. Говорить о внешнем или архитектурном состоянии программы можно только с позиции последней машинной инструкции, покинувшей блок отставки. При возникновении какого-либо прерывания все последующие инструкции будут считаться невыполненными вне зависимости от действительного состояния их выполнения. При выходе из прерывания все эти инструкции будут повторно исполнены с самого начала.

Ниже описана организация подсистемы внеочередного исполнения операций и характеристики функциональных устройств, в которых эти операции выполняются. Структура этой подсистемы связана с устройством подсистемы декодирования инструкций, поэтому характеристики этих двух подсистем тесно переплетаются.

Здесь рассмотрена организация данной подсистемы только для архитектуры процессоров P-III, P-M, а также Core Duo. Более подробно об организация подсистемы внеочередного исполнения операций другой архитектуры можно узнать из статьи, ссылка на которую сделана в конце лекции.

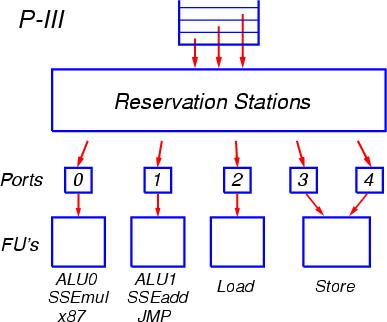

После выхода из декодера сформированные группы по три МОПа помещаются в буфер переупорядочения ROB, длина которого составляет 40 элементов (начиная с процессора P-M размер буфера ROB, по некоторым данным, увеличен до 60-80 элементов). Новая группа МОПов также копируется в очередь планировщика RS, из которой операции будут запускаться на исполнение. В процессоре P-III используется единая очередь планировщика размером в 20 элементов (начиная с процессоры P-M – 24 элемента), общая для всех типов операций. МОПы выбираются на исполнение из этой очереди во внеочередном порядке, по мере готовности аргументов операций (рис. 4).

Рис. 4. Организация внеочередного исполнения операций в процессорах архитектуры P-III, P-M, Core Duo.

МОПы отправляются на исполнение через так называемые порты запуска. Всего таких портов пять: два для арифметико-логических операций (ALU), и три – для операций вычисления адресов и для загрузки/выгрузки. К каждому из портов подсоединены соответствующие функциональные устройства.

Порт 0 обслуживает устройства целочисленной арифметики и логики, включая блоки для выполнения умножения и деления, а также устройства арифметики с плавающей точкой x87 и устройство умножения SSE. К порту 1 подсоединено другое устройство целочисленной арифметики и логики, частично дублирующее аналогичное на порту 0, устройство для выполнения переходов, а также устройства сложения и некоторых дополнительных операций SSE.

Начиная с процессора P-M, операции умножения и сложения с плавающей точкой x87 разнесены по разным портам (по аналогии с операциями SSE): умножение осталось на порту 0, а сложение переведено на порт 1. Также добавлены операции SSE2 с аналогичным распределением между портами.

К портам 2 и 3 подсоединены устройства вычисления адресов для операций загрузки из памяти и выгрузки в память, а к порту 4 – собственно устройство выгрузки, готовящее данные для отсылки в память.

В процессоре P-III при декодировании инструкций загрузки из памяти с последующим исполнением (Load-Op) порождаются отдельные МОПы для загрузки и для выполнения. Оба этих МОПа помещаются в буфер переупорядочения ROB и в очередь планировщика RS и обслуживаются по отдельности. Начиная с процессора P-M, в декодере реализован механизм «слияния микроопераций» (micro-ops fusion), когда порождается единый МОП, содержащий два элементарных действия. Разделение на эти элементарные действия, или микрооперации, происходит при их запуске на исполнение (диспетчеризации) из очереди планировщика. Сначала запускается микрооперация загрузки (через порт 2), а затем, в преддверии готовности операнда – функциональная микрооперация (через порт 0 или 1).

Аналогично операциям загрузки для инструкций выгрузки в память в процессоре P-III также порождаются два отдельных МОПа: для вычисления адреса и для осуществления записи. Эти МОПы запускаются (диспетчеризуются) по отдельности, соответственно через порты 3 и 4. Начиная с процессора P-M, для инструкций выгрузки порождается единый МОП, который разделяется на микрооперации при запуске на исполнение.

Механизм слияния микроопераций позволяет экономить ресурсы буферов внеочередного исполнения (ROB и RS), имеющих ограниченный размер, и увеличить эффективную пропускную способность трактов процессора.

Через каждый из пяти портов может отсылаться на исполнение по одной операции за такт. Таким образом, очередь планировщика представляет собой полностью ассоциативный буфер с довольно сложной организацией. В каждом такте может производиться поиск и извлечение до пяти элементов (МОПов) из этого буфера, и одновременно в него может быть помещено три новых МОПа. Для отправки на исполнение в буфере ищутся операции, аргументы которых уже вычислены либо вычисляются и будут готовы к моменту попадания в функциональное устройство. Если для какого-то порта найдено несколько таких готовых операций, среди них выбирается одна по алгоритму «псевдо-FIFO» (First In, First Out). Этот алгоритм отдаёт предпочтение самым старым операциям, однако выполняет поиск не совсем строго и точно, что связано со сложностью реализации алгоритма с точным соблюдением старшинства. В результате может оказаться, что 100-процентная скорость выполнения потока инструкций не достигается даже при оптимальном потактовом планировании машинных инструкций программистом или транслятором из-за того, что не в каждом такте через порты 0 и 1 запускаются две операции.

Латентность большинства операций целочисленной арифметики составляет 1 такт, а их суммарный темп исполнения – 2 операции за такт, по одной в устройствах, подсоединённых к портам 0 и 1. Некоторые операции (сложения/вычитания и копирования, а также логические) могут выполняться в устройствах на обоих портах. Также в каждом такте может быть произведено одно считывание из L1-кэша и одна запись в L1-кэш (64-разрядные).

Операции арифметики с плавающей точкой x87 выполняются в соответствующем устройстве на порту 0 (начиная с процессора P-M – в раздельных устройствах на портах 0 и 1). Операции сложения FADD могут стартовать в каждом такте, а операции умножения FMUL – с интервалом в 2 такта. Чередуя сложение и умножение, можно получить суммарный темп выполнения, равный одной операции за такт. Латентность операции сложения составляет 3 такта, умножения – 5 тактов.

Операции перестановки регистров x87 в стеке (FXCH) отрабатывают на стадии переименования регистров и поэтому не попадают в очереди планировщика и в функциональные устройства. Темп обработки таких операций равен трём за такт.

Скалярные операции SSE исполняются в полном темпе, упакованные операции – в половинном. Это связано с тем, что каждая упакованная инструкция SSE преобразуется в два МОПа. С учётом чередования сложения и умножения, суммарный темп выполнения составляет два МОПа за такт, что соответствует четырём 32-битным арифметическим операциям для упакованного режима. Латентность операций сложения и умножения SSE составляют соответственно 3 и 4 такта.

Операции сложения в 64-битном режиме SSE2 (начиная с процессора P-M) также выполняются в полном темпе с латентностью 3 такта, а операции умножения — в половинном темпе с латентностью 5 тактов. Таким образом, суммарный темп выполнения таких операций при чередовании сложения и умножения составляет один МОП за такт. На практике на процессоре P-III удаётся добиться уровня в 0.9-0.95 арифметической операции SSE2 за такт.

Таким образом, в процессоре P-III имеется ряд недостатков, ограничивающих его производительность. Главным из них является слабость блока плавающей арифметики при работе в 64-битном и 80-битном режимах (SSE2 и x87). Другим недостатком являются ограничения в планировщике, которые не позволяют достичь полной скорости работы функциональных устройств. Некоторые ограничения микроархитектуры преодолены в процессорах P-M и P-M2 (Core Duo).

Полную информацию о функционировании процессоров можно посмотреть в Интернете по адресу:

http://www.ixbt.com/cpu/cpu-microarchitecture-part-1.shtml

http://www.ixbt.com/cpu/cpu-microarchitecture-part-2.shtml