Принципы устройства современных МПС

Общая структура МПС

Микропроцессор - центральная часть любой микропроцессорной системы (МПС) - включает в себя АЛУ и ЦУУ, реализующее командный цикл. МП может функционировать только в составе МПС, включающей в себя, кроме МП, память, устройства ввода/вывода, вспомогательные схемы (тактовый генератор, контроллеры прерываний и ПДП, шинные формирователи, регистры-защелки и др.).

В любой МПС можно выделить следующие основные части (подсистемы) :

· процессорный модуль;

· память;

· внешние устройства (внешние ЗУ + устройства ввода/вывода);

· подсистему прерываний;

· подсистему прямого доступа в память.

|

Связь между процессором и другими устройствами МПС может осуществляться по принципам радиальных связей, общей шины или комбинированным способом. В однопроцессорных МПС, особенно 8- и 16-разрядных, наибольшее распространение получил принцип связи "Общая шина", при котором все устройства подключаются к интерфейсу одинаковым образом (Рис.1.1).

Рис.1.1. Структура МПС с интерфейсом "Общая шина"

Все сигналы интерфейса делятся на три основные группы - данных, адреса и управления. Многочисленные разновидности интерфейсов "Общая шина" обеспечивают передачу по раздельным или мультиплексированным линиям (шинам). Например, интерфейс Microbus, с которым работают большинство 8-разрядных МПС на базе i8080, передает адрес и данные по раздельным шинам, но некоторые управляющие сигналы передаются по шине данных. Интерфейс Q-bus, используемый в микро-ЭВМ фирмы DEC (отечественный аналог - микропроцессоры серии К1801) имеет мультиплексированную шину адреса/данных, по которой эта информация передается с разделением во времени. Естественно, что при наличии мультиплексированной шины в состав линий управления необходимо включать специальный сигнал, идентифицирующий тип информации на шине.

Обмен информацией по интерфейсу производится между двумя устройствами, одно из которых является активным, а другое - пассивным. Активное устройство формирует адреса пассивных устройств и управляющие сигналы. Активным устройством выступает, как правило, процессор, а пассивным - всегда память и некоторые ВУ. Однако, иногда быстродействующие ВУ могут выступать в качестве задатчика (активного устройства) на интерфейсе, управляя обменом с памятью (т.н. режим прямого доступа в память - см. раздел 8).

Концепция "Общей шины" предполагает, что обращения ко всем устройствам МПС производится в едином адресном пространстве, однако, в целях расширения числа адресуемых объектов, в некоторых системах искусственно разделяют адресные пространства памяти и ВУ, а иногда даже и памяти программ и памяти данных.

Как известно, процессор является основным вычислительным блоком компьютера, в наибольшей степени определяющим его мощь. Процессор является устройством, исполняющим программу - последовательность команд (инструкций), задуманную программистом и оформленную в виде модуля программного кода. Чтобы понять, что делает процессор, рассмотрим его в окружении системных компонентов IBM PC-совместимого компьютера. Этой компьютерной архитектурой, естественно, не ограничивается сфера применения процессоров.

Всем известный IBM PC-совместимый компьютер представляет собой реализацию так называемой фон-неймановской архитектуры вычислительных машин. Эта архитектура была представлена Джоном фон-Нейманом еще в 1945 году и имеет следующие основные признаки. Машина состоит из блока управления, арифметико-логического устройства (АЛУ), памяти и устройств ввода/вывода. В ней реализуется концепция хранимой программы: программы и данные хранятся в одной и той же памяти.

Рис. 1.1 Архитектура фон-Неймана

Если разделить память на: память программ и память данных мы получим Гарвардскую архитектуру.

Рис. 1.2 Гарвардская архитектура

Выполняемые действия определяются блоком управления и АЛУ, которые вместе являются основой центрального процессора. Центральный процессор выбирает и исполняет команды из памяти последовательно, адрес очередной команды задается "счетчиком адреса" в блоке управления. Этот принцип исполнения называется последовательной передачей управления. Данные, с которыми работает программа, могут включать переменные - именованные области памяти, в которых сохраняются значения с целью дальнейшего использования в программе.

Фон-неймановская архитектура - не единственный вариант построения ЭВМ, есть и другие, которые не соответствуют указанным принципам (например, потоковые машины). Однако подавляющее большинство современных компьютеров основано именно на этих принципах, включая и сложные многопроцессорные комплексы, которые можно рассматривать как объединение фон-неймановских машин. Конечно же, за более чем полувековую историю ЭВМ классическая архитектура прошла длинный путь развития.

Прерывание – первое отличие современных архитектур от машин фон-Неймана. Работа прерывания заключается в том, что при поступлении сигнала прерывания процессор обязан прекратить выполнение текущей программы и немедленно начать обработку процедуры прерывания.

Рис. 1.3 Архитектура фон-Неймана с прерыванием

ПДП (Прямой Доступ к Памяти) – второе отличие современных архитектур от машин фон-Неймана. ПДП позволяет сократить расходы на пересылку единицы информации.

Рис. 1.4 Архитектура фон-Неймана с каналом ПДП

Шинная организация IBM PC

В основу архитектуры IBM PC изначально был положен принцип открытости, который стал ее отличительной чертой. Основные конкуренты IBM в области персональных машин пришли к этому только через несколько лет после того, как указанный принцип позволил персональным компьютерам фирмы IBM практически завоевать компьютерный рынок.

Принцип открытости, строго говоря, основывается во-первых, на чрезвычайно развитой в IBM PC системе прерываний, которая позволяет “подключать” программы пользователя ко всем ресурсам системы на любом уровне, доступном пользователю, а во-вторых, на системе шин, организующей информационные потоки таким образом, чтобы не только позволить пользователю подключать к ресурсам процессора свои аппаратные средства (возможно, нестандартные), но и дать возможность самой архитектуре совершенствоваться и развиваться за счет введения дополнительных или новых компонентов без каких-либо принципиальных изменений в организации информационных потоков.

Принципы организации открытой системы прерываний будут рассмотрены ниже в отдельном разделе, а здесь остановимся на шинной организации информационных потоков, которая берет свое начало с первой модели IBM PC и эволюционирует сегодня. Как Вам известно из курса "Организации ЭВМ", шину микрокомпьютера образует группа линий передачи сигналов с адресной информацией, информацией о передаваемых данных, а также управляющих сигналов. Фактически ее можно разделить на три части: адресную шину, шину данных и шину управления.

Уровни этих сигналов в каждый момент времени определяют состояние всей вычислительной системы в этот момент. Далее мы привяжем обсуждение этих принципов функционирования к конкретной архитектуре ЭВМ, совместимых с IBM PC AT-286 и 386. На рис.2.1 изображено ядро гипотетической вычислительной системы, включающей, например, синхрогенератор i82284, микропроцессор i80286 и математический сопроцессор i80287, а также шинный контроллер i82288.

Рис 2.1. Шины компьютера.

Кроме того, показаны три шины: адреса, данных и управляющих сигналов. Синхрогенератор генерирует тактовый сигнал CLK для синхронизации внутреннего функционирования процессора и других микросхем. Сигнал RESET производит сброс процессора в начальное состояние. Сигнал READY, также формируется с помощью синхрогенератора, предназначен для удлинения циклов шины при работе с медленными периферийными устройствами. На адресную шину, состоящую из 24 линий, микропроцессор i80286 выставляет адрес байта или слова, которые будут пересылаться по шине данных в процессор или из него. Кроме того, шина адреса используется микропроцессором для указания адресов (номеров) периферийных портов, с которыми производится обмен данными.

Шина данных состоит из 16 линий, по которым возможна передача как отдельных байтов, так и двухбайтовых слов. При пересылке байтов возможна передача отдельно как по старшим 8 линиям, так и по младшим. Шина данных двунаправленна, т.к. передача байтов и слов может производиться как в микропроцессор, так и из него. Шина управления формируется сигналами, во-первых, поступающими непосредственно от микропроцессора, во-вторых, сигналами, сформированными системным контроллером, и, в-третьих, сигналами, идущими к микропроцессору от других микросхем и периферийных адаптеров. Микропроцессор использует системный контроллер для формирования управляющих сигналов, определяющих правила переноса данных по шине. Он выставляет три сигнала S0, S1, M/IO (выводы 5, 4 и 65), которые определяют тип цикла шины (подтверждение прерывания, чтение порта ввода/вывода, запись в порт ввода/вывода, останов, чтение памяти, запись в память). На основании значений этих сигналов системный контроллер формирует управляющие сигналы, определяющие последовательность процессов данного типа цикла шины.

Для того чтобы понять динамику работы шины, разберем, каким образом процессор осуществляет чтение слова из оперативной памяти. Это происходит в течение четырех тактов CLK (тактовых импульсов на входе 31 микропроцессора), или двух внутренних состояний процессора (т.е. каждое состояние процессора длится 2 такта синхросигнала CLK). Во время первого состояния, обозначаемого как Ts, процессор выставляет на адресную шину значение адреса, по которому будет читаться слово. Кроме того, он формирует на шине совместно с шинным контроллером соответствующие значения управляющих сигналов. Эти сигналы и адрес обрабатываются схемой управления памятью, в результате чего, начиная с середины второго состояния процессора Ts (т.е. в начале четвертого такта CLK) на шине данных появляется значение содержимого соответствующего слова из оперативной памяти. И, наконец, процессор считывает значение этого слова с шины данных. На этом перенос (копирование) значения слова из памяти в процессор заканчивается.

Эволюция шинной архитектуры

Когда микропроцессор с рассмотренной шинной архитектурой выполняет, например, команду чтения из памяти, воздействие (адрес и сигналы управления) с локальной L шины попадает на системную S шину, а только затем на шину памяти M. После этого данные, считанные из памяти, опять-таки попадают на системную шину, а с нее - на локальную. Очевидно, что каждый перенос информации через тот или иной буферный элемент сопровождается определенной задержкой. И пусть одна задержка невелика (не более 10 наносекунд), но суммарно их набирается довольно много, что и определяет ту довольно низкую тактовую частоту, на которой работали первые IBM PC - 12, или даже 8 Мгц.

Рис 2.3 Классическая архитектура IBM PC AT 286

Для устранения таких потерь в более поздних моделях IBM PC AT 286 основная оперативная память выделяется в особую подсистему и доступ к ней осуществляется не через системную шину, а параллельно с доступом к системной шине. Как правило, это связано с наличием интегрированного контроллера шины данных. Суммарная задержка передачи данных в этом случае сокращается примерно до 20 нс, а тактовая частота повышается до 25 МГц.

Рис 2.4 Архитектура IBM PC AT 286 поздних моделей

Дальнейшее совершенствование систем в этом направлении привело к тому, что переход от шины данных LD локальной шины к шине MD шины памяти упростился до предела. Функцию контроллера шины данных в этом случае выполняет обычный шинный формирователь. На первый взгляд, в нем нет необходимости и можно было бы просто объединить шины LD и MD. Но по соображениям согласования электрических сигналов этого нельзя делать.

Рис 2.5 Архитектура IBM PC AT 386 с конвертором системной шины

Дальнейшие возможности повышения производительности процессора связаны с поисками решений в области архитектуры РС АТ. Введение кэш- памяти позволило ослабить требования по времени доступа к основной оперативной памяти (кэш-память - это статическая память с малым временем доступа, которая не “видна” для программного обеспечения. Объем ее колеблется от 128Кбайт до 1 Мбайт). При этом на локальной шине, кроме микропроцессора и сопроцессора, появляется контроллер управления кэш- памятью. При объеме памяти 128 Кбайт вероятность того, что необходимая микропроцессору информация окажется в кэш-памяти, состовляет 95-98%. Эффективность кэш-памяти становится значительной на частотах выше 20 Мгц, так как в этом случае потери производительности из-за задержек доступа к оперативной памяти очень чувствительны.

Последующие архитектурные изменения связаны с переходом от процессоров, имеющих 32 разрядные шины данных (i80386 и i80486), к процессорам, имеющим 64 разрядные шины, а именно к процессорам Pentium, Pentium Pro и Pentium II.

Рис 2.6 Архитектура IBM PC AT с кеш-памятью

Передача информации в МПС

При организации последовательного обмена ключевыми могут считаться две проблемы:

1) синхронизацию битов передатчика и приемника;

2) фиксацию начала сеанса передачи.

В МПС существует три способа передачи информации:

· асинхронный;

· синхронный;

· смешанный.

Асинхронный способ характеризуется тем, что сигналы передаются с произвольными промежутками времени.

Синхронный способ характеризуется тем, что сигналы передаются строго периодично во времени.

Смешанный способ характеризуется тем, что байты передаются асинхронно, а биты внутри байтов синхронно.

Асинхронный способ

Асинхронный способ обеспечивает передачу информации по единственной линии. Для надежной синхронизации обмена в асинхронном режиме

1) передатчик и приемник настраивают на работу с одинаковой частотой;

2) передатчик формирует стартовый и стоповый биты, отмечающие начало и конец посылки;

3) передача ведется короткими посылками (5..9 бит), а частоты передачи выбираются сравнительно низкими.

Асинхронный способ по методу регистрации сигналов делится на:

· стробируемый;

· «запрос-ответ».

Метод стробирования

Строб – дополнительный сигнал, является подтверждением действительности других сигналов.

Стробирование может осуществляться по фронту или по уровню.

Рис. 3.1 Виды стробов.

рис 3.2 Стробируемый метод

рис 3.3 Стробируемый метод

Стробирование по фронту.

Достоинства:

· легкая аппаратная реализация;

· высокое быстродействие.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· момент переключения трудно зафиксировать программно.

Стробирование по уровню.

Достоинства:

· легкая аппаратная реализация;

· легкая программная реализация;

· легкая организация приема от нескольких источников.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· меньшее быстродействие.

Метод «запрос-ответ»

рис 3.4 Метод «запрос-ответ»

t1 – передатчик выставляет данные (предварительно проверив отсутствие строба-ответа)

t2 – передатчик с некоторой задержкой выставляет сигнал строб-запрос

t3 – приемник, анализируя состояние линии строб-запрос, обнаруживает наличие определенного сигнала и в этот же момент осуществляет прием данных по линии.

t4 – передатчик, сканируя линию строб-ответ, обнаруживает, что он активен и сбрасывает строб-запрос

t5 – приемник, сканируя линию строб-запрос, обнаруживает, что строб запрос стал неактивен и сбрасывает строб-ответ

t6 – тоже самое, что и t1

Достоинства:

· позволяет сопрягать аппаратуру существенно отличающуюся быстродействием;

· легко организуется программным путем.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· меньшее быстродействие.

Синхронный способ

В синхронном способе передачи информации выделяют изохронный метод.

Синхронизация бывает:

· внутренняя

· внешняя

Изохронный метод

В этом методе передачи информации возможна потеря данных. Здесь сам приемник определяет какие данные принимать, а какие нет (например для звуковой информации).

Внешняя синхронизация

Сигналы синхронизации поступают вместе с данными. В этом случае форма сигналов может быть неправильной. Поэтому внешняя синхронизация используется только при передаче на небольшие расстояния, т.е. внутри платы.

Внутренняя синхронизация

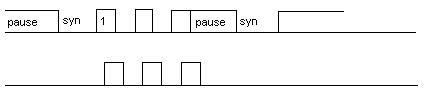

рис 3.5 Внутренняя синхронизация

SYN – специальный сигнал пересылаемый один раз и запускающий тактовый генератор.

Достоинства:

· достаточно двух линий: сигнал и земля;

· высокая частота;

· высокая надежность связи;

· длина пакета определяется взаимной синхронностью передатчики и приемника.

|

При синхронном методе передатчик генерирует две последовательности - информационную TxD и синхроимпульсы CLK, которые передаются на приемник по разным линиям (Рис. 3.6).

Рис. 3.6. Последовательный синхронный обмен с внешней синхронизацией

Синхроимпульсы обеспечивают синхронизацию передаваемых бит, а начало передачи отмечается по-разному.

При организации внешней синхронизации сигнал начала передачи BD генерируется передатчиком и передается на приемник по специальной линии (Рис. 3.6).

В системах с внутренней синхронизацией отсутствует линия BD, а на линию данных генерируются специальные коды длиной 1-2 байта - “символы синхронизации”. Для каждого приемника предварительно определяются конкретные синхросимволы, таким образом можно осуществлять адресацию конкретного абонента из нескольких, работающих на одной линии. Каждый приемник постоянно принимает биты с RxD, формирует символы и сравнивает с собственными синхросимволами. При совпадении синхросимволов последующие биты поступают в канал данных приемника.

Подсистема прерываний МПС

Подсистема прерываний - совокупность аппаратных и программных средств, обеспечивающих реакцию программы на события, происходящие вне программы. Такие события возникают, как правило, случайно и асинхронно по отношению к программе и требуют прекращения (чаще временного) выполнения текущей программы и переход на выполнение другой программы (подпрограммы), соответствующей возникшему событию.

Контроллеры прерываний

Внешние устройства, включенные в подсистему прерываний, должны реализовать несколько функций, связанных с работой в этой подсистеме - формирование запроса, анализ ответа процессора, выдачу вектора прерывания. Кроме того, в подсистеме необходимо обеспечить дисциплину обслуживания запросов. Перечисленные функции могут быть реализованы на специальных устройствах - контроллерах прерываний, которые выпускаются в виде БИС в составе многих микропроцессорных комплектов.

Рис. 5.2. Общая схема контроллера прерываний

Рис. 5.3. Контроллер К589ИК14

На Рис. 5.3 приведена структурная схема простого контроллера прерываний К589ИК14, применяемого совместно с МП К580ВМ80 (на схеме показаны лишь основные блоки и выводы контроллера).

Контроллер включает в себя следующие блоки:

Ø РгЗП - регистр запросов, на который поступают запросы на прерывание z0..z7 от внешних источников;

Ø ПШ - приоритетный шифратор, формирующий на выходе трехразрядный код номера возбужденного входа (соответствующего разряда РгЗП), причем, если на входе ПШ присутствуют несколько единиц, то на выходе будет сформирован код большего номера;

Ø Буф. - буферная схема, подключающая выход ПШ к линиям системной шины данных при подаче на управляющий вход сигнала подтверждения прерывания INTA;

Ø РгТП - регистр текущего приоритета, программно-доступный в пространстве ввода/вывода и хранящий трехразрядный код приоритета текущей программы;

Ø СС - схема сравнения, формирующая запрос на прерывание INT процессору при условии, что код наибольшего из поступивших запросов больше кода текущего приоритета.

МП проверяет состояние входа INT в конце каждого командного цикла при условии установки в "1" триггера разрешения прерывания TI. Если INT = 1, то МП вместо машинного цикла M1 следующего командного цикла выполняет цикл обслуживания прерывания, который отличается от M1 только тем, что вместо сигнала RDM\ вырабатывается сигнал INTA\ и программный счетчик PC не инкрементируется. Поэтому не происходит чтение команды из памяти (хотя ее адрес и выставлен на AB[15:0]), а по сигналу INTA\ контроллер выставляет на DB[5:3] трехразрядный номер запроса. На остальных линиях DB сохраняются лог. "1" (высокоимпедансное состояние). В такте T3 цикла обслуживания прерывания код с DB[7:0] записывается в регистр команд МП.

Код 11nnn111 представляет собой код одной из восьми команд RST 0. . RST 7, которые выполняются аналогично командам CALL, но с фиксированными адресами вызываемых подпрограмм:

RST 0 = CALL 0000h

RST 1 = CALL 0008h

RST 2 = CALL 0010h

.. . . . .

RST 7 = CALL 0038h

Таким образом, каждому запросу соответствует фиксированный адрес обслуживаемой его подпрограммы.

К недостаткам рассмотренного выше контроллера прерываний К589ИК14 относится жесткая система приоритетов запросов, не позволяющая обеспечить равновероятное обслуживание источников прерываний. Кроме того, контроллер не позволяет выделить произвольное подмножество разрешенных в данный момент прерываний из множества поступающих на его входы запросов. Возможно лишь задать определенный уровень, начиная с которого запросы будут разрешены.

Использование ..ИК14 накладывает ограничение на расположение обслуживающих прерывания подпрограмм или указателей на них в адресном пространстве памяти. Команды RST вызывают подпрограммы из начальной области адресов памяти (0000..0038), что не всегда удобно при организации МПС.

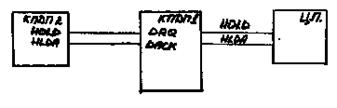

Каскадирование КПДП

Рис. 6.4. Каскадирование КПДП

Организация ПДП в IBM PC

В современных машинах используются дополнительные контроллеры ПДП, один из которых 16-ти разрядный, но также есть и 8-ми разрядные.

При программировании контроллера указываются адреса, приоритеты, регистр страниц ПДП.

Рис. 6.5. Организация ПДП в IBM PC

Функции контроллера ПДП

|

На Рис. 6.7 показана структура 32-разрядного восьмиканального контроллера ПДП в составе кристалла 82380. При проектировании контроллера ставилась задача эффективной передачи произвольных комбинаций байтов, слов и двойных слов. С помощью контроллера ПДП можно адресовать полное пространство, покрываемое 32-разрядными физическими адресами, а также увеличивать и уменьшать адреса как операндов-источников, так и операндов назначения.

Рис. 6.7. Контроллер ПДП в 82386

С помощью внутреннего вспомогательного 32-разрядного регистра можно выполнять разборку и сборку данных разной разрядности, а также организовывать обмен данными между устройствами, имеющими разную ширину тракта данных. При работе контроллера 82380 на частоте 20 МГц и при передаче данных одинаковой разрядности может быть достигнута скорость обмена между памятью и устройствами ввода-вывода 25,6 Мбайт/с.

В порядке обслуживания как программных, так и аппаратных запросов ПДП контроллер может поддерживать обмен данными следующих типов:

· порт ввода-вывода — порт ввода-вывода;

· память — память;

· порт ввода-вывода — память;

· память — порт ввода-вывода.

Семь из восьми каналов (все, за исключением канала 4) имеют доступ к аппаратным сигналам подтверждения ПДП через трехразрядную шину подтверждения ПДП (линии от EDACK0 до EDACK2).

Каждый из восьми каналов контроллера ПДП 82380 функционирует независимо один от другого и может быть запрограммирован для работы в любом из допустимых режимов. Регистры каждого канала можно разделить на три класса: регистры счетчика байтов, регистры инициатора запроса и. целевые регистры; всего в канале имеется 24 регистра состояний и команд. С помощью этих регистров определяются адреса и объем пересылаемых данных. Регистр счетчика байтов (24 разряда) содержит значение числа байтов, которые должны быть переданы. Регистр инициатора запроса (32 разряда) содержит адрес порта ввода-вывода или памяти, где находятся данные, по которым был сделан запрос контроллеру на обслуживание ПДП; целевой регистр (32 разряда) содержит адрес порта ввода-вывода или памяти, по которому будут пересылаться данные.

Для каждого канала программист может выбирать дисциплину обслуживания с циклическими или фиксированными приоритетами. Циклический приоритет предусматривает разделение шины среди нескольких периферийных устройств, тогда как дисциплина с фиксированными приоритетами основана на определенных фиксированных параметрах, связанных с аппаратными и другими особенностями. В дисциплине с фиксированными приоритетами допускается, чтобы программист присваивал любому каналу низший приоритет, что позволит без перепрограммирования командных регистров изменять или приводить в исходное состояние расписание обслуживания приоритетов.

Каналы контроллера ПДП разделены на две группы по четыре канала — нижнюю и верхнюю. Нижние (от нулевого до третьего) и верхние (от четвертого до седьмого) каналы работают так, будто два отдельных контроллера ПДП включены по каскадной схеме. Такая организация работы позволяет одной группе присваивать фиксированные приоритеты, а другой — циклические, причем в различных комбинациях. По умолчанию каналы контроллера ПДП 82380 имеют фиксированные приоритеты, при этом высшим приоритетом обладает нулевой канал, низшим — седьмой. Нижняя группа играет своеобразную роль канала 5 в верхней группе и по порядку приоритетов располагается между каналами 7 и 4.

Как уже отмечалось, программисту предоставлена возможность по своему усмотрению выбирать, какому из каналов назначить низший приоритет. С помощью специальных команд определяется канал с самым низким приоритетом в пределах какой-либо группы, при этом остальным каналам присваиваются фиксированные приоритеты в последовательном порядке. Например, если низший приоритет присвоен каналу 1 в нижней группе, то порядок каналов по приоритетам будет следующий: 2 (высший приоритет), 3, 0, 1 (низший приоритет). Как видно, каналу, порядковый номер которого следует сразу же за номером выбранного канала с низшим приоритетом (в данном случае за номером 2), устанавливается самый высокий приоритет и так далее с убыванием приоритета по мере последовательного циклического в рамках группы возрастания номеров каналов, пока не будет достигнут номер выбранного наименее приоритетного канала (в данном случае номер 1). То же относится и к верхней группе каналов. Так, если низший приоритет присвоен каналу 6, то приоритеты верхней группы составят следующий ряд: 7 (высший приоритет), 4—6 (низший приоритет). Еще раз напоминаем, что нижняя группа по приоритету располагается между каналами 4 и 7. Поэтому по данным рассмотренных выше примеров комбинация двух групп даст следующий порядок каналов: 7 (высший приоритет), [2, 3, 0, I], 4, 5, 6 (низший приоритет).

Контроллер ПДП может принимать команды программного управления приоритетами только тогда, когда группа каналов, к которой относятся эти команды, находится в режиме с фиксированными приоритетами. При переходе к дисциплине с циклическими приоритетами все текущие уровни приоритетов остаются без изменений. При возврате от дисциплины с циклическими приоритетами к дисциплине с фиксированными приоритетами для уровней приоритетов каналов с помощью команд программного управления приоритетами восстанавливаются те значения, которые были в последний раз установлены программным образом.

Для дисциплины с циклическими приоритетами любой канал после обслуживания его запроса не остается с высшим приоритетом. Этому каналу присваивается низший приоритет. Следует помнить, что номера приоритетов нижней группы (в предыдущем примере 2, 3, 0, 1) меняются циклически в пределах верхней группы приоритетов (в предыдущем примере 7, [нижняя группа], 4 – 6). Поэтому обслуживание канала из нижней группы сопровождается циклическим изменением номеров уровня приоритета как в нижней, так и в верхней группах.

Такие команды, как "сброс запроса прерывания по завершении счета", "сброс режима ведущего устройства", "очистка регистра маски" и "сброс триггера указателя байтов", активизируются в результате распознавания контроллером ПДП 82380 соответствующего адреса порта. При этом в выбранный порт должны быть записаны какие-нибудь данные.

Контроллер ПДП 82380 реализует передачу блоков данных в одном из следующих режимов: режим одиночного буфера, буферный режим с автоинициализацией и режим с цепочкой буферов. Первый режим используется обычно в тех случаях, когда к моменту начала передачи известны объем и местоположение передаваемых данных, а данные размещены в непрерывной области памяти. Для данного режима характерно, что по завершении передачи одиночного блока контроллер ПДП должен перепрограммироваться для других передач даже этого же блока. В буферном режиме с автоинициализацией, напротив, допускается неоднократная передача контроллером ПДП одного и того же блока данных без перепрограммирования канала всякий раз.

В режиме с цепочкой буферов допускается, чтобы в программе был определен список буферов, содержимое которых передается, при этом для перепрограммирования контроллера ПДП используются программы обработки прерываний. Канал для передачи содержимого нового буфера программируется до того, как закончится передача содержимого текущего буфера. В данном режиме контроллер ПДП может работать с разрывными областями памяти и передавать все данные из этих областей за один рабочий процесс ПДП.

Подсистема памяти МПС

Диспетчер памяти

При необходимости расширить объем памяти за пределы адресного пространства можно воспользоваться т.н. "диспетчером памяти". В простейшем случае он представляет собой программно-доступный регистр, который должен располагаться в пространстве ввода/вывода. В него заносится номер активного в данный момент банка памяти, причем объем банка может равняться объему адресного пространства МП (2k).

Очевидно, в каждый момент времени процессору доступен только один банк. При необходимости перехода в другой банк памяти МП должен предварительно выполнить программную процедуру (часто всего одну команду) перезагрузки содержимого номера банка. Сказанное иллюстрируется Рис. 7.44. К развитию этой идеи можно отнести механизм сегментации памяти в 16- и 32-разрядных МП фирмы INTEL.

Рис. 7.4. Использование диспетчера памяти

Запоминающие устройства

Память может быть внутренней и внешней. Внешней называют память на магнитных, оптических дисках, лентах и т.п. Внутренняя память выполняется, чаще всего, на микросхемах. Внутренняя или основная память может быть двух типов: оперативное запоминающее устройство (ОЗУ) или ЗУ с произвольной выборкой (ЗУПВ) и постоянное ЗУ (ПЗУ). ОЗУ, кроме того, обозначается - (RAM, Random Access Memory), а ПЗУ - (ROM, Read Only Memory). Получила также распространение Флэш(Flash) память, имеющая особенности и ОЗУ и ПЗУ и энергонезависимая память (Nonvolatile - NV) на батарейках. Последнее название условно, так как ПЗУ и Флэш память, также энергонезависимы. В ОЗУ коды в соответствии с решаемыми задачами постоянно изменяются и полностью пропадают при выключении питания. В ПЗУ хранятся управляющие работой ЭВМ стандартные программы, константы, таблицы символов и другая информация, которая сохраняется и при выключении компъютера. ОЗУ подразделяются на статическую память (SRAM), динамическую (DRAM), регистровую (RG). ПЗУ могут быть: масочными - запрограммированными на заводе изготовителе (ROM), однократно-программируемыми пользователем ППЗУ (PROM или OTP), многократно-программируемыми (репрограммируемыми) пользователем РПЗУ с ультрафиолетовым стиранием (EPROM) или c электрическим стиранием (EEPROM). Широкое распространение нашли также программируемые логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т.д.) с большим выбором логических элементов и устройств на одном кристалле.

В зависимости от типа ЗУэлементом памяти (ЭП)может быть: триггер, миниатюрный конденсатор, транзистор с "плавающим затвором", плавкая перемычка (или ее отсутствие). Упорядоченный набор ЭП образует ячейку памяти (ЯП). Количество элементов памяти в ячейке (длина слова) обычно кратно 2n (1,4,8,16, 32,64..), причем величины свыше 8-ми достигаются, обычно, группировкой микросхем с меньшим количеством ЭП. Количество ЭП в ЯП иногда называется длиной слова. Основными характеристиками микрсхем памяти являются: информационная емкость, быстродействие и энергопотребление. Емкость ЗУ чаще всего выражается в единицах кратных числу 210 = 1024 = 1K. Для длины слова равной биту (одному двоичному разряду)или байту (набору из восьми бит) эта единица называется килобит или килобайт и обозначается Kb или KB.

Рис. 7.5

Каждой из двух в степени "n" ячеек памяти однозначно соответствует "n"- разрядное двоичное число, называемое адресом ЯП. Например, адресом 511-ой ячейки будет число 1 1111 1111(BIN) = 511(DEC) = 1FF(HEX). В программах адреса употребляются в 16-ном формате. Емкость ЗУ часто выражается произведением двух чисел 2n * m, где 2n - число ячеек памяти, а m - длина слова ячейки, например 8K * 8 (м/с 537РУ17), т.е. 8192 ячейки размером в один байт. В некоторых справочниках для этой же микросхемы приводится обозначение емкости одной цифрой 64Kбит, что никак не отражает внутреннюю организацию этой микросхемы, такую же емкость могут иметь м/с с организацией 16K * 4, 64K * 1 и т.д.

&nb