Понятие виртуальной памяти. Страничная, сегментная и смешанного типа организация виртуальной памяти.

Виртуа́льная па́мять - это область выделенная Операционной системой на жестком диске. технология управления памятью ЭВМ, разработанная для многозадачных операционных систем. При использовании данной технологии для каждой программы используются независимые схемы адресации памяти, отображающиеся тем или иным способом на физические адреса в памяти ЭВМ.

Вся прога разбив-ся на части равной велич., котор. наз-ся страницами. Р-р страницы выбир-ся от 4 до 8 кБ. В общ. случ. р-р кратен ёмк-ти одного сектора магн-го диска.

Вирт. и физич. адр. Простр-во разбив-ся на блоки размером в страницу. Всем страницам присваивают номера.

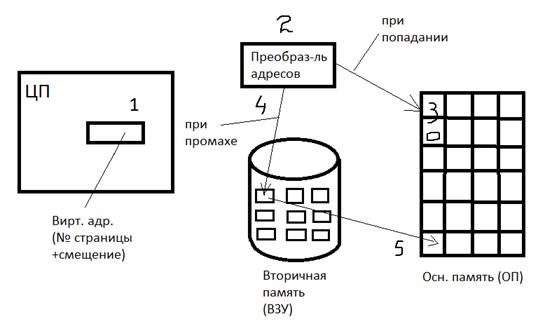

1. ЦП обращ. к ячейке памяти, указав при этом адрес. Вирт. адр. поступает 2 в сист. преобраз. Адресов, чтобы получить физич. адр. ячейки в осн. памяти. 3 – получ. физич. адр. в ОП.

Физич. адр. - № стр. и смещ.

Смещение в вирт. и физич. адр.пр. одинак.=> преобраз. нужно только № стр. При попадании физич. адр. берётся процом.

Если нужная физич. стр. отсутств. в основн. памяти, то происх обращ. к внешн. Памяти и, затем страницы счит-ся в ОП.

Преобразователь адресов – часть ОС + аппаратные ср-ва.

Виртуальн. адр. простр-во опис-ся 2-мя стр.:

- табл. страниц;

- карта диска.

Табл стр. указ. какие именно вирт. страницы находятся в физич. памяти и их местоположение.

Карта диска содерж. инфу о секторах диска, где хранятся вирт. стр. на диске.

Сегментная и сегментно-страничная орг-ия

В предыдущем подходе предполагалось – ВП – непрер. массив со сквозной нумерацией слов, что не всегда хорошо.

Обычно прога сост. из неск. сегм. (кода, данн., стека).

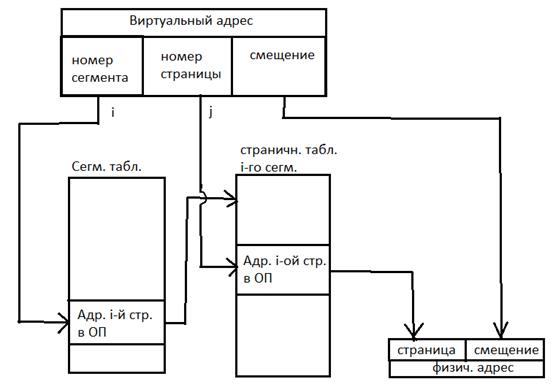

Т.к. заранее не известны длины сегментов, то удобно, чтобы кажд. сегм. Имел собств. Нумерацию слов, начиная с 0. Для этого организ. сист. сегментации памяти, когда в вирт-ом адр. простр. Выдел независ. Линейные простр-ва переменной длины и назыв. их сегментами.

ВП как и ОП разбив-ся на сегменты с независимой адресацией слов внутри сегмента. Вирт. адр. предст. собой № сегм.+смещение.

Чтобы преобраз. вирт. адр. в физич. исп-ся сегментная таблица. Главн. недост-ом такой орг-ии явл-ся неэффект-ое использ-ие ОП, т.к. заранее неизвестен р-р сегм. Выходом явл-ся сегм-но-страничн. орг-ия, когда р-р сегм. выбир. не произвольно, а задаётся кратным р-ру страницы. Сегм. содерж целое число страниц., даже если страница не заполнена.

Таким образм для получ. физич. адр. необх. доступ к сегментной табл. и одной из страничных таблиц => преобраз адр. заним. много времени.

17. КЭШ-память. Назначение. Принцип функционирования.

Функционально КЭШ-память предназначена для согласованной скорости работы сравнительно медленных устройств, например динамической памяти, с относительно быстрым микропроцессором.

Внутренняя архитектура МП основана на работе статических элементов памяти (триггеров, регистров), быстродействие которых достаточно большое. Например, в МП 80386 при fсинхр = 33 МГц тактовый период равен 30нс. В то время как время выборки информации из ОЗУ динамического типа составляет 60 - 100 нс. Поскольку большую часть времени МП осуществляет чтение памяти (команд, данных), то ОЗУ динамического типа значительно снижает быстродействие ЭВМ, так как при обращении к памяти МП вынужден в течении 2-3 тактов ожидать готовности данных.

Микросхемы статической памяти имеют примерно в 5 раз меньшее время выборки (до 15 нс), что позволило бы исключить простои ЦП при обращении к памяти. Однако стоимость микросхем статического типа выше, а удельная емкость меньше.

Поэтому в память ЭВМ вводится небольшое количество ячеек памяти статического типа — КЭШ-память, в которой по мере работы процессора автоматически накапливается наиболее актуальная информация. Первоначально эта информация находится в динамической памяти большого объема. А затем при считывании информации из главной памяти (динамического типа) соответствующие копии откладываются в КЭШ-памяти.

Отличительными особенностями КЭШ являются:

1. Малый объем (от 8кбайт)

2. Быстродействие сравнимое с быстродействием процессора.

КЭШ – это тайник, недоступно для программ, так как не может быть адресовано машинными командами.

КЭШ является “невидимой” для пользователя и для процессора и выражается только в увеличении быстродействия памяти.

Суть заключается в следующем, когда процессору понадобилась информация, сначала он обращается к КЭШ памяти, если информация там есть (такое событие называется КЭШ попаданием), то нужное слово извлекается из КЭШ и передается процессору. Если нет (КЭШ промах), то идет обращение к оперативной памяти, информация помещается в КЭШ затем передается процессору.

- Основные функциональные характеристики блоков КЭШ-памяти.

1) Емкость КЭШ.

2) Метод отображения. Так как количество строк Кэш памяти гораздо меньше, чем количество блоков памяти, необходимо установить соответствие между строкой КЭШ и строкой в оперативной памяти (ОП). Установление соответствие и называется функцией отображения.

· Прямая функция. За каждым блоком ОП закрепляется определенная строка КЭШ.Достоинства: простота реализации. Недостаток: обновление одних строк КЭШ будет происходить часто, другие могут быть вообще не задействованы.

· Ассоциативная. В этом случае Тетл являются все старшие разряды кода памяти, разрывается жесткая связь между блоком ОП и строкой КЭШ. Достоинства:обеспечение гибкости. Недостаток:усложнение логики поиска, усложнение алгоритмов управления Кэш памяти

· Секционированное – ассоциативная. В этом случае весь массив Кэш памяти делится на секции с фиксированным количеством строк.

3) Алгоритм замены строк в КЭШ

· LRU – least recently used – заменяется строка, к которой дольше всего не обращался процессор.

· LFU - least freguently used – заменяется, прежде всего, используемая строка

· FIFO – first in, first out – заменяется строка, записанная в КЭШ раньше остальных

· Случайный – выбирается случайным образом строка КЭШ.

4) Обеспечивание целостности информации.

· Сквозная запись – все операции записи дублируются в ОП

· Обратная запись – процессор вносит изменения только в свой КЭШ и информация записывается в ОП только по окончания процесса. Минимизирует количество обращений к ОП.

5) Размер блока. (2-8 слов)

6) Структурная и архитектурная организация блока.

· Количество уровней в иерархии

· Емкость КЭША растет по мере перехода от более верхнего уровня к более низкому

· КЭШ команд

· КЭШ данных

Если организуется единый массив КЭШ памяти, то упрощаются схемы контроллеров КЭШ, а при организации сегментированной организации массива, возможно параллельно обрабатывать команды и данные.

19. Сравнительная характеристика организации КЭШ–памяти прямого отображения, ассоциативной и наборно-ассоциативной.

1. КЭШ с прямым отображением

2. ассоциативная КЭШ

3. наборно - ассоциативная КЭШ

1) Адрес полностью определяет используемую строку КЭШ с ОП.

Строка КЭШ минимальный блок данных, которыми обменивается КЭШ с ОП.

При КЭШ-попадании считывание идет из КЭШ, иначе из ОП и соответственно строка КЭШ обнавляется.

КЭШ + 8 строк х 8 байт + 64 байта

Для примера десятиразрядный адрес.

В этом методе адрес однозначно определяется номером строки КЭШ.

Если теги совпадают и V + 1, то чтение идет из КЭШ, если нет, то из ОП.

+ — малые аппаратные затраты ( одна операция сравнения для тегов)

- — если 2 блока претендуют на одну строку КЭШ ( в этом примере на одну строку претендуют 2 4 ячеек, т.е. 16) и они одинаково часто используются

2) в полностью ассоциативной КЭШ-памяти любой блок памяти может занимать любую строку КЭШа.

Полный адрес памяти делится только на 2 части: тег и смещение.

+ — Отсутствие конфликтов адресов (любой адрес ОП может занимать любую строку КЭШ).

- — большие аппаратные затраты для сравнения всех тегов.

3) наборно ассоциативная архитектура.

Несколько линий адреса образуют набор и сравнение тегов производится только для строк КЭШа, входящих в набор.

Двухвходовый наборно-ассоциативный КЭШ

КЭШ может быть разделен для команд и данных, что позволяет оптимизировать отдельные кэши.