Особенности суперскалярных микропроцессоров.

Данная архитектура обеспечивает одновременное выполнение двух и более команд. Для этой цели в МП реализовано несколько специальных или универсальных обрабатывающих устройств (конвейеров), которые могут работать параллельно. Управляющее устройство МП обеспечивает просмотр очереди команд на возможность одновременного выполнения нескольких команд и если такие команды найдены, обеспечивает загрузку ими исполнительных устройств. Т.о. функцию распараллеливания потока команд берет на себя аппаратура процессора (без вмешательства программиста).

При этом для увеличения загрузки исполнительных устройств необходимо:

· устранение зависимостей по управлению (предсказание переходов)

· устранение зависимостей по данным (переименование регистров)

Особенности архитектуры:

- "+" Программист не заботится о распараллеливании

- "-" распараллеливание происходит динамически (затрачивается процессорное. время)

- "-" распараллеливается только ограниченная часть программного кода (т.е. далеко расположенные друг от друга не связанные между собой команды одновременно не могут быть выполнены)

- "-" высокая сложность УУ

Пример: МП Pentium Pro (II, III)

- Организация памяти ЭВМ. Статические и динамические ОЗУ.

Вся память ЭВМ имеет иерархич. структ. Принято раздел. 3 ур-ня иерарх. пам.:

1. Высший – внутр память CPU, КЭШ, RAM. Верхн. Ур-нь иерарх. принято назыв. основным.

2. Средний ур-нь – магн. диски.

3. Нижний – съёмное хранилище инфы.

По мере перехода от верхн. к нижн. сниж-ся стоим-ть, повыш. объём, сниж-ся быстродей-ие.

Осн. память (О.п.)

О.п. ЭВМ образуют ЗУ с прямым доступом/произвольн. доступом. Такие ЗУ образованы как массив ячеек, а произвольн. доступ означает, что обращение к любой ячейке занимает одно и тоже время и выполн. в произвольн. посл-ти.

Кажд. ячейка в массиве содерж. фиксир-ое число запомин. эл-ов и имеет уникальн. адрес.

Изначально ЗУ были построены на базе ферромагн. колец. Современные ЗУ явл-ся п/п и строятся на базах:

- биполярн. Транз-ов;

- МОП-транз-ов;

- МНОП-транз-ов;

- ПЗС-приборы;

МОП--транз-ов с изолир. затвором.

Осн. память

|  |

ОЗУ (RAM) ПЗУ (ROM)

RAM занимает больш. часть в ОП. Доп-ет как запись, так и счит-ие инфы, причём обе опер-ии выполн. однотипно (≈ с одинак. скор-тью) и выполн. при помощи эл-их сигн.

ROM обеспеч. счит-ие инфы. Почти не допускает изменен инфы, но измен. может быть проведено, но сильно отлич. счит-ие и занимает больше врем.

Вся память предст-на в виде интегральн. м/с. Это матрица ячеек, кажд. ячейка в зав-ти от разрядн-ти ИМС содержит1-н/неск-ко запомин. эл-ов и имеет свой адрес. Кажд запомин. эл-нт способен хранить 1-н бит инфы.

RAM

Явл-ся энергозависимой памятью. Делится на 2 группы:

1. DRAM (динамич.) В ней запомин. эл-нт может хранить запис-ую инфу в течен. Короткого промежутка врем., по истечен. котор. Инфу нужно восстан./она будет потеряна.

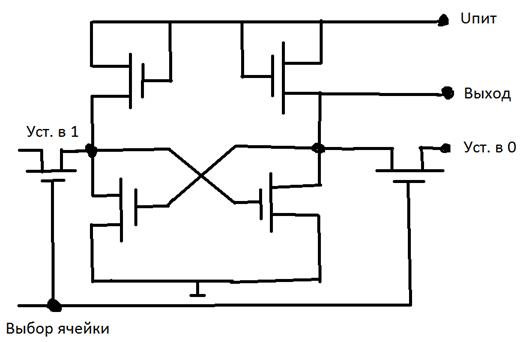

2. SRAM (статич.) В ней запомин. эл-нт может хранить инфу неогранич. долго при наличии питающ-го U-ия. Роль запомин эл-та в SRAM выполн. триггер:

Такой триггер сост. из 4-х/6-ти транз-ов и предст. собой. сх. с 2-мя устойч. сост. Сх. с 4-мя транз-ми обеспеч. бὀльшую ёмкость м/с => меньш. стоим., но у неё большой ток утечки. Если инфа просто хранится также триггер на 4-х транз. более чувствит. к возд. внешн. источн. излучен.

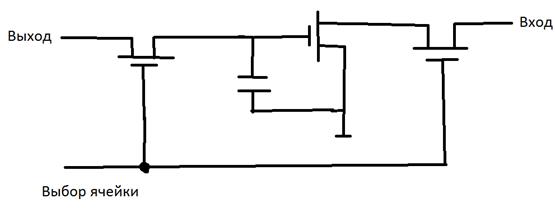

DRAM

Запомин. эл-нт DRAM сост. из одного конденс. и запир. транз-ра. Наличие/отсутствие заряда в конденс. интерпретир-ся как 1/0. Простота реализ-ии сх. позвол. достичь высок. плотн. размещен. эл-ов. и тем самым уменьш. стоим. Основн. недост. Явл-ся то, что накапливаемый на конденс. заряд со временем теряется. Средн. время утечки заряда в динамич. ЗУ сост. 100-ни/10-ки мс => необх. восст. заряд в течен. данн. отр-ка врем., иначе инфа потер-ся. Периодич. восст. заряда назыв-ся регенерацией и осущ-ся кажд 2 – 8 мс.

Обл. применен. SRAM и DRAM опред-ся скор-тью и стоим-тью.

Осн. дост-ом SRAM явл-ся её высок. быстрод-ие, онон больше, чем у DRAM (в 10-ки раз), но SRAM облад. низк. ёмк-тью и высок. стоим-тью => её примен. ограниченно - это КЭШ-память: L1, L2, L3. КЭШ может работать со врем. доступа к инфе = врем. одного тактового импульса проца.

Самые быстрые м/с DRAM на чтение 1-го байта пакета треб. от 5 до 10 тактов проца, что замедл. работу всей сист., но из-за высок. упак-ки запомин. эл-ов и относ-но низк стоим-ти именно DRAM-модули исп-ся при построен. ОП ЭВМ.