На скачкообразное приращение электрических величин

(ВЕКТОРОВ ТОКА ПРЯМОЙ И ОБРАТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЕЙ)

В отечественных энергосистемах и за рубежом разработаны и используются несколько вариантов УБК, основанных на различии скорости изменения электрических величин (сопротивления Z, тока I, напряжения U) при качаниях и КЗ. Ниже рассматривается новый вариант подобных УБК, реагирующих на скачкообразное увеличение (приращение) модуля и угла вектора тока обратной последовательности ΔI2/Δt, имеющих место только при КЗ. Устройство разработано во ВНИИР (г. Чебоксары) при участии проектного института "Энергосетьпроект" и применяется в дистанционных защитах типа ШДЭ-2801 и ПДЭ-2001, выпускаемых АО ЧЭАЗ.

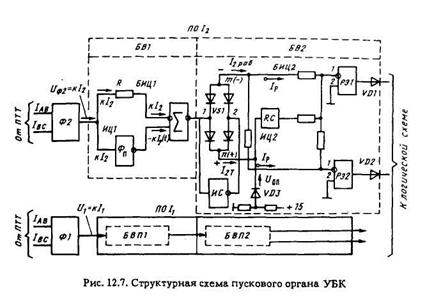

Устройство состоит из измерительных (пусковых) органов и логической части. Измерительный орган имеет два пусковых органа (рис.12.7):

основной ПО I2, реагирующий на приращение тока обратной последовательности, рассчитанный на действие при всех видах КЗ, сопровождающихся появлением составляющих I2;

дополнительный ПО I1, реагирующий на приращение составляющей тока прямой последовательности ΔI1/Δt.

Дополнительный орган предназначен для обеспечения надежного действия УБК при К(3), если из-за отсутствия или малого значения I2 основной ПО I2 не подействует.

Структуру ПО и принцип выделения аварийной составляющей рассмотрим на примере основного комплекта ПО I2. Токи защищаемого объекта, получаемые от измерительных ТТ, преобразуются в промежуточном трансформаторе тока ПТТ и поступают на вход фильтра обратной последовательности Ф2, на выходе которого появляется напряжение, пропорциональное составляющей обратной последовательности тока защищаемой линии UФ2 = kI2. С выхода Ф2 сигнал поступает на блок выделения БВ1, осуществляющий выделение приращения вектора тока I2 (или пропорционального ему напряжения kI2), имеющего место при появлении КЗ.

Схема блока БВ1 состоит из двух параллельных цепей — инерционной цепи ИЦ1 и безынерционной цепи БИЦ1, сумматора Σ, осуществляющего сложение сигналов, поступающих с указанных цепей. Инерционная цепь содержит активный полосовой фильтр Фп, замедляющий прохождение синусоидального сигнала промышленной частоты, поступающего на его вход на 0,01 с (время половины периода синусоидального тока с частотой f = 50 Гц) и одновременно инвертирующий фазу сигнала на 180°. Безынерционная цепь (БИЦ) передает сигнал без задержки (мгновенно) и без изменения фазы, так как цепь имеет только активное сопротивление R (X = 0). Сигналы цепей поступают на сумматор Σ.

Параметры схемы подобраны так, чтобы в установившемся режиме (после затухания переходного процесса в полосовом инерционном фильтре Фп) выходные сигналы обеих цепей были равны и противоположны по фазе. При этом условии выходной сигнал сумматора будет пропорционален разности входных сигналов Uвых Σ = k'(kI2 – kI2(t)), т.е. будет равен нулю. Это означает, что в нормальном режиме, когда по защищаемой линии проходит ток нагрузки (при котором I2 ≈ 0), выходной сигнал Ф2 kI2 будет равен небалансу, обусловленному погрешностями измерительных ТТ и самого фильтра. Сигнал на выходе блока приращения БВ1 при этом будет отсутствовать, и, следовательно, небаланс в нормальном режиме не будет влиять на работу ПО. При скачкообразном увеличении напряжения U2 на выходе фильтра Ф2 с kI2 до kI2' новое напряжение поступит на вход сумматора по безынерционной цепи практически мгновенно, а так как в инерционной цепи сигнал не может измениться скачком, то он останется неизменным: kI2(t). Поэтому в первый момент переходного процесса на выходе сумматора появится сигнал, пропорциональный разности входных напряжений kI2' – kI2(t) = kΔI2. Таким образом, благодаря наличию инерционной цепи схема БВ1 выделяет приращение входного вектора. По мере затухания переходного процесса kI2(t) будет нарастать и через t = 0,01 с достигнет нового уровня kI2'(t), при котором kΔI2 станет равной нулю.

Однако схема БВ1 имеет недостаток – в режиме качания токи качания достигают больших значений, изменяется частота тока fк ≠ 50 Гц, что приводит к резкому увеличению амплитуды тока небаланса, а из-за отклонения частоты меняется частотная характеристика полосового фильтра Фп. В результате нарушается равенство токов, поступающих на вход сумматора Σ, и на его выходе появляется напряжение небаланса, от которого необходимо отстроить ток срабатывания ПО (т.е. снизить его чувствительность). Чтобы исключить ложное действие при качаниях от Iнб и не снижать чувствительности УБК, возникла необходимость введения дополнительного блока БВ2. Он состоит из двухполупериодного выпрямителя VS1 и двух реагирующих элементов: чувствительного РЭ1 и более грубого (в 1,5–2 раза) РЭ2. Выпрямительный мост используется как селектор прошедших через выпрямитель положительных (+) и отрицательных (–) сигналов (полуволны синусоидального напряжения, поступающие с выхода сумматора на вход выпрямителя). На вход 1 моста VS1 сигнал сумматора поступает непосредственно без изменения фазы, а по второй цепи на вход 2 моста сигнал сумматора идет через инвертор ИС с изменением фазы на 180°. По абсолютному значению оба сигнала одинаковы. Как видно из рис.12.7, выпрямленные сигналы положительного знака собираются на нижней шинке моста п (отмеченной знаком "+"), на верхнюю шинку m (обозначенную знаком "–") приходят сигналы отрицательной полярности. Выходные цепи выпрямителя с отрицательной шинки приходят на входы 1 РЭ1 и РЭ2 без задержки и соответствуют выходному сигналу сумматора. На те же входы 1 приходит выпрямленный сигнал с положительной шинки VS1 с задержкой по времени, определяемой постоянной времени контура RC в цепи ИЦ2. В эту же точку приходит опорное напряжение +Uоп, снимаемое с делителя напряжения положительного знака, определяющее напряжение срабатывания ПО.

В нормальном установившемся режиме сигналы, поступающие с шинок моста "+" и "–", уравновешиваются, поскольку ,они равны по значению и противоположны по знаку. Поэтому под действием +Uоп на выходе реагирующих элементов дежурят отрицательные сигналы, означающие, что ПО не работает и быстродействующие ступени заблокированы, независимо от уровня небалансов, а также от значения I2 нагрузки.

При КЗ происходит скачкообразное изменение сигнала, появляющийся ток КЗ на выходе сумматора поступает на выпрямительный мост. Соответственно мгновенно возрастает напряжение на отрицательной шинке выпрямителя, и этот сигнал поступает на входы 1 РЭ1 и РЭ2. Положительный сигнал в точке п выпрямительного моста в первый момент КЗ остается неизменным, а затем плавно нарастает по мере заряда конденсатора контура RC. В результате, при достаточном значении скачкообразного приращения сигнала отрицательного знака, сумма сигналов на входах 1 реагирующих элементов имеет отрицательный знак. При этом на их выходе появляется сигнал положительного знака, передающий на логическую часть через диоды VD1, VD2 сигнал о срабатывании ПО УБК. При К(3) работают оба ПО I2 и I1, а при отсутствии несимметрии действует только дополнительный ПО I2, реагирующий на скачкообразное появление составляющей прямой последовательности.

В режиме качаний на вход VS1 с выхода сумматора поступает медленно изменяющееся переменное напряжение неcкомпенсированного небаланса. Параметры схемы подобраны так, что возникающий при этом отрицательный сигнал на VS1 будет меньше положительного с учетом опорного напряжения Uоп. Поэтому на выходах РЭ возникнут сигналы отрицательного знака, при которых логическая схема не работает (иначе говоря, ПО не действует).

Применение блока БВ2 позволяет надежно отстроиться от небаланса при качаниях и сохранить высокую чувствительность ПО.

Дополнительный ПО I1 выполнен и работает аналогично, но его входной ток поступает с фильтра Ф1.

Принципиальная схема ПО, реагирующего на резкое приращение тока I2(ΔI2/Δt), приведена на рис.12.8. Участки схемы, соответствующие структурным элементам схемы на рис.12.7, выделены пунктирным контуром и обозначены так же, как и на структурной схеме.

Фильтр ОП (фильтр Ф2 на рис.12.7) выполнен на операционном усилителе (ОУ) А1 (рис.12.8) с частотным фильтром ФВЧ в цепи обратной связи по схеме, рассмотренной в гл. 2, для ограничения прохождения высших гармоник, искажающих работу ПО.

Принципиальная схема блока БВ1 (БВ1 А12 на рис. 12.8), выделяющего приращение I2(ΔI2/Δt) на переменном токе, состоит из суммирующего усилителя A3, выполненного на ОУ, и инвертирующего частотного полосового фильтра Ф, настроенного на рабочую частоту 50 Гц. Фильтр Ф представляет собой инвертирующий ОУ А2, в цепи обратной связи которого включен фильтр по схеме двойного Т-образного RC-моста. Рассматриваемый фильтр Ф является инерционным элементом, замедляющим прохождение быстро изменяющихся сигналов вследствие наличия конденсаторов в цепи обратной связи (линия задержки).

Как видно из схемы на рис.12.8, входной сигнал, приходящий с фильтра Ф2 в виде напряжения UФ2 = kI2, поступает на вход усилителя A3 по двум параллельным ветвям через безынерционную ветвь с резистором R11 и через инерционную — с фильтром Ф. Сигнал, проходящий через фильтр Ф, инвертируется и всегда имеет знак, противоположный сигналу, проходящему по безынерционной цепи через резистор R11. На входе усилителя A3 оба сигнала суммируются с учетом их знаков: UА3 = kRI2 – kфI2, где kRI2 и kфI2 — сигналы, проходящие через A3 и Ф соответственно. Параметры схемы выбираются так, чтобы kR = kф = k.

Работа схемы БВ1 (рис.12.8). При симметричной нагрузке с Ф2 приходит сигнал в виде напряжения небаланса UФ2 = Uнб. при несимметричной UФ2 = kфI2Н. В обоих случаях UФ2 изменяется относительно медленно, и сигналы, проходящие по каналу R11 и Ф, поступают на вход A3 практически одновременно. Их алгебраическая сумма (при частоте 50 Гц) близка к нулю. Поэтому выходной сигнал сумматора A3 отсутствует: UΣ = 0. Следовательно, при принятой схеме небаланс, возникающий в нормальном режиме, не создает напряжения на выходе схемы БВ1 и поэтому практически не влияет на работу ПО.

При качаниях UФ2 на выходе фильтра Ф2 возрастает в результате увеличения небаланса, вызванного ростом фазных токов, а также из-за изменения частоты токов качания, нарушающей балансировку элементов фильтра задержки Ф, подобранных для работы с частотой 50 Гц. Помимо этого из-за изменения частоты в энергосистеме меняется ZФ — сопротивление фильтра Ф, а следовательно, и коэффициент усиления усилителя А2, что порождает различие токов в инвертирующей и неинвертирующей ветвях. В результате этого сумма токов, приходящих на И-вход сумматора A3, отличается от нуля. На выходе сумматора появляется напряжение UΣ = – (IR – IФ)ZФ. Влияние этого напряжения на работу ПО устраняется в схеме БВ2.

При возникновении КЗ (К(1), К(2) и в первый момент К(3)) выходное напряжение фильтра Ф2 UФ2 изменяется скачком от предшествующего значения до UФ2к = kI2к за счет появления составляющей ОП I2к в токе Iк. В этом случае сигнал, проходящий по ветви с инерционным фильтром Ф, поступает на суммирующий усилитель с некоторой задержкой времени Δt ≈ 0,01 с. До появления этого сигнала на входе A3 присутствует сигнал kRI2к, пришедший без замедления через резистор R11. В результате этого в течение времени задержки сигнала Δt, поступающего от фильтра Ф, на выходе усилителя A3 появляется сигнал (напряжение) UA3, пропорциональный приращению входного напряжения UФ2kRI2(t), или, иначе говоря, пропорциональное приращению I2к.

Такое выделение составляющей ОП при КЗ обеспечивается благодаря принятой схеме

передачи сигналов с выхода фильтра Ф2 по двум параллельным ветвям с наличием в одной из них замедляющего и инвертирующего элемента А2.

Схема БВ2 выделения ΔI2 на выпрямленном токе (рис.12.8) имеет в своем составе диодный двухполупериодный выпрямительный мост VS1, используемый в качестве избирателя положительных и отрицательных сигналов; инвертирующий операционный усилитель А4 с коэффициентом передачи kU = 1, Являющийся повторителем входного сигнала с изменением его знака, т.е. работающего как инвертор; инерционный элемент в виде цепи RC для замедления передачи сигналов положительного знака выпрямителя VS1. В режиме качаний нескомпенсированный небаланс в виде сигнала UΣ поступает с выхода предыдущей схемы БВ1 в точку 1 и через инвертор А4 в точку 2 выпрямительного моста VS1. Оба сигнала имеют одинаковое значение UΣ, но различную полярность вследствие наличия в цепи 2 инвертора А4. Выпрямленные сигналы (пульсирующие с двойной частотой) снимаются с точек 3 и 4 VS1. На выходе 3 выпрямителя VS1 выделяются сигналы отрицательного знака U3(–), а в точке 4 — положительного U4(+). В каждый момент времени их абсолютные значения равны и пропорциональны сигналам сумматора UΣ, поступающим на входы 1 и 2 моста VS1|U3(–)| = |U4(+)| = k|UΣ|.

Сигналы отрицательной полярности U3(–) через резисторы R18 и R22, а положительной полярности U4(+) через инерционный элемент RC, резисторы R20 и R21 подаются для сравнения на элементы И компараторов А5 и А6 соответственно. Эти компараторы являются реагирующими элементами ПО РЭ1 и РЭ2.

Элемент РЭ1 выполняется в 2-3 раза чувствительнее грубого ПО РЭ2. Это достигается подбором сопротивлений резисторов R18, R19, R20 и R21. Они выбираются с таким расчетом, чтобы при качаниях положительный сигнал, приходящий на инвертирующие входы А5 и А6 был больше отрицательного: |U(+)| > |U(–)|. Прохождение положительного сигнала U(+), при скачкообразном его появлении, замедляется на время, необходимое для заряда конденсатора С до установившегося значения U(+) напряжения. При медленном изменении входного сигнала положительный сигнал проходит без задержки (скорость заряда конденсатора соответствует скорости изменения U(+)).

Для переключения компаратора на его вход 1 должен поступить сигнал отрицательного знака, превосходящий по абсолютному значению опорное напряжение Uoп положительного знака. Последнее поступает от делителя напряжения R16, R17, включенного на источник питания Еп между полюсами + 15 В и 0 В.

Работа схемы БВ2. В нормальном режиме энергосистемы (при отсутствии КЗ и качаний), когда на выходе сумматора схемы БВ1 UΣ = 0 (небаланс скомпенсирован), UвыхБВ1 = 0. Под действием положительного напряжения, поступающего через резисторы на вход И компараторов А5 и А6 (см. рис.12.8), на выходе дежурит отрицательное напряжение Uвыx max, при этом диоды VD2 и VD4 заперты; ПО, а следовательно, и УБК не действуют. В режиме качаний на вход выпрямителя VS1 схемы БВ2 от сумматора схемы БВ1 поступает медленно изменяющееся переменное напряжение нескомпенсированного небаланса (UΣ = Uнб). Возникающие при этом напряжения на выходе VS1 U(–) и U(+) приходят на зажимы И А5 и А6 одновременно, и, так как |U(+)| > |U(–)|, на входе обоих компараторов появляется положительный сигнал, равный разности U(+) – U(–), при котором на их выходе возникает напряжение отрицательного знака. Под воздействием последнего диоды VD2 и VD4 запираются и на выходе логических элементов D1.1 и D1.2 появляется логический сигнал 1, означающий, что ПО не действует.

Таким образом, с помощью рассмотренной схемы БВ2 устраняется влияние медленно изменяющихся сигналов, возникающих при качаниях и асинхронном ходе, на работу ПО: это позволяет обеспечить высокую чувствительность УКБ при удаленных КЗ.

При возникновении несимметричных КЗ на выходе схемы БВ1, а следовательно, и на входе схемы БВ2 немедленно скачком возникает напряжение UΣ = kI2К. В результате этого на выходе выпрямителя VS1 мгновенно возрастают напряжения U3(+) и U4(–) до значения kI2К. С этого момента начинается заряд конденсатора С, что задерживает появление положительного сигнала U(+) = kI2, появляющегося практически без задержки на входе компараторов, а на их выходе возникает положительный сигнал, проходящий через диоды VD2–VD5 на вход логических элементов ИЛИ D1.1 и D1.2. Оба элемента переключаются, и на их выходе появляется логический сигнал, означающий, что ПО блокирующего устройства сработал. Сигнал о срабатывании появляется кратковременно, пока не закончится заряд конденсатора С8, после чего будет преобладать положительный сигнал, при котором D1.1 и D1.2 возвращаются в начальные состояния, соответствующие недействию ПО. Таким образом, в результате инвертирования входного сигнала и задержки прохождения выпрямленного сигнала U(+) происходит выделение составляющей ОП, появляющейся в момент возникновения КЗ. Аналогично выполнен и работает ПО, реагирующий на составляющие прямой последовательности I1.

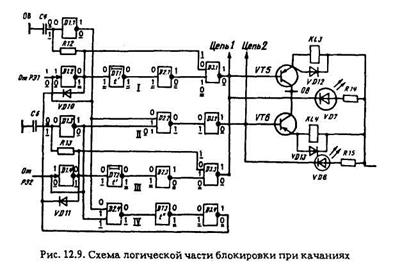

Логическая схема УБК (рис.12.9) предусматривает выполнение операций (см. §12.4). При недействии ПО (что имеет место при нормальном режиме и при качаниях) схема обеспечивает блокирование быстродействующих ступеней ДЗ. При срабатывании ПО УБК логическая схема должна разрешать пуск блокируемых ступеней на время Δt, необходимое для их срабатывания с последующим выводом из работы на заданное время tгот, определяемое по (12.7). В течение этого времени повторный пуск блокируемой ступени ДЗ невозможен. Для устранения этого недостатка в данной схеме предусмотрен повторный пуск заблокированной быстродействующей ступени Действием грубого комплекта ПО, уставка которого отстроена от несимметрии при отключении и включении токов нагрузки.

На рис. 12.9 приведена логическая схема рассматриваемого УБК, применяемая в ДЗ устройства ШДЭ 2801. Логические элементы схемы выполняются с помощью типовых микросхем И-НЕ серии К511. Элементы D3.1–D3.3 работают по схеме И-НЕ при одновременном появлении на их входе логического сигнала 1. Элементы D2.2 и D2.4 реализуют схему ИЛИ-НЕ при подаче на любой из их входов логического сигнала 0. Остальные ЛЭ выполняют логическую операцию НЕ и служат для инвертирования и усиления входного сигнала. Элементы времени DT1–DT3 выполняются по

схеме с использованием контура RC. Они приходят в действие при появлении на входе логического сигнала 1 и возвращаются при 0.

Сигналы UРЭ1 от чувствительного реагирующего элемента ПО УБК поступают на D1.2, а UРЭ2 от грубого реагирующего элемента на D1.4 (рис.12.8 и 12.9). Сигналы от РЭ1 и РЭ2 передаются по четырем каналам. Канал I служит для блокирования и пуска быстродействующих ступеней при действии чувствительного ПО (РЭ1). По каналу II производится блокирование и пуск медленнодействующих ступеней ДЗ по команде чувствительного и грубого ПО (РЭ2). Канал IV осуществляет возврат схемы в состояние готовности к действию по истечении заданного времени вывода tгот = 3–12 с. По каналу III пускаются повторно быстродействующие ступени РЗ при срабатывании грубого ПО.

Логические сигналы, присутствующие на входе и выходе элементов схемы в исходном режиме (при недействии ПО), обозначены цифрами 0 и 1, логические сигналы, появляющиеся при срабатывании ПО изображены подчеркнутыми снизу цифрами 0 и 1.

В исходном режиме схемы на входах D1.2 и D1.3 присутствуют логические 1, а на их выходах логические 0. При этом на выходных элементах логической схемы D3.1, D3.2 и D3.3 дежурят логические сигналы, блокирующие действие всех ступеней РЗ.

Ниже рассматривается работа схемы.

Ввод быстродействующих ступеней защиты на время Δt = 0,2–0,6 с с последующим выводом их. При срабатывании чувствительного ПО РЭ1 на входе элемента D1.2 появляется кратковременно логический сигнал 0, а на выходе 1. Этот единичный сигнал (см. рис.12.9) поступает на три элемента канала I: D3.1, DT.1, D1.1. Логический элемент D3.1 (выходной элемент канала I), выполняющий операцию И-НЕ, получив на свой второй вход сигнал 1, переключается и на его выходе появляется сигнал 0, осуществляющий пуск быстродействующих ступеней (I с t = 0 и II с t < 1,2 с) по цепи 1.

Одновременно приходит в действие элемент времени DT.1. Он срабатывает с установленной выдержкой времени Δt (0,2; 0,4; 0,6 с), на его выходе возникает сигнал 1, который через инвертирующий элемент D2.1, поступает на первый вход D3.1 в виде логического 0. При этом D3.1 возвращается в начальное состояние, на его выходе появляется логический сигнал 1, прекращающий пуск быстродействующих ступеней и блокирующий их действие.

На выходе D1.1, после получения единичного сигнала от D1.2, возникает нулевой сигнал, поступающий на входы D1.2 и D2.4. Как видно из рис.12.9 под воздействием этого сигнала элементы D1.2 и D1.1 самоудерживаются в сработанном состоянии и продолжают пуск схемы после исчезновения кратковременного сигнала от РЭ11. Этим обеспечивается, во-первых, продление пуска

быстродействующих ступеней на время Δt, необходимое для их срабатывания и, во-вторых, по истечении времени Δt удерживание в сработанном состоянии элемента времени DT.1 с сохранением на его выходе сигнала 1. При этом на втором входе D3.1 появляется нулевой сигнал, запрещающий ему переключаться и производить повторный пуск быстродействующих ступеней ДЗ.

|

1 Для исключения ложного срабатывания от помех сигнал на вход D1.1 подается через цепь из R12 и С4, которая замедляет его прохождение на время, превышающее длительность импульсных помех.

Возврат схемы к повторному действию происходит только после прекращения самоудерживания элементов D1.2 и D1.1 по команде IV канала. Под действием нулевого сигнала D1.1 входной элемент канала II D2.2 переключается, в результате этого на выходе D3.2 появляется сигнал 0, производящий по цепи 2 пуск медленнодействующих ступеней (II и III) ДЗ. Кроме того под действием сигнала D1.1 переключается элемент D2.4 (ИЛИ-НЕ) канала IV и подает логический сигнал 1 на элемент времени DT.3, осуществляя его пуск. Через заданное время tгот (3, 6, 9, 12 с) DT.3 срабатывает и на выходе D3.4 возникает логический сигнал 0. Этот нулевой сигнал через диоды VD10 (VD11) поступает на вход DT.1 и на второй вход D3.1 через входы DT.2 и D3.3. Под их действием эти и остальные элементы логической схемы возвращаются в начальное состояние (готовности к повторному действию), что легко проследить по изменению сигналов на элементах схемы. На выходных элементах каналов I, II и III (D3.1, D3.2, D3.3) снова присутствуют единичные сигналы, блокирующие соответствующие ступени РЗ.

Логические элементы D3.1, D3.2, D3.3, кроме пуска и блокирования быстродействующих и медленнодействующих ступеней ДЗ, приводят в действие сигнализацию о работе ПО УБК, осуществляемую светодиодами VD7 и VD8 и герконовые реле KL3 и KL4. Реле KL используются для передачи сигнала на отключение линии с противоположного конца по каналам устройства АНКА.

Работой этих элементов управляют транзисторы VT5 и VT6. В исходном состоянии логической схемы на базы транзисторов подается сигнал 1 — они заперты. При появлении нулевого сигнала транзисторы открываются и приводят в действие соответствующее реле KL.

Ввод в действие ступеней защиты, выведенных из работы после срабатывания чувствительного ПО на заданное время от 3 до 12 с. Для этой цели используется грубый реагирующий орган РЭ2. При срабатывании грубого органа на входе элемента D1.4 появляется логический сигнал 0, а на его выходе — логический сигнал 1. При этом на выходе элемента D3.3 появляется логический сигнал 0 и осуществляется повторный пуск быстродействующих ступеней защиты. С выхода элемента Dl.4 логический сигнал 1 через замедляющую цепь R13, С5 проходит на вход элемента D1.3, и на его выходе появляется логический сигнал 0, поступающий на вход элементов D1.4 и D2.4, чем обеспечивается подхват кратковременного выходного сигнала грубого органа и дополнительный запуск элемента времени DT3. Через время, равное выдержке времени элемента DT2, на его выходе появляется логический сигнал 1, а на выходе элемента D2.3 — логический сигнал 0. При этом на выходе элемента D3.3 появляется логический сигнал 1 и обеспечивается вывод быстродействующих ступеней ДЗ на время выдержки элемента времени DT3, по истечении которого схема возвращается в исходное состояние.

Ввод медленнодействующих ступеней при срабатывании ПО УБК и возврат схемы в исходное состояние. При срабатывании чувствительного или грубого реагирующего элемента ПО логический сигнал 0 появляется также на входах логического элемента D2.2, на его выходе — сигнал 1. При этом на выходе элемента D3.2 появляется сигнал 0 и осуществляется пуск медленнодействующих ступеней защиты на время выдержки элемента DT3 (3, 6, 9, 12 с). По истечении выдержки времени элемента DT3 схема возвращается в исходное состояние, светодиод VD8 гаснет, обеспечивается блокирование медленнодействующих ступеней защиты.

Оценка УБК, реагирующего на приращение векторов тока. Устройство, реагирующее на приращение I2 и I1, имеет следующие преимущества по сравнению с устройствами, реагирующими на абсолютное значение составляющих обратной последовательности I2 и U2 типа КРБ:

1) оно надежно работает при К(3) при отсутствии I2 или недостаточных его значениях;

2) предусмотрено восстановление работы быстродействующей ступени в период, когда ее действие блокируется на время от 3 до 12 с;

3) оно имеет высокую чувствительность, так как не требуется отстройка от тока небаланса и несимметрии токов нагрузки.

Вопросы для самопроверки

1. Каков характер изменения тока, напряжения и сопротивления при качаниях?

2. Какие защиты линий и почему могут сработать в режиме качаний?

3. Виды блокировок при качаниях.

4. Какие ступени дистанционной защиты выполняются с блокировкой при качаниях?

Глава тринадцатая