Количественные характеристики

Количественные характеристики определяют скорость выполнения операций, время выполнения одной операции, точность представления данных,количество выполняемых операций.

Среднюю скорость выполнения операций Vср. в АЛУ можно определить как отношение N(T)- количества операций, выполненных за отрезок времени Т к данному отрезку времени:

Vср = N(T)/T

Среднее время, которое АЛУ тратит на выполнение операции равно:

Tср = 1/Vср

Точность представления данных в АЛУ зависит от разрядной сетки АЛУ и выбранного формата данных.

Качественные характеристики АЛУ:

К качественным характеристикам АЛУ относятся:

- структурные особенности АЛУ;

- форматы представления данных (с фиксированной или плавающей точкой);

- способы кодирования данных.

5. Последовательностные элементы. Асинхронные и синхронные RS-триггеры.

Назначение. Временная диаграмма работы.

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти. Микросхемы с внутренней памятью называются еще последовательными или последовательностными, в отличие от комбинационных микросхем.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной (в отличие от постоянной памяти и перепрограммируемой постоянной памяти, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также сверхоперативной памятью. Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

Триггер можно рассматривать как одноразрядную, а регистр — как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (сдвиговый регистр или, что то же самое, регистр сдвига).

В основе любого триггера (англ. — "тrigger" или "flip-flop") лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

Рис. 7.1. Схема триггерной ячейки

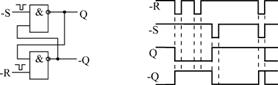

Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

| Таблица 7.1. Таблица истинности триггерной ячейки | |||

| Входы | Выходы | ||

| -R | -S | Q | -Q |

| Без изменения | |||

| Не определено |

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

- RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а).

- JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б).

- D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в).

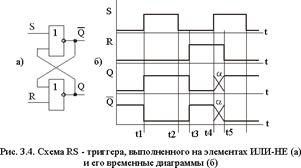

Из временных диаграмм (рис. 3.4, б) следует, что рассмотренные выше RS-триггеры опрокидываются, т.е. управляются сигналами R и S, в любой момент времени. В тех случаях, когда длительности управляющих сигналов не синхронизированы (не согласованы), триггер может находиться в неопределенном состоянии (интервалы времени t4, t5), и поэтому такие триггеры называют асинхронными.

Триггер, построенный на базе элементов ИЛИ-НЕ, называют также дизьюнктивной бистабильной ячейкой. Бистабильные ячейки, помимо самостоятельного применения, входят в качестве составного узла в триггеры других типов.

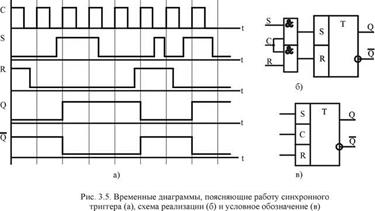

Синхронный RS -триггер.Синхронные триггеры снабжаются дополнительным входом, по которому поступает синхронизирующий (тактирующий) сигнал. При этом изменение состояния триггера происходит (при наличии управляющего сигнала) только в те моменты времени, когда на специальный синхровход триггера поступает тактирующий импульс (рис 3.5, а). Синхронный RS-триггер строится в соответствии с рис. 3.5, б, а его условное изображение на принципиальных и функциональных схемах приведено на рис. 3.5, в. Синхронизирующий вход обозначается буквойС.

Входные сигналы S и R являются информационными, а на входе С - синхронизирующими, по ним происходит переключение триггера. Следует отметить, что для надежной работы триггера необходимо, чтобы длительность переключающего сигнала (синхронизирующего сигнала) на входеС была не меньше времени переключения триггера. Временем переключения (срабатывания, установки) триггера называется время, которое проходит от момента изменения входных сигналов до соответствующего изменения состояния выходов и определяющееся задержками распространения сигнала логическими элементами, входящими в состав триггера.