NTSC/PAL TV decoder circuit

Лабораторная работа №1

Знакомство с отладочным стендом Altera DE 2

1. Цель работы: Ознакомится с отладочным стендом Altera DE 2.

Приобрести навыки работы с технической литературой.

Краткие сведения по отладочному стенду Altera DE 2.

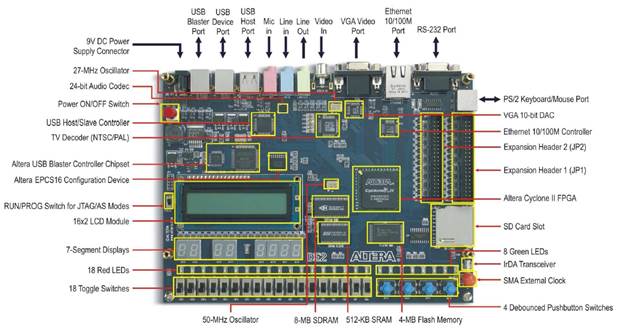

Внешний вид отладочного стенда Altera DE 2 изображен на рисунке 1. Также на рисунке указаны позиционное размещение разъемов и основных компонентов стенда.

|

Рисунок 1 - Отладочный стенд Altera DE 2

В состав стенда входит достаточно большое количество компонентов, что позволяет производить отладку различных проектов, от простейших до мультимедийных.

В состав отладочного стенда Altera DE 2 входят:

· ПЛИС Altera Cyclone® II 2C35 FPGA

· устройство конфигурации Altera - EPCS16

· ОЗУ – 512 Кбайт

· ОЗУ – 8 Мбайт

· Flash память – 4 Мбайта

· приемо-передатчик RS-232

· 50 МГц и 27 МГц – кварцевые генераторы

· 24 битный аудио CODEC

· VGA ЦАП

· TV дешифратор (NTSC/PAL)

· Контроллер10/100М Ethernet

· Контроллер USB Host/Slave

· приемо-передатчик IrDA

· кнопка ВКЛ/ВЫКЛ питания

· переключатель RAN/PROG

· 4 кнопки ключа

· 18 ключей переключателей

· 18 красных светодиодов

· кнопка SMA Extemal clock

· 9 зеленых светодиодов

· 8 семи сегментных индикатора

· 16Х2 ЖКИ дисплей

· разъем для линейного входа

· разъем для микрофонного входа

· разъем для линейного выхода

· разъем VGA видео порта

· разъем TV – входа

· разъем 10/100М Ethernet

· разъем USB тип A

· разъем USB тип Б

· разъем USB для программирования

· 9- штырьковый разъем

· разъем PS/2

· слот для CD карты

· два 40 – штырьковых разъема расширения с диодной защитой

· разъем питания

Структурная схема отладочного стенда Altera DE 2

|

Структурная схема отладочного стенда Altera DE 2 изображена на рисунке 2. Чтобы обеспечивать максимальную гибкость при проектировании, все связи заведены через Циклон II FPGA. Таким образом, потребитель может сконфигурировать FPGA под любое схемотехническое решение.

Рисунок 2 – Структурная схема отладочного стенда Altera DE 2

На рисунке 2 изображены следующие блоки:

Cyclone II 2C35 FPGA

· 33,216 LEs

· 105 M4K RAM blocks

· 483,840 total RAM bits

· 35 embedded multipliers

· 4 PLLs

· 475 user I/O pins

· FineLine BGA 672-pin package

Serial Configuration device and USB Blaster circuit

· Altera’s EPCS16 Serial Configuration device

· On-board USB Blaster for programming and user API control

· JTAG and AS programming modes are supported

SRAM

· 512-Kbyte Static RAM memory chip

· Organized as 256K x 16 bits

· Accessible as memory for the Nios II processor and by the DE2 Control Panel

SDRAM

· 8-Mbyte Single Data Rate Synchronous Dynamic RAM memory chip

· Organized as 1M x 16 bits x 4 banks

· Accessible as memory for the Nios II processor and by the DE2 Control Panel

Flash memory

· 4-Mbyte NOR Flash memory (1 Mbyte on some boards)

· 8-bit data bus

· Accessible as memory for the Nios II processor and by the DE2 Control Panel

SD card socket

· Provides SPI mode for SD Card access

· Accessible as memory for the Nios II processor with the DE2 SD Card Driver

Pushbutton switches

· 4 pushbutton switches

· Debounced by a Schmitt trigger circuit

· Normally high; generates one active-low pulse when the switch is pressed

Toggle switches

· 18 toggle switches for user inputs

· A switch causes logic 0 when in the DOWN (closest to the edge of the DE2 board) position

and logic 1 when in the UP position

Clock inputs

· 50-MHz oscillator

· 27-MHz oscillator

· SMA external clock input

Audio CODEC

· Wolfson WM8731 24-bit sigma-delta audio CODEC

· Line-level input, line-level output, and microphone input jacks

· Sampling frequency: 8 to 96 KHz

· Applications for MP3 players and recorders, PDAs, smart phones, voice recorders, etc.

VGA output

· Uses the ADV7123 240-MHz triple 10-bit high-speed video DAC

· With 15-pin high-density D-sub connector

· Supports up to 1600 x 1200 at 100-Hz refresh rate

· Can be used with the Cyclone II FPGA to implement a high-performance TV Encoder

NTSC/PAL TV decoder circuit

· Uses ADV7181B Multi-format SDTV Video Decoder

· Supports NTSC-(M,J,4.43), PAL-(B/D/G/H/I/M/N), SECAM

· Integrates three 54-MHz 9-bit ADCs

· Clocked from a single 27-MHz oscillator input

· Supports Composite Video (CVBS) RCA jack input.

· Supports digital output formats (8-bit/16-bit): ITU-R BT.656 YCrCb 4:2:2 output + HS, VS,

and FIELD

· Applications: DVD recorders, LCD TV, Set-top boxes, Digital TV, Portable video devices

Ethernet controller

· Integrated MAC and PHY with a general processor interface

· Supports 100Base-T and 10Base-T applications

· Supports full-duplex operation at 10 Mb/s and 100 Mb/s, with auto-MDIX

· Fully compliant with the IEEE 802.3u Specification

· Supports IP/TCP/UDP checksum generation and checking

· Supports back-pressure mode for half-duplex mode flow control