Дешифраторы и шифраторы

Функции дешифраторов и шифраторов понятны из их названий. Дешифратор преобразует входной двоичный код в номер выходного сигнала (дешифрирует код), а шифратор преобразует номер входного сигнала в выходной двоичный код (шифрует номер входного сигнала). Количество выходных сигналов дешифратора и входных сигналов шифратора равно количеству возможных состояний двоичного кода (входного кода у дешифратора и выходного кода у шифратора), то есть 2n, где n — разрядность двоичного кода (рис. 5.1). Микросхемы дешифраторов обозначаются на схемах буквами DC (от английского Decoder), а микросхемы шифраторов — CD (от английского Coder).

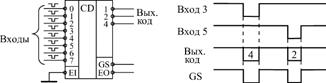

Рис. 5.1. Функции дешифратора (слева) и шифратора (справа)

На выходе дешифратора всегда присутствует только один сигнал, причем номер этого сигнала однозначно определяется входным кодом. Выходной код шифратора однозначно определяется номером входного сигнала.

Шифраторы используются гораздо реже, чем дешифраторы. Это связано с более специфической областью их применения. Значительно меньше и выбор микросхем шифраторов в стандартных сериях. В отечественных сериях шифраторы имеют в названии буквы ИВ.

Стандартное применение шифраторов состоит в сокращении количества сигналов. Например, в случае шифратора ИВ1 информация о восьми входных сигналах сворачивается в три выходных сигнала. Это очень удобно, например, при передаче сигналов на большие расстояния. Правда, входные сигналы не должны приходить одновременно. На рис. 5.10 показаны стандартная схема включения шифратора и временные диаграммы его работы.

Рис. 5.10. Стандартное включение шифратора

Инверсия выходного кода приводит к тому, что при приходе нулевого входного сигнала на выходе формируется не нулевой код, а код 111, то есть 7. Точно так же при приходе, например, третьего входного сигнала на выходе образуется код 100, то есть 4, а при приходе пятого выходного сигнала — код 010, то есть 2.

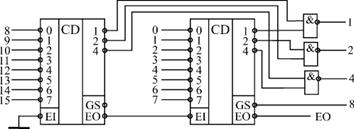

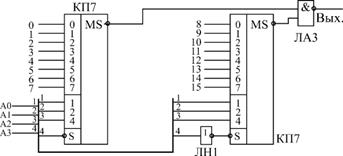

Наличие у шифраторов входов EI и EO позволяет увеличивать количество входов и разрядов шифратора, правда, с помощью дополнительных элементов на выходе. На рис. 5.11 показан пример построения шифратора 16–4 на двух микросхемах шифраторов ИВ1 и трех элементах 2И-НЕ (ЛА3).

Рис. 5.11. Шифратор 16–4 на двух шифраторах 8–3

Одновременное или почти одновременное изменение сигналов на входе шифратора приводит к появлению периодов неопределенности на выходах. Выходной код может на короткое время принимать значение, не соответствующее ни одному из входных сигналов. Поэтому в тех случаях, когда входные сигналы могут приходить одновременно, необходима синхронизация выходного кода, например, с помощью разрешающего сигнала EI, который должен приходить только тогда, когда состояние неопределенности уже закончилось.

Задержка шифратора от входа до выхода кода примерно в полтора раза превышает задержку логического элемента, а задержка до выхода GS — примерно в два раза больше. Точные величины задержек микросхем надо смотреть в справочниках.

Преобразователи кодов

Микросхемы преобразователей кодов (англ. сonverter) служат для преобразования входных двоичных кодов в выходные двоично-десятичные и наоборот - входных двоично-десятичных кодов в выходные двоичные. Они используются довольно редко, так как применение двоично-десятичных кодов ограничено узкой областью, например, они применяются в схемах многоразрядной десятичной индикации. К тому же при правильной организации схемы часто можно обойтись без преобразования в двоично-десятичный код, например, выбирая счетчики, работающие в двоично-десятичном коде. Преобразование двоично-десятичного кода в двоичный встречается еще реже.

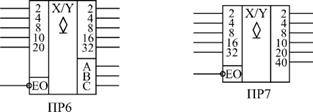

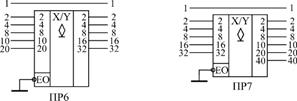

На схемах микросхемы преобразователей обозначаются буквами X/Y. В отечественных сериях преобразователи имеют обозначения ПР.

Кроме того, надо учесть, что любые преобразования параллельных кодов, даже самые экзотические, могут быть легко реализованы на микросхемах постоянной памяти нужного объема. Обычно это намного удобнее, чем брать стандартные микросхемы преобразователей кодов.

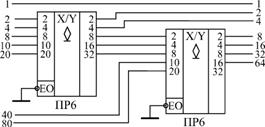

Рис. 6.5. Микросхемы преобразователей кодов

В стандартные серии входят две микросхемы преобразователей кодов: ПР6 для преобразования двоично-десятичного кода в двоичный и ПР7 для преобразования двоичного кода в двоично-десятичный (рис. 6.5). Обе микросхемы имеют выходы ОК, поэтому к ним надо присоединять нагрузочные резисторы величиной около 1 кОм, но для удобства в дальнейших схемах эти резисторы не показаны. Обе микросхемы имеют также вход разрешения выхода -ЕО при нулевом уровне на котором все выходы активны, а при единичном - переходят в состояние единицы. Преобразователь ПР6 имеет дополнительные выходы А, В, С, не участвующие в основном преобразовании.

| Таблица 6.2. Таблица истинности преобразователя ПР6 | ||||||||||

| Входы | Выходы | |||||||||

| -EO | ||||||||||

| X | X | X | X | X | ||||||

Таблицы истинности преобразователей просты (табл. 6.2 и 6.3). Например, двоично-десятичный код без младшего разряда на входе ПР6 преобразуется в двоичный код без младшего разряда на выходе ПР6. Младший разряд не участвует в преобразовании, он непосредственно передается со входа на выход. Одна микросхема ПР6 обрабатывает входные коды в диапазоне от 0 (двоично-десятичный код 00 000) до 39 (код 11 1001).

| Таблица 6.3. Таблица истинности преобразователя ПР7 | |||||||||||

| Входы | Выходы | ||||||||||

| -EO | |||||||||||

| X | X | X | X | X | |||||||

Точно так же двоичный код без младшего разряда на входе ПР7 преобразуется в двоично-десятичный код без младшего разряда на выходе ПР7. Одна микросхема ПР7 может обрабатывать входные коды в диапазоне от 0 (двоичный код 000000) до 63 (код 111111). Младшие разряды входных кодов передаются на выход без обработки в обход микросхемы, так как они одинаковые как в двоичном, так и в двоично-десятичном кодах. Простейшие схемы включения одиночных микросхем ПР6 и ПР7 приведены на рис. 6.6.

Рис. 6.6. Простейшее включение одиночных преобразователей кода ПР6 и ПР7

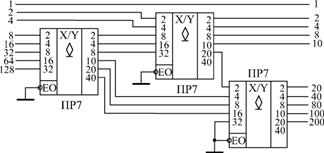

Рис. 6.7. Преобразователь двоично-десятичного кода от 0 до 99 в двоичный код

Каскадировать преобразователи ПР6 и ПР7 для увеличения разрядности также несложно. Для преобразования двоично-десятичных кодов от 0 до 99 достаточно двух микросхем ПР6 (рис. 6.7), а для преобразования двоичных кодов от 0 до 255 требуется три микросхемы ПР7 (рис. 6.8). Если надо преобразовывать двоично-десятичные коды до 999, то понадобится 6 микросхем ПР6, а для преобразования двоичных кодов до 511 потребуется 4 микросхемы ПР7. На всех выходах микросхем необходимо включать нагрузочные резисторы.

Рис. 6.8. Преобразователь двоичного кода от 0 до 255 в двоично-десятичный код

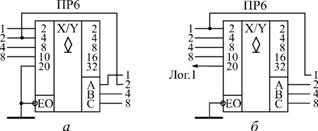

Наличие дополнительных выходов А, В, С у микросхемы ПР6 позволяет преобразовывать двоично-десятичный код от 0 до 9 в код дополнения до 9 или до 10 (рис. 6.9). То есть сумма входного и выходного кодов в этом случае равна, соответственно, 9 или 10. Например, при входном коде 6 на выходе схемы а будет код 3, а на выходе схемы б - код 4. В схеме б при входном коде 0 на выходе также формируется код 0. Как и все остальные выходы микросхемы ПР6, выходы А, В, С имеют тип ОК, поэтому к ним необходимо присоединять нагрузочные резисторы, для удобства не показанные на схеме. Такие схемы "дополнителей" применяются редко, поэтому о них упоминают не во всех справочниках и учебниках, но иногда подобные функции бывают довольно удобны.

Рис. 6.9. Преобразователи входного кода в дополнение до 9 (а) и в дополнение до 10 (б)

Задержки преобразователей кодов примерно вдвое превосходят задержки логических элементов. Точные величины задержек надо смотреть в справочниках.

3. Комбинационные элементы. Мультиплексоры и демультиплексоры.

Номенклатура и характеристики ТТЛ серий.

Мультиплексоры

Мультиплексоры (английское Multiplexer) предназначены для поочередной передачи на один выход одного из нескольких входных сигналов, то есть для их мультиплексирования. Количество мультиплексируемых входов называется количеством каналов мультиплексора, а количество выходов называется числом разрядов мультиплексора. Например, 2-канальный 4-разрядный мультиплексор имеет 4 выхода, на каждый из которых может передаваться один из двух входных сигналов. А 4-канальный 2-разрядный мультиплексор имеет 2 выхода, на каждый из которых может передаваться один из четырех входных сигналов. Число каналов мультиплексоров, входящих в стандартные серии, составляет от 2 до 16, а число разрядов — от 1 до 4, причем чем больше каналов имеет мультиплексор, тем меньше у него разрядов.

Управление работой мультиплексора (выбор номера канала) осуществляется с помощью входного кода адреса. Например, для 4-канального мультиплексора необходим 2-разрядный управляющий (адресный) код, а для 16-канального — 4-разрядный код. Разряды кода обозначаются 1, 2, 4, 8 или А0, А1, А2, А5. Мультиплексоры бывают с выходом 2С и с выходом 3С. Выходы мультиплексоров бывают прямыми и инверсными. Выход 3С позволяет объединять выходы мультиплексоров с выходами других микросхем, а также получать двунаправленные и мультиплексированные линии. Некоторые микросхемы мультиплексоров имеют вход разрешения/запрета С (другое обозначение — S), который при запрете устанавливает прямой выход в нулевой уровень.

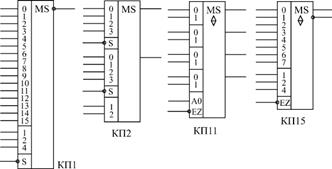

На рис. 5.12 показаны для примера несколько микросхем мультиплексоров из состава стандартных серий. В отечественных сериях мультиплексоры имеют код типа микросхемы КП. На схемах микросхемы мультиплексоров обозначаются буквами MS.

Рис. 5.12. Примеры микросхем мультиплексоров

| Таблица 5.3. Таблица истинности 8-канального мультиплексора | |||||

| Входы | Выходы | ||||

| -EZ | Q | -Q | |||

| X | X | X | Z | Z | |

| D0 | -D0 | ||||

| D1 | -D1 | ||||

| D2 | -D2 | ||||

| D3 | -D3 | ||||

| D4 | -D4 | ||||

| D5 | -D5 | ||||

| D6 | -D6 | ||||

| D7 | -D7 |

В табл. 5.3 в качестве примера приведена таблица истинности одноразрядного 8-канального мультиплексора с выходами 3С (КП15).

В таблице сигналы на входах 0...7 обозначены D0...D7, прямой выход — Q, инверсный выход — –Q, Z — третье состояние выхода. При единице на входе –EZ оба выхода находятся в третьем состоянии. При нуле на входе –EZ выходной сигнал на прямом выходе повторяет состояние входного сигнала, номер которого задается входным кодом на входах 1, 2, 4. Сигнал на инверсном выходе противоположен по полярности сигналу на прямом выходе.

На рис. 5.13 приведена временная диаграмма работы 4-канального мультиплексора. В зависимости от входного кода на выход передается один из четырех входных сигналов. При запрещении работы на выходе устанавливается нулевой сигнал вне зависимости от входных сигналов.

Рис. 5.13. Временная диаграмма работы 4-канального мультиплексора с разрешением

Микросхемы мультиплексоров можно объединять для увеличения количества каналов. Например, два 8-канальных мультиплексора легко объединяются в 16-канальный с помощью инвертора на входах разрешения и элемента 2И-НЕ для смешивания выходных сигналов (рис. 5.14). Старший разряд кода будет при этом выбирать один из двух мультиплексоров. Точно так же из двух 16-канальных мультиплексоров можно сделать 32-канальный. Если нужно большее число каналов, то необходимо вместо инвертора включать дешифратор, на который подаются старшие разряды кода. Выходные сигналы дешифратора будут выбирать один из мультиплексоров.

Рис. 5.14. Объединение мультиплексоров для увеличения количества каналов

Состояния неопределенности, сопровождающиеся короткими паразитными импульсами, могут возникать на выходе мультиплексоров при почти одновременном изменении входных сигналов. Здесь возможны две ситуации. Во-первых, управляющий код может переключаться сразу после изменения передаваемого в данный момент на выход входного сигнала или сразу перед изменением входного сигнала, который будет передавать на выход следующий код. Во-вторых, сигналы (разряды) управляющего кода могут переключаться не одновременно, что приведет к кратковременной передаче на выход входного сигнала, не соответствующего ни одному из значений кода. В любом случае, в момент переключения каналов сигнал на выходе мультиплексора не определен (рис. 5.15).

Чтобы избежать состояния неопределенности, лучше всего задавать состояние управляющего кода еще до начала работы схемы (до прихода входных сигналов) и в дальнейшем его не менять. Если же это невозможно, то необходима синхронизация, стробирование выходного сигнала, то есть его разрешение только тогда, когда все переходные процессы, связанные с изменением кода, уже закончились. Правда, обычно применять стробирование довольно непросто, так как мультиплексор, как правило, должен без изменений передавать любой входной сигнал.

Задержки выходного сигнала мультиплексора по входам управляющего (адресного) кода примерно в два раза превышают задержки логических элементов, а по информационным входам — примерно в полтора раза. Точные величины задержек надо смотреть в справочниках.

Рис. 5.15. Неопределенные состояния на выходе мультиплексорам