Система команд однокристального микропроцессора

Успехи микроэлектроники привели к широкому распространению однокристальных микропроцессоров (ОМП), все компоненты которых реализованы в виде одной БИС. Рассмотрим 8-разрядный ОМП КР580ВМ80.

Основные характеристики ОМП КР580ВМ80: длина информационного слова 8 бит; число основных команд 111 (с модификациями 250); время выполнения команды 2—9 мкс (при длительности такта Т = 0,5 мкс); число РОН 6; адресуемая емкость памяти 64 Кбайт.

Электрические данные: три источника напряжения +5 В, +12 В, —5 В; суммарное потребление около 750 мВт; для всех сигналов стандартные ТТЛ-уровни, кроме двух последовательностей синхросигналов Ф1 и Ф2, которые имеют единичный уровень - 12 В. Используется пластмассовый 40-выводной корпус, кристалл изготавливается по п-МОП-технологии. Структурные особенности: предусмотрены возможность организации прерываний, режим ПДП, асинхронный обмен информацией.

Микропроцессорный комплект КР580, в состав которого входит ОМП КР580ВМ80, содержит около 20 микросхем для построения МП-систем различного назначения.

Структурная схема КР580ВМ80 приведена на рис.2.7. Для нее характерны все черты универсального ОМП: наличие АЛУ с набором регистров (Рг1, Рг2, Ак, PrF) для выполнения заданной совокупности операций; устройства управления в составе регистра команд (РгК); дешифратора команд и шифратора машинного цикла; схем управления и синхронизации, с помощью которых организуется взаимодействие всех элементов МП, а также взаимодействие с внешней средой в процессе его функционирования; системы из трех шин для связи с внешней средой, в том числе двунаправленной 8-разрядной шины данных, однонаправленной 16-разрядной шины адреса и двунаправленной 10-разрядной шины управления. В ОМП предусмотрены средства для организации прерываний, прямого доступа к памяти, асинхронного обмена информацией.

Производится обработка данных в виде 8-разрядных чисел, адресная информация—16-разрядная. В составе МП имеется 8-разрядное АЛУ, обеспечивающее аппаратное выполнение арифметических (сложение, вычитание) и логических (умножение, сложение, инверсия, сложение по модулю 2, сравнение кодов) операций над 8-разрядными двоичными кодами.

Рис.2.7 – Структурная схема микропроцессора ОМП КР580ВМ80

Результат выполнения операций АЛУ, как правило, помещается в накапливающий регистр — аккумулятор (Ак). Содержимое этого регистра обычно используется в качестве одного из операндов в большинстве операций АЛУ.

Вычисление результата операций АЛУ зачастую приводит к формированию определенных признаков, среди которых: признак переноса старшего разряда результата CY (если имеет место перенос, то CY=1); признак нулевого значения результата Z (если результат нулевой, то Z = 1); признак отрицательного результата S (при отрицательном результате S = 1); четного числа единиц в байте результата Р (при четном числе единиц Р=1); вспомогательного переноса между полубайтами результата АС (если имеет место перенос, то АС = 1). Последний признак используется схемой десятичной коррекции при обработке чисел с двоично-десятичным кодированием информации. Остальные признаки применяются для организации условных переходов в программах, выполняемых МП. Признаки (флаги) помещаются в соответствующий регистр (PrF) и хранятся там до момента, пока не будут сформированы новые значения признаков.

В составе МП используется большое число регистров. Часть из них выполняют функции буферных элементов для согласования временных характеристик при передаче информации внутри МП и обмене с внешней средой (Рг1, Рг2, РгК, РгА, буферный регистр в составе шины данных). Другая часть включена в состав блока регистров. В этом блоке имеются 8-разрядные регистры общего назначения (РОН) В, С, D, E, H, L, выполняющие функции сверхоперативной памяти МП. Программное обращение к указанным регистрам позволяет сократить число обменов информацией между МП и внешней средой и тем самым повысить его производительность. Имеется возможность обращения к парам РОН (В и С, D и Е, Н и L) при обработке 16-разрядных чисел. Регистры W и Z используются в качестве буферных при выполнении некоторых операций, программное обращение к ним не предусмотрено. Некоторые из элементов блока регистров выполняют специализированные функции. Среди них 16-разрядный программный счетчик (PC), который служит для формирования адреса очередного байта команды, считываемого из памяти. Содержимое PC может модифицироваться с помощью схемы ± для получения адресов всех байтов команд выполняемой программы. Другим специализированным элементом является 16-разрядный регистр, называемый указателем стека SP. С его помощью в МП-системе организуется стековая память.

Процесс обращения к области ОЗУ, отведенной под такую память, иллюстрирует рис.2.8. Каждый прямоугольник здесь обозначает одну из 8-разрядных ячеек области стековой памяти. Предполагается, что при записи информации заполнение ячеек происходит снизу вверх (заштрихованные прямоугольники). Стрелкой показана верхушка стека — верхний заполненный уровень стековой памяти.

Рис.2.8 – Принцип работы стека

Адрес именно этой ячейки в каждый момент времени задает SP. Запись в стек задается командой МП и предусматривает заполнение двух ячеек, расположенных выше указателя стека, содержимым двух РОН или PC с перемещением вверх на две позиции верхушки стека (рис. .8,б). Считывание информации из стековой памяти также задается определенными командами МП и предусматривает передачу в МП, в пару РОН или PC, содержимого двух ячеек памяти. Адреc одной из них задается SP, другой на единицу больше, чем предыдущий. Освобождение двух ячеек стековой памяти сопровождается понижением верхушки стека на две позиции (рис.8. в). Подобный стек работает по принципу: число, записанное в стек последним, считывается из него первым (такая организация иногда обозначается LIFO — last in first out). Стековая память с организацией LIFO оказывается очень удобной для реализации аппаратных и программных прерываний, так как позволяет после обработки прерывания передавать управление последней программе, которая обрабатывалась до поступления запроса на прерывание. Начальная загрузка PC и SP, предусмотренная определенными командами МП, задает области памяти, отводимые для хранения программ и под стек.

Управление работой МП обеспечивается управляющим автоматом, состоящим из дешифратора команд и шифратора машинного цикла, а также схем управления и синхронизации. В соответствии с кодами команд, поступающими в МП, онобеспечивает генерацию последовательностей сигналов, необходимых для управления всеми элементами МП (подключение сигналов управления к соответствующим элементам на рис.2.7 не показано).

Для связи с внешней средой МП использует систему из трех шин. Двунаправленная 8-разрядная шина данных D позволяет организовать прием в МП команд и операндов и передачу результатов обработки. Она через буферный регистр (на рис.2.7 не показанный в виде отдельного элемента) соединена с внутренней шиной данных, используемой для обмена 8-разрядными кодами между отдельными элементами МП. Однонаправленная 16-разрядная шина адреса А обеспечивает передачу из МП кодов для адресации памяти и устройств ввода-вывода. Обе шины имеют выходы с тремя состояниями. Организация взаимодействия МП с внешней средой обеспечивается десятью цепями, которые образуют шину управления. Для этого используются также слова состояния, выдаваемые из МП на определенных временных интервалах.

МП представляет собой программно-управляемое устройство, которое способно выполнять определенный набор действий (операций), задаваемый соответствующим набором команд. При рассмотрении системы команд МП большую помощь может оказать так называемая программная модель, которая содержит все доступные программисту компоненты МП без указания внутренних связей между ними, состоящая из 10 регистров: шесть РОНов, аккумулятор, счетчик команд, указатель стека, регистр признаков.

PSW

PSW

7 A07 F0

BC

7 B 0 7 C 0

DE

7 D 0 7 E 0

HL

7 H 0 7 L 0

15 SP 0

15 PC 0

T int

Рис.2.9 - Программная модель 8-разрядного ОМП КР580ВМ80

Функции этих компонентов обеспечиваются соответствующими командами МП. На рис.2.9 изображена программная модель 8-разрядного ОМП КР580ВМ80. На ней представлен 8-разрядный накапливающий регистр (аккумулятор) А, содержимое которого в качестве источника или (и) приемника информации участвует в большинстве команд. Рядом с ним находится регистр признаков F, в соответствующих его разрядах показаны все пять используемых признаков. Размещение регистров А и F в программной модели рядом вызвано тем, что их содержимое (обозначаемое PSW) записывается в стек одной командой. Регистры общего назначения В, С, D, Е, Н, L могут быть использованы отдельно либо парами, что определяет их расположение в программной модели. В стек записывается одной командой содержимое пары РОН.

Указатель стека SP и счетчик команд PC всегда оперируют 16-разрядными кодами. Триггер Тint предназначен для хранения запрета прерываний.

Обработка информации и функционирование МП обеспечиваются с помощью программного управления. Программа записывается в ОЗУ в виде последовательности команд. Каждая команда определяет вид операции, исполняемой в данном цикле работы, адреса слов, участвующих в операции, место расположения результата операции, адрес расположения следующей команды. Из-за малой разрядности МП очень трудно задать такую обширную информацию с помощью только одного слова. Проблема выбора формaтa команд и кодирование полей команд МП имеют особое значение. Гибкость МП и его эффективность определяются числом команд и полнотой системы команд, средствами и способами адресации, возможностями организации разветвленных вычислительных процессов.

С увеличением разрядности команды растут и возможности МП. Ограниченная разрядность команды создает существенные трудности в размещении информации о ходе операции и методе адресации данных. Для преодоления этих трудностей в систему команд вводятся операции с удвоенной разрядностью, а также команды с переменной разрядностью.

Кроме поля кода операции и кодов адресов данных команда должна содержать поле признаков с указаниями способов адресации. Способы адресации определяют механизм формирования прямого адреса памяти по полю адреса и полю признаков адресации. Гибкость системы команд в значительной мере определяется разнообразием способов адресации. Выбор системы команд является сложнейшей задачей при построении МП. Команды можно классифицировать по функциональному назначению, по числу адресов, по способу кодирования команд, по длине команды, по способу адресации.

По функциональному назначению различаются команды передачи данных, обработки данных, передачи управления и дополнительные команды. Команды передачи данных включают в себя подгруппы команд передачи кодов между регистрами МП, пересылки кодов между МП и ОЗУ, передачи кодов между МП и внешними устройствами. Команды обработки данных подразделяются на арифметические, логические и команды сдвига. Команды передачи управления используются организации порядка выполнения команд и организации циклических участков в программах. Среди них выделяются команды безусловного и условного переходов Дополнительные команды используются для задания останова программы, начальной установки аппаратных средств, реализации ожидания.

По числу адресов различают нуль-адресные, одноадресные, двухадресные и многоадресные команды.

По способу кодирования различаются команды сфиксированным и расширяющимся полем кода операций.

По длине различают команды длиной водно, два, три байта.

Механизм адресации в значительной мере влияет на эффективность обработки информации в МП. Для преодоления ограничений из-за малой разрядности кодов команд используются всевозможные способы адресации, которые позволяют определитьполный адрес памяти меньшим числом бит, вычислять адреса во время обработки, вычислять адреса данныхотносительно позиции команды таким образом, что можно загружать программу в любую область памяти безизменений адресов в программе. Способы адресации можно разделить на две группы. K первой группе принадлежат способы, вкоторых исполнительный адрес определяется одним значением кодав команде. Такими являются прямая регистровая, косвенная регистровая, непосредственная, автоинкрементная и автодекрементная адресации. Ко второй группепринадлежат такие способы адресации, в которых используется содержимое адресной части команды и нескольких регистров для формирования исполнительного адреса. Такими являются страничная, индексная, относительная адресации.

При прямой адресации код адреса в команде является исполнительным адресом обращения к памяти. При регистровой адресации обрабатываемое слово (операнд) содержится в одном из регистров МП. При регистровой косвенной адресации косвенный адрес извлекается из внутреннего регистра МП. Непосредственная адресация позволяет задавать операнд в команде. Автоинкрементная адресация основана на вычислении исполнительного адреса так же, как и при регистровой косвенной адресации, затем осуществляется увеличение содержимого регистра на некоторую константу.

При автодекрементной адресации сначала из содержимого регистра вычитается константа, затем полученный результат используется в качестве исполнительного адреса. Совместное использование автоинкрементной и автодекрементной адресации обеспечивает применение любого регистра в качестве стека.

При страничной адресации память разбивается на ряд страниц одинаковой длины. Адресация страниц осуществляется с помощью регистра страниц, а адресация ячеек памяти внутри страницы — адресом в команде. Номера всех страниц могут находиться в таблице страниц, которая представляет собой нулевую страницу

Индексная адресация используется при обращении к массивам слов и таблиц. Для образования исполнительного адреса к адресной части команды прибавляется смещение (индекс) из регистра, называемого индексным. Содержимое индексного регистра можно изменять; это позволяет изменять исполнительный адрес без модификации адресной части команды.

При относительной адресации исполнительный адрес образуется сложением базового адреса с адресом команды. В качестве базового адреса используется содержимое программного счетчика. Такая адресация позволяет строить свободно перемещаемые в памяти программы.

Каждая команда МП имеет определенную структуру (формат), в которой можно выделить часть (поле) кода операции (КОП) и поле операнда, определяющее числа (операнды), участвующие в операции в соответствии с КОП. Способ определения операнда на основе структуры команды называется режимом адресации. Использование нескольких режимов адресации расширяет возможности при составлении программы. Как отмечалось ранее, наиболее широко применяются следующие способы адресации:

· неявная адресация, когда место расположения операнда подразумевается и его адрес отдельно ни в какой части команды не задается;

· прямая адресация, предусматривающая запись в поле операнда адреса ячейки памяти с операндом;

· непосредственная адресация, когда в поле операнда находится сам операнд;

· регистровая адресация, когда в поле операнда указывается номер РОН с операндом;

· косвенная адресация, предусматривающая запись в отдельных разрядах КОП номеров РОН, в которых находится адрес ячейки памяти с операндом.

Именно эти способы адресации применяются в МП КР580ВМ80, причем в одной и той же команде может одновременно использоваться несколько способов. Например, в командах для обработки двух чисел один операнд может быть задан регистровой адресацией, а другой — непосредственной. Чаще всего один из операндов подразумевается находящимся в аккумуляторе, туда же помещается и результат выполнения операции.

При обработке информации в МП каждая команда представляет собой двоичный код. Однако при подготовке программ пользователю обычно удобнее применять символические обозначения (мнемокоды) команд (см. табл.2.3). Чаще всего в качестве мнемокодов используются сокращения от английских наименований соответствующих операций. Например, LDA — load direct accumulator (прямая загрузка аккумулятора). Иногда мнемокоды представляют собой слова, определяющие суть выполняемых операций. Например, PUSH — затолкнуть, POP — вытолкнуть. В структуре команд в символическом виде могут приводиться сведения об операндах и адресах, по которым расположены операнды (это могут быть регистры МП, регистровые пары, ячейки памяти М, 8- или 16-разрядные числа, 8- или 16-разрядные адреса).

Таблица 2.3 - Система команд МП КР580ВМ80

| Мнемони-ка | Описание команды | Код ком-ды DDDDDDDD 7 6 5 4 3 2 1 0 | Дл. к-ды байт | Число так- тов | Флаги условий S Z AC P CY |

| MOV R1,R2 | Передача из R2 в R1 | 01DDDSSS | - - - - - | ||

| MOV M,R | Передача из R в память | 01110SSS | - - - - - | ||

| MOV R,M | Передача из памяти в R | 01DDD110 | - - - - - | ||

| MVI R,d8 | Передача байта в R | 00DDD110 | - - - - - | ||

| MVI M,d8 | Передача байта в память | - - - - - | |||

| LXI RP,d16 | Загрузка парных регист- ров BC,DE,HL,SP | 00RP0001 | - - - - - | ||

| LDAX RP | Загрузка аккумулятора по адресу [BC] или [DE] | 00RP1010 | - - - - - | ||

| STAX RP | Занесение содержимого аккумулятора по адресу [BC] или [DE] | 00RP0010 | - - - - - | ||

| LDA adr | Загрузка аккумулятора по адресу, указанному в команде | - - - - - | |||

| STA adr | Занесение содержимого аккумулятора по адресу, указанному в команде | - - - - - | |||

| LHLD adr | Загрузка регистров L,H из двух соседних ячеек, начиная с адреса, ука- занного в команде | - - - - - | |||

| SHLD adr | Занесение содержимого регистров L,H в две со- седние ячейки, начиная с адреса, указанного в команде | - - - - - | |||

| XCHG | Обмен данными между парами регистров HL и DE | - - - - - | |||

| XTHL | Обмен данными между SP и HL | - - - - - | |||

| SPHL | Занесение содержимого регистра HL в SP | - - - - - | |||

| PUSH RP | Ввод содержимого регистров BC,DE, HL в стек | 11RP0101 | - - - - - | ||

| PUSH PSW | Ввод PSW в стек | + + + + + | |||

| POP RP | Выдача данных из стека в регистры BC,HL,DE | 11RP0001 | + + + + + | ||

| POP PSW | Выдача данных из стека в аккумулятор и PSW | + + + + + | |||

| ADD R | Сложение содержимого R и аккумулятора | 10000SSS | + + + + + |

Продолжение таблицы 2.3

| ADC R | То же, но с учетом пе- реноса CY | 10001SSS | + + + + + | ||

| ADD M | Сложение содержимого ячейки памяти и аккуму- лятора | + + + + + | |||

| ADC M | То же, но с учетом пе- реноса CY | + + + + + | |||

| ADI d8 | Сложение байта с содер- жимым аккумулятора | + + + + + | |||

| ACI d8 | То же, но с учетом пе- реноса CY | + + + + + | |||

| DAD RP | Сложение содержимого регистров BC,DE,HL,SP с содержимым HL | 11RP1010 | - - - - - | ||

| SUB R | Вычитание содержимого R из аккумулятора | 10010SSS | + + + + + | ||

| SBB R | То же, но с заемом | 10011SSS | + + + + + | ||

| SUB M | Вычитание содержимого ячейки памяти из акку- мулятора | + + + + + | |||

| SBB M | То же, но с заемом | + + + + + | |||

| SUI | Вычитание байта из со- держимогоаккумулятора | + + + + + | |||

| SBI d8 | То же, но с заемом | + + + + + | |||

| INR R | Увеличение содержимого R на 1 | 00DDD100 | + + + + - | ||

| INR M | Увеличение содержимого ячейки памяти на 1 | + + + + - | |||

| DCR R | Уменьшение содержимого R на 1 | 00DDD101 | + + + + - | ||

| DCR M | Уменьшение содержимого ячейки памяти на 1 | + + + + - | |||

| INX RP | Увеличение содержимого BC,HL,DE,SP на 1 | 00RP0011 | - - - - - | ||

| DCX RP | Уменьшение содержимого BC,HL,DE,SP на 1 | 00RP1011 | - - - - - | ||

| ANA R | Поразрядное логическое умножение содержимого R и аккумулятора | 10100SSS | + + 0 + 0 | ||

| ANA M | Поразрядное логическое умножение содержимого ячейки памяти и акку- мулятора | + + 0 + 0 | |||

| ANI d8 | Поразрядное логическое умножение содержимого аккумулятора и байта | + + 0 + 0 | |||

| XRA R | Поразрядное исключающее ИЛИ над содержимым R и аккумулятора | 10101SSS | + + 0 + 0 |

Продолжение таблицы 2.3

| XRA M | Поразрядное исключающее ИЛИ над содержимым ячейки памяти и акку- мулятора | + + 0 + 0 | |||

| XRI d8 | Поразрядное исключающее ИЛИ над содержимым аккумулятора и байта | + + 0 + 0 | |||

| ORA R | Поразрядное логическое сложение содержимого R и аккумулятора | 10110SSS | + + 0 + 0 | ||

| ORA M | Поразрядное логическое сложение содержимого ячейки памяти и акку- мулятора | + + 0 + 0 | |||

| ORI d8 | Поразрядное логическое сложение содержимого аккумулятора и байта | + + 0 + 0 | |||

| CMP R | Сравнение содержимого R и аккумулятора | 10111SSS | + + + + + | ||

| CMP M | Сравнение содержимого ячейки памяти и акку- мулятора | ||||

| CPI d8 | Сравнение байта с со- держимым аккумулятора | ||||

| RLC | Циклический сдвиг со- держимого аккумулятора влево | - - - - + | |||

| RRC | То же, но вправо | - - - - + | |||

| RAL | Циклический сдвиг со- держимого аккумулятора влево через перенос | - - - - + | |||

| RAR | То же, но вправо | - - - - + | |||

| CMA | Инвертирование аккуму- лятора | - - - - - | |||

| STC | Установка флага переноса CY в 1 | - - - - + | |||

| CMC | Инвертирование флага переноса | + + + + + | |||

| DAA | Двоично-десятичная кор- рекция содержимого ак- кумулятора | - - - - - | |||

| JMP | Безусловный переход | - - - - - | |||

| JC | Переход при переносе | - - - - - | |||

| JNC | То же, при отсутствии переноса | - - - - - | |||

| JZ | То же, при нуле | - - - - - | |||

| JNZ | То же, при отсутствии нуля | - - - - - | |||

| JP | То же, при плюсе | - - - - - | |||

| JM | То же, при минусе | - - - - - |

Продолжение таблицы 2.3

| JPE | То же, при четности | - - - - - | |||

| JPO | То же, при нечетности | - - - - - | |||

| PCHL | Занесение в счетчик ко- манд содержимого регис- тра HL | - - - - - | |||

| CALL | Вызов подпрограммы | - - - - - | |||

| CC | То же, при переносе | 11/17 | - - - - - | ||

| CNC | То же, при отсутствии переноса | 11/17 | - - - - - | ||

| CZ | То же, при нуле | 11/17 | - - - - - | ||

| CNZ | То же, при отсутствии нуля | 11/17 | - - - - - | ||

| CP | То же, при плюсе | 11/17 | - - - - - | ||

| CM | То же, при минусе | 11/17 | - - - - - | ||

| CPE | То же, при четности | 11/17 | - - - - - | ||

| CPO | То же, при нечетности | 11/17 | - - - - - | ||

| RET | Возврат из подпрограммы | - - - - - | |||

| RC | То же, при переносе | 5/11 | - - - - - | ||

| RNC | То же, при отсутствии переноса | 5/11 | - - - - - | ||

| RZ | То же, при нуле | 5/11 | - - - - - | ||

| RNZ | То же, при отсутствии нуля | 5/11 | - - - - - | ||

| RP | То же, при плюсе | 5/11 | - - - - - | ||

| RM | То же, при минусе | 5/11 | - - - - - | ||

| RPE | То же, при четности | 5/11 | - - - - - | ||

| RPO | То же, при нечетности | 5/11 | - - - - - | ||

| RST | Повторный запуск | 11NNN111 | - - - - - | ||

| IN port | Ввод из порта | - - - - - | |||

| OUT port | Вывод в порт | - - - - - | |||

| EI | Разрешить прерывания | - - - - - | |||

| DI | Запретить прерывания | - - - - - | |||

| NOP | Отсутствие операции | - - - - - | |||

| HLT | Останов | - - - - - |

В дальнейшем необходимо пользоваться следующими условными обозначениями:

· DDD,SSS - 3-разрядные поля в формате команды, адресующие один из регистров общего назначения или в качестве места назначения (D), или в качестве источника операнда (S). Кроме имени каждый РОН, а также регистр А имеют трехзначный двоичный код:

000 B 010 D 100 H 110 M

001 C 011 E 101 L 111 A;

· RP - 2-разрядное поле в формате команды, адресующие один из парных регистров - регистровая пара (в мнемокодах команд они записываются единичными буквами B, D, H), а также указатель стека:

00 - BC; 01 - DE; 10 - HL; 11- SP или PSW;

· PSW - слово-состояние программы, 1-й байт которого равен А, 2-й -содержимому RS;

· NNN - двоичное представление номера команды RST;

· + - установка или сброс флага условия;

· – - отсутствие влияние на флаг;

· 5/11 - в знаменателе дроби указано число тактов при выполнении

рассматриваемого в команде условия, в числителе - при невыполнении;

· d8 - байт непосредственного операнда;

· d16 - двухбайтовый непосредственный операнд;

· adr - непосредственный адрес операнда (адрес ячейки памяти);

· port - однобайтовый номер порта;

· R, R1, R2, ...- один из 8-разрядных РОН или аккумулятор.

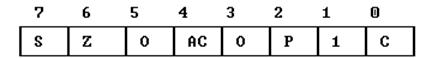

· Регистр признаков F предназначен для хранения 5 признаков (флагов), вырабатываемых при выполнении некоторых операций. Эти признаки (биты условий) хранятся в соответствующих разрядах регистра признаков (рис.2.10).

Y

Рис.2.10 – Регистр признаков F

где S (Sign) - признак знака результата, хранящегося в аккумуляторе. При

положительном знаке S=0, при отрицательном S=1;

Z (Zero) - если содержимое аккумулятора =0, то признак

Z=1, иначе Z=0.

С Y(Carry)- признак переноса. С=1,если при выполнении команд появляется

единица переноса из старшего разряда (переполнение).

АС (Auxiliary Carry)- дополнительный признак переноса. Устанавливается

в единицу, если при выполнении команд возникает единица из

третьего разряда числа (из младшей тетрады в старшую)

P (Parity)- признак четности. P=1, если количество единиц в разрядах

аккумулятора будет четным. Нулевой результат также относится к

четному. В противном случае Р=0.

Разряды 1,3 и 5 в регистре признаков не используются в качестве признаков. Полное описание каждой команды МП должно содержать информацию о том, на какие признаки в регистре F эта команда влияет.

Содержимое пары регистров А и F называют словом состояния программы и обозначают PSW.

Двоичное число, выбранное из памяти и указывающее на выполнение определенной операции, называется командой. Двоичное число, подлежащее обработке, называется операндом.

Используемые ниже обозначения позволяют наряду с записью мнемокодов команд формировать при необходимости их двоичные представления. Программно доступные регистры МП обозначаются символами R. В структуре команд им соответствуют 3-разрядные коды SSS и DDD, которым присвоены двоичные коды, определяющие конкретные регистры МП в соответствии с табл.2.3. Обратим внимание, что коду 110 соответствует ячейка памяти М, адрес которой задается парой регистров HL (при использовании косвенной адресации).

Любая команда имеет мнемоническое (символическое) описание, облегчающее написание программы. Например, ADD (сложить), MOV (переслать), XCHG (обмен содержимым регистровых пар D и H) и др.

В первом столбце таблицы 2.3 приведены мнемокоды команд и соответствующие сведения об операндах. Они могут быть заданы в виде: обозначения 8-разрядного регистра R (источника или приемника) информации; 8-разрядной ячейки памяти М, адрес которой определяется регистровой парой либо указателем стека; 16-разрядного содержимого регистровой пары или указателя стека; 8-разрядного операнда d8, взятого из второго байта двухбайтовой команды; 16-разрядного операнда d16, взятого из второго (младшая часть) и третьего (старшая часть) байтов трехбайтовой команды; 8-разрядного адреса adr устройства (port) ввода-вывода, взятого из второго байта двухбайтовых команд IN и OUT; 16-разрядного адреса adr, взятого из второго (младшая часть) и третьего (старшая часть) байтов трехбайтовой команды.

Во втором столбце табл.2.3 дано сокращенное представление операций, выполняемых соответствующими командами.

Далее в табл.2.3 приводится вариант формата команды. Сопоставление используемого варианта формата команды с содержанием выполняемой операции позволяет сравнительно просто представить последовательность действий МП при выполнении команд. В последeдующих столбцах табл.2.3 указываются число байтов в команде и число машинных тактов Т, требуемое для выполнения команды. Эта информация используется для оценки объема программы и времени ее выполнения

В столбце «Флаги условий» даны сведения о формировании в результате выполнения команд всех пяти признаков. Символ “—” соответствует сохранению признака неизменным; символ “+” - формированию признака на основе анализа результата (см. описание функциональной схемы МП КР580ВМ80); символы 0 или 1 определяют формирование в качестве признака соответствующих констант. В командах выполнения логического умножения (ANA R , ANA M, ANI d8) в качестве признака вспомогательного переноса АС берется содержимое аs результата.

В системе команд обычно выделяется пять групп команд: пересылка кодов; выполнение арифметических операций; выполнение логических операций; передача управления; команды ввода-вывода и специальные.

Команды пересылки кодов предусматривают передачу 8-разрядного кода из регистра в регистр, из регистра в ячейку памяти и обратно, загрузку содержимого второго байта команды в регистр или ячейку памяти. В ряде команд обеспечивается передача 16-разрядного кода из двух ячеек памяти в регистровую пару и обратно, в том числе с использованием области памяти, отведенной под стек. Предусмотрены загрузка регистровой пары содержимым второго и третьего байтов команды и обмен данными между регистровыми парами (HL) и (DE), а также регистровой парой HL и ячейками стековой памяти. В командах пересылки кодов ни один из признаков не формируется.

Рассмотрим несколько примеров представления команд пересылки кодов. Пусть требуется выполнить пересылку кода из РОН L в РОН В.

В соответствии с первой строкой табл.2.3 эту операцию выполняет однобайтовая команда. Мнемокод может быть записан в виде MOV В, L, а двоичный код — 01000101. Аналогично можно определить, что операции пересылки 16-разрядного кода, находящегося во втором и третьем байтах команды, в регистровую пару ВС соответствуют мнемокод LXI ВС,d16 и двоичный код первого байта 00000001.

Команды выполнения арифметических операций обеспечивают сложение и вычитание 8-разрядных чисел, одно из которых находится в аккумуляторе, с помещением результата в аккумулятор. Второе число, участвующее в этих операциях, может задаваться различными режимами адресации (регистровой, косвенной, непосредственной). При выполнении некоторых команд сложения и вычитания предусмотрена возможность учета переноса CY, что позволяет организовать обработку многобайтных чисел отдельными частями. Все команды сложения и вычитания 8-разрядных чисел формируют полный набор признаков результата.

Имеется возможность выполнения сложения 16-разрядных чисел с использованием регистровых пар. В этом случае результат фиксируется в регистровой паре HL и формируется только признак переноса CY. Ряд команд позволяет изменить на единицу в сторону увеличения или уменьшения содержимое регистра, регистровой пары, ячейки памяти М. В результате выполнения этих команд признаков переноса не формируется, а остальные признаки формируются только в операциях с 8-разрядными числами. В этой группе команд особое место занимает команда десятичной коррекции, предусматривающая преобразование содержимого аккумулятора. В связи с тем, что это преобразование основано на выполнении арифметических операций над содержимым полубайтов аккумулятора, то команда отнесена к данной группе.

Команды выполнения логических операций предусматривают реализацию наиболее распространенных логических операций над двумя 8-разрядными кодами, один из которых расположен в аккумуляторе, другой задается различными режимами адресации с помещением результата в аккумулятор. Среди этих операций: логическое умножение, логическое сложение, сложение по модулю 2. Команды сравнения кодов (CMP R, CMP M, CPI d8) выполняются путем вычитания из содержимого аккумулятора второго операнда с формированием всех признаков результата, но без изменения самого содержимого аккумулятора. Имеется команда инвертирования содержимого аккумулятора без формирования признаков результата. В эту же группу команд отнесены команды инвертирования признака переноса и запись в качестве этого признака единичного значения, а также команды поразрядного сдвига содержимого аккумулятора влево и вправо на один разряд (с двумя вариантами формирования признака переноса CY).

Группа команд передачи управления обеспечивает возможность изменения порядка выполнения команд в программе. Среди них команда JMP adr передает управление по адресу, задаваемому вторым и третьим байтами команды, a PCHL — по адресу, взятому из регистровой пары HL (это команды безусловной передачи управления). Команда вызова подпрограммы CALL adr также передает управление по адресу, заданному вторым и третьим байтами но с одновременной записью в стековую память текущего значения PC, что дает возможность возвратиться к прерванной программе. Этот возврат может быть произведен с помощью команды RЕТ, восстанавливающей содержимое PC считыванием его из стековой памяти. Команда RST считывается из внешнего устройства, которое сформировало запрос на прерывание. Она передает управление программе обработки прерывания, начальный адрес которой задается 3-разрядным кодом nnn. Имеются команды, которые выполняют передачу управления, вызов подпрограммы или возврат из нее только в случае выполнения условия (cond), задаваемого соответствующим признаком. Мнемокоды команд условного перехода начинаются буквой J, условного вызова подпрограммы — буквой С, а условного возврата из подпрограммы — буквой R. Далее в мнемокоде идет мнемоническое обозначение условия в соответствии с табл.2.3. Проиллюстрируем это примером. Пусть требуется организовать условный переход по адресу, задаваемому вторым и третьим байтами команды, если значение признака S = 0. На основе табл.2.3 мнемокод —JP adr. Двоичный код первого байта команды 11110010.

В последней группе команд имеется две команды, обеспечивающие ввод-вывод информации через аккумулятор. Второй байт этих команд позволяет адресовать до 256 устройств ввода и столько же устройств вывода. В этой группе имеется также несколько специальных команд. Команды EI и DI, управляющие состоянием триггера Tint, обеспечивают программное разрешение или запрет режима прерывания Команда HLT позволяет остановить выполнение программы, а команда NOP не задает выполнение операции, она позволяет перейти к очередной команде с задержкой на четыре такта Т. Данная группа команд также не влияет на признаки. Так как большинство представленных в табл.2.3 команд имеет обобщенную форму, то они обеспечивают значительное число модификаций с использованием комбинаций регистров, регистровых пар, условий на основе признаков.

Во всех командах разряды КОП располагаются в первом байте.

Возможные варианты однобайтовых команд приведены на рис.2.11.

|

а) д)

б) PUSH 11 0101

POP 0001

LDAX 1010

в) STAX 0010

INX 00 0011

INR 100 DCX 1011

DCR 101 DAD 1001

г) е)

ADD 000

ADC 001

SUB 010 ж)

SBB 011

ANA 100

XRA 101

ORA 110

CMP 111

Рис.2.11 - Варианты однобайтовых команд

Вариант.а рис.2.11 соответствует случаю, когда весь байт команды занимают разряды КОП. Это обычно имеет место либо при неявной адресации операнда (чаще всего подразумевается, что он находится в аккумуляторе), либо когда операнд не используется в команде вообще. В табл. 2.5 приведены мнемокоды и двоичные значения КОП всех команд варианта а.

Таблица 2.5 – Мнемокоды команд, когда весь байт команды занимают

разряды КОП

| Мнемокоды команд варианта а | Значение КОП | Мнемокоды команд варианта а | Значение КОП |

| SPHL | RLC | ||

| XCHG | RRC | ||

| XTHL | RAL | ||

| DAA | RAR | ||

| CMA | PCHL | ||

| CMC | EI | ||

| STC | DI | ||

| RET | HLT | ||

| NOP |

Вариант б рис.2.11 предусматривает использование регистровой адресации. Два левых разряда образуют КОП со значением 01, что соответствует командам пересылки информации из одного РОН в другой. Сами РОН, участвующие в такой пересылке, определяются на основе табл.2.6. Исключение составляет код источника или приемника информации 110, который задает пересылку с участием ячейки памяти М с адресом, взятым из регистровой пары HL (косвенная адресация).

Таблица 2.6 – Трехразрядные коды SSS или DDD, которым присвоены двоичные коды, определяющие конкретные регистры МП

| SSS или DDD | Обозначение регистра |

| B | |

| C | |

| D | |

| E | |

| H | |

| L | |

| M | |

| A |

Варианты в и г рис.2.11 предусматривают регистровую адресацию с использованием одного РОН (источника или приемника информации). На рис.2.11 для этих вариантов представлены мнемокоды всех соответствующих им команд и двоичные значения КОП.

Вариант д рис.2.11 определяет формат однобайтовых команд, в которых участвуют регистровые пары и указатель стека. Приведенные здесь значения разрядов КОП наряду с данными из табл.2.7 позволяют получить двоичные коды соответствующих команд.

Таблица 2.7 – Двухразрядные коды регистровых пар BC, SE, HL, указателя стека, регистров А и F обозначаемые PSW

| Обозначение пары регистров | RP | Мнемокоды команд |

| В | LDAX, STAX DAD, LXI, INX, DCX, PUSH, POP | |

| D | LDAX, STAX DAD, LXI, INX, DCX, PUSH, POP | |

| H | DAD, LXI, INX, DCX, PUSH, POP | |

| SP | DAD, LXI, INX, DCX | |

| PSW | PUSH, POP |

Аналогично вариант е рис.2.11 наряду с данными табл.2.8 может быть использован для нахождения двоичных кодов однобайтовых команд для организации переходов в программах.

Таблица 2.8 – Трехразрядный код, обозначаемый в ряде форматов команд символами ССС, определяющий один из признаков(Z, CY, P, S), используемых для организации перехода в программе

| Условие перехода | ССС | Мнемоническое обозначение условия |

| Неравенство нулю (Z=0) | NZ | |

| Равенство нулю (Z=1) | Z | |

| Отсутствие переноса (CY=0) | NC | |

| Наличие переноса (CY=1) | C | |

| Нечетность (Р=0) | PO | |

| Четность (Р=1) | PE | |

| Положительный результат (S=0) | P | |

| Отрицательный результат (S=1) | M |

Трехразрядный код, обозначаемый символами nnn в варианте ж рис.2.11,используется для определения адреса в команде RST.

Варианты двухбайтовых команд приведены на рис.2.12

з) и)

ADI 000

ACI 001

SUI 010

SBI 011

ANI 100 к)

XRI 101

ORI 110

CPI 111

Рис.2.12 – Варианты двухбайтовых команд

Вариант з рис.2.12 представляет комбинацию неявной и непосредственной адресации. Один из операндов неявно предполагается находящимся в аккумуляторе, другой во втором байте команды (data).

Вариант и рис.2.12 представляет комбинацию регистровой (приемник информации) и непосредственной (источник информации) адресаций.

В варианте к рис.2.12, используемом в командах ввода-вывода, при n=0 задается ввод (IN), при n=1 – вывод (OUT). Второй байт определяет адрес устройства ввода-вывода (adr port).

Варианты трехбайтовых команд представлены на рис.2.13.

|

л) н)

м)

Рис.2.13 - Варианты трехбайтовых команд

Прямая адресация соответствует варианту л. Второй байт определяет младшие разряды, а третий – старшие разряды. В таблице 2.9 приведены мнемокоды и двоичное значение КОП для всех команд варианта л.

Таблица 2.9 - Мнемокоды и двоичное значение КОП для всех команд

варианта л

| Мнемокод команд вариант л | Значение КОП |

| LDA | |

| STA | |

| LHLD | |

| SHLD | |

| JMP | |

| CALL |

Непосредственная адресация с загрузкой содержимым второго и третьего байтов команды регистровой пары или указателя стека используется в варианте м. Выбор приемника информации в соответствии с кодом RP производится на основе таблицы 2.7 (для мнемокода LXI).

Вариант н использует прямую адресацию для организации переходов в программах на основе условий, задаваемой таблицей 2.8.

3 МАТЕРИАЛЫ, ПРИБОРЫ, ОБОРУДОВАНИЕ

Лабораторный практикум проводится с применением персонального компьютера.

4 УКАЗАНИЯ ПО ТЕХНИКЕ БЕЗОПАСНОСТИ

При выполнении лабораторного практикума выполнять требования по охране труда согласно инструкции №328 «Требования по охране труда при работе с компьютерной техникой».