Схема управления регистром

Разработать схему и рассчитать задержку установки и снятия данных на выходе регистра (RG) по сигналу RD, проходящему через микросхемы управления регистром. Микросхемы и регистр заданы в табл. 3. Необходимо обеспечить нормальное функционирование схемы, для чего в схему кроме указанных в заданном варианте (табл. 3) допускается добавлять инвертор К1533ЛН1 [1].

Пример выполнения задания

Исходные данные: микросхемы управления КР1533ЛИ1 и КР1533ЛН1, регистр КР1533ИР23. Схема примера приведена на рис. 5.

С учётом микросхем для получения сигнала управления EZ низкого уровня (для открытия выходного буфера) входные сигналы ADR0 и RD в данной схеме должны быть равны "1".

Задержки сигналов при передаче информации на шину DAT7-DAT0 при открытии выходного буфера регистра (часть сигналов DAT7-DAT0 переходит из состояния Z в состояние L (1), другая часть из Z в H (2)) по сигналу RD составляют:

; (1)

; (1)

. (2)

. (2)

При снятии сигнала RD и закрытии выходного буфера регистра задержки составляют:

.

.

Рис. 5

Таблица 3

| № варианта | Регистр | МС, используемые для управления RG | |

| ИР16 | ЛА2 | ЛЛ4 | |

| ИР38 | ЛИ4 | ЛН1 | |

| ИР15 | ЛА8 | ЛИ4 | |

| ИР15 | ЛИ1 | ЛЕ11 | |

| ИР22 | ЛИ4 | ЛН2 | |

| ИР16 | ЛЕ4 | ЛА2 | |

| ИР34 | ЛА2 | ЛЛ1 | |

| ИР34 | ЛИ3 | ЛН1 | |

| ИР33 | ЛЕ4 | ЛА2 | |

| ИР37 | ЛН2 | ЛИ1 | |

| ИР34 | ЛИ10 | ЛИ8 | |

| ИР22 | ЛА1 | ЛЕ4 | |

| ИР22 | ЛА4 | ЛЕ4 | |

| ИР22 | ЛН1 | ЛИ3 |

Окончание табл. 3

| № варианта | Регистр | МС, используемые для управления RG | |

| ИР38 | ЛЕ1 | ЛЛ1 | |

| ИР34 | ЛН2 | ЛЛ1 | |

| ИР37 | ЛЕ4 | ЛИ1 | |

| ИР33 | ЛА10 | ЛИ3 | |

| ИР34 | ЛИ3 | ЛЕ11 | |

| ИР15 | ЛЕ10 | ЛЛ1 | |

| ИР33 | ЛН2 | ЛИ1 | |

| ИР38 | ЛА10 | ЛА7 | |

| ИР16 | ЛИ2 | ЛЕ11 | |

| ИР34 | ЛЕ4 | ЛА2 | |

| ИР34 | ЛА1 | ЛН1 | |

| ИР16 | ЛИ4 | ЛА7 | |

| ИР15 | ЛЕ10 | ЛИ4 | |

| ИР16 | ЛЕ1 | ЛА3 | |

| ИР34 | ЛЕ4 | ЛЛ4 | |

| ИР23 | ЛА3 | ЛА10 | |

| ИР22 | ЛА1 | ЛА4 | |

| ИР23 | ЛИ3 | ЛА4 | |

| ИР38 | ЛА7 | ЛА3 | |

| ИР33 | ЛЕ11 | ЛЕ10 | |

| ИР33 | ЛН1 | ЛИ8 | |

| ИР22 | ЛЕ1 | ЛЛ1 | |

| ИР38 | ЛА10 | ЛЕ10 | |

| ИР16 | ЛН2 | ЛЛ4 | |

| ИР34 | ЛИ4 | ЛА3 | |

| ИР23 | ЛА8 | ЛИ10 | |

| ИР16 | ЛА1 | ЛЕ10 | |

| ИР16 | ЛА10 | ЛА2 | |

| ИР33 | ЛА7 | ЛЛ4 | |

| ИР15 | ЛН2 | ЛЕ1 | |

| ИР15 | ЛА3 | ЛИ2 | |

| ИР34 | ЛА8 | ЛН1 | |

| ИР22 | ЛИ8 | ЛА8 | |

| ИР22 | ЛЕ4 | ЛИ10 | |

| ИР34 | ЛЕ10 | ЛА8 | |

| ИР37 | ЛИ1 | ЛА4 | |

| ИР15 | ЛЕ4 | ЛИ2 | |

| ИР34 | ЛЕ11 | ЛА4 | |

| ИР37 | ЛА3 | ЛЕ4 | |

| ИР38 | ЛА4 | ЛА10 | |

| ИР16 | ЛИ10 | ЛЛ1 | |

| ИР23 | ЛЕ10 | ЛЛ4 | |

| ИР38 | ЛЕ10 | ЛИ8 | |

| ИР37 | ЛИ3 | ЛЛ1 | |

| ИР37 | ЛИ4 | ЛИ2 | |

| ИР34 | ЛЛ4 | ЛН1 |

Задание 4

Схема управления магистральным приёмопередатчиком

Разработать схему и рассчитать задержку установки и снятия данных на выходе магистрального приёмопередатчика (МПП) по сигналу RD, проходящему через микросхемы управления. Микросхемы и МПП заданы в табл. 4. Необходимо обеспечить нормальное функционирование схемы, для чего в схему кроме указанных в заданном варианте (табл. 4) допускается добавлять инвертор К1533ЛН1 [1].

Пример выполнения задания

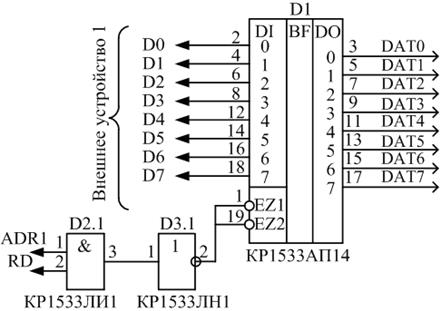

Исходные данные: микросхемы управления КР1533ЛИ1 и КР1533ЛН1, магистральный передатчик КР1533АП14. Схема примера приведена на рис. 6. Входные сигналы ADR1 и RD для открытия выходного буфера МС должны быть равны "1".

Рис. 6

Пример выполнения задания

Задержки сигналов при передаче информации на шину DAT7÷DAT0 при открытии буфера МС по сигналу RD составляют:

;

;

.

.

При снятии сигнала RD и закрытии буфера МС задержки составляют:

;

;

.

.

Таблица 4

| № варианта | МПП | МС управления МПП | |

| АП5 | ЛИ4 | ЛА7 | |

| АП5 | ЛА2 | ЛА2 | |

| АП5 | ЛА3 | ЛИ8 | |

| АП3 | ЛА4 | ЛЕ10 | |

| АП14 | ЛЕ1 | ЛЕ4 | |

| АП4 | ЛЕ11 | ЛА3 | |

| АП4 | ЛА7 | ЛА3 | |

| АП3 | ЛН2 | ЛЛ1 | |

| АП14 | ЛИ2 | ЛА2 | |

| ЛН7 | ЛИ4 | ЛИ4 | |

| АП9 | ЛЕ11 | ЛА10 | |

| АП16 | ЛЛ4 | ЛА10 | |

| АП9 | ЛА8 | ЛН1 | |

| АП15 | ЛИ10 | ЛН2 | |

| АП14 | ЛИ8 | ЛИ4 | |

| АП3 | ЛН2 | ЛА10 | |

| ЛН7 | ЛИ8 | ЛЛ1 | |

| АП3 | ЛИ4 | ЛА3 | |

| АП14 | ЛА7 | ЛА7 | |

| АП4 | ЛА8 | ЛЕ4 | |

| ИП6 | ЛЕ1 | ЛА4 | |

| АП16 | ЛН1 | ЛЕ4 | |

| АП14 | ЛА2 | ЛА4 | |

| АП16 | ЛЕ4 | ЛЕ4 | |

| ИП6 | ЛЕ10 | ЛА10 | |

| АП16 | ЛА1 | ЛЕ1 | |

| АП6 | ЛН2 | ЛЕ10 | |

| АП6 | ЛИ10 | ЛИ8 | |

| АП5 | ЛЕ11 | ЛА2 | |

| ИП6 | ЛЛ4 | ЛЕ11 | |

| АП9 | ЛИ1 | ЛЕ4 | |

| АП6 | ЛИ4 | ЛА3 | |

| АП14 | ЛИ6 | ЛЛ1 | |

| АП3 | ЛА10 | ЛИ3 | |

| АП16 | ЛЕ11 | ЛА3 | |

| ЛН7 | ЛИ1 | ЛН1 | |

| ИП6 | ЛЕ10 | ЛА7 | |

| АП6 | ЛЕ10 | ЛА3 | |

| АП4 | ЛИ1 | ЛЛ1 | |

| АП3 | ЛИ8 | ЛА2 | |

| ЛН7 | ЛИ4 | ЛЕ11 | |

| АП14 | ЛА10 | ЛА1 | |

| АП16 | ЛЕ11 | ЛН1 | |

| АП15 | ЛН2 | ЛН1 | |

| АП5 | ЛИ1 | ЛА1 | |

| АП9 | ЛИ2 | ЛА7 | |

| АП3 | ЛИ2 | ЛЛ4 | |

| ИП6 | ЛЕ11 | ЛИ10 |

Окончание табл. 4

| № варианта | МПП | МС управления МПП | |

| АП14 | ЛЕ11 | ЛЛ4 | |

| АП9 | ЛЛ1 | ЛН2 | |

| АП14 | ЛЛ1 | ЛЕ11 | |

| ЛН7 | ЛН1 | ЛЕ11 | |

| АП9 | ЛА4 | ЛА10 | |

| АП5 | ЛЕ4 | ЛН1 | |

| АП5 | ЛН1 | ЛИ10 | |

| АП16 | ЛА8 | ЛЕ11 | |

| ИП6 | ЛИ3 | ЛИ2 | |

| АП16 | ЛИ2 | ЛИ3 | |

| АП5 | ЛЕ4 | ЛИ2 | |

| АП5 | ЛА3 | ЛА3 |

Задание 5

Дешифратор адреса

Разработать дешифратор адреса (ДА) ААхВВ с задатчиком адреса на микросхемах серии КР1533 [1], указанных в табл. 5, и DC, а также рассчитать необходимые задержки (АА - разрядность шины адреса интерфейса, ВВ - количество адресуемых элементов в проектируемом модуле).

Пример выполнения задания

Рассмотрим пример ДА 10х4, выполненного на МС "Исключающее ИЛИ" (КР1533ЛП5) и дешифраторе DC (КР1533ИД7).

Рис. 7

Временные параметры работы ДА при установке адреса на ША и его снятии в данной схеме рассчитываются по формулам

;

;

.

.

Таблица 5

| № варианта | Логические элементы | "Исключаю-щее ИЛИ" | Цифровые компараторы | Мультиплек- соры | Дешифра- торы |

| 11х14 | 14х7 | 5х5 | 11х15 | 8х9 | |

| 8х6 | 8х14 | 5х2 | 10х5 | 5х14 | |

| 6х12 | 5х6 | 13х8 | 5х5 | 12х9 | |

| 8х12 | 12х8 | 14х13 | 6х8 | 10х5 | |

| 9х13 | 8х4 | 5х4 | 14х14 | 7х13 | |

| 6х5 | 11х5 | 14х9 | 11х11 | 7х9 | |

| 15х6 | 9х14 | 14х14 | 9х14 | 11х9 | |

| 6х13 | 10х12 | 9х3 | 5х4 | 8х14 | |

| 7х15 | 10х13 | 10х2 | 14х6 | 8х2 | |

| 5х9 | 13х12 | 9х5 | 5х10 | 10х7 | |

| 6х4 | 12х2 | 14х9 | 11х9 | 13х10 | |

| 13х7 | 14х7 | 11х2 | 9х2 | 10х10 | |

| 11х4 | 11х7 | 7х13 | 15х8 | 5х13 | |

| 7х10 | 10х10 | 12х6 | 8х8 | 10х14 | |

| 8х12 | 12х7 | 5х7 | 14х3 | 13х12 | |

| 14х5 | 6х3 | 11х8 | 12х11 | 8х6 | |

| 15х12 | 9х12 | 10х11 | 13х10 | 12х11 | |

| 9х8 | 11х8 | 12х7 | 8х11 | 13х3 | |

| 14х4 | 5х2 | 8х15 | 10х11 | 10х12 | |

| 5х8 | 12х14 | 12х4 | 7х9 | 13х11 | |

| 6х13 | 6х10 | 7х11 | 15х8 | 15х2 | |

| 7х6 | 12х2 | 6х10 | 7х12 | 14х11 | |

| 9х5 | 9х7 | 10х9 | 15х9 | 5х2 | |

| 5х4 | 13х8 | 15х2 | 11х2 | 10х2 | |

| 11х5 | 12х5 | 8х13 | 7х9 | 12х2 | |

| 5х13 | 10х7 | 13х10 | 10х10 | 7х14 | |

| 9х14 | 10х13 | 7х4 | 8х2 | 11х7 | |

| 7х8 | 6х8 | 7х15 | 9х11 | 9х6 | |

| 7х6 | 8х13 | 5х10 | 15х6 | 8х10 | |

| 9х7 | 8х3 | 12х8 | 15х14 | 9х5 | |

| 14х12 | 13х9 | 6х15 | 11х15 | 7х7 | |

| 12х10 | 8х11 | 15х12 | 7х10 | 8х13 | |

| 15х12 | 9х12 | 9х15 | 12х10 | 6х6 | |

| 15х13 | 13х7 | 15х10 | 9х12 | 11х14 | |

| 14х7 | 14х14 | 5х12 | 9х3 | 9х13 | |

| 10х2 | 8х4 | 13х7 | 6х10 | 11х6 | |

| 5х14 | 9х4 | 13х8 | 12х3 | 15х8 | |

| 8х6 | 15х9 | 15х10 | 5х3 | 15х11 |

Окончание табл. 5

| № варианта | Логические элементы | "Исключаю-щее ИЛИ" | Цифровые компараторы | Мультиплек- соры | Дешифра- торы |

| 12х10 | 5х14 | 6х15 | 9х8 | 11х11 | |

| 10х15 | 7х9 | 11х10 | 13х5 | 13х3 | |

| 13х14 | 10х6 | 9х7 | 11х6 | 9х7 | |

| 5х3 | 6х4 | 7х13 | 11х11 | 14х13 | |

| 13х10 | 14х6 | 8х13 | 10х14 | 7х2 | |

| 14х11 | 11х9 | 13х13 | 13х6 | 8х8 | |

| 11х4 | 10х6 | 6х6 | 11х6 | 15х9 | |

| 5х2 | 9х15 | 9х5 | 5х8 | 6х8 | |

| 14х6 | 9х4 | 12х10 | 6х13 | 10х15 | |

| 10х7 | 14х14 | 15х13 | 12х6 | 13х2 | |

| 10х10 | 10х14 | 7х6 | 15х6 | 5х12 | |

| 6х9 | 11х12 | 11х13 | 8х12 | 15х5 | |

| 10х10 | 13х11 | 5х11 | 10х11 | 15х12 | |

| 7х15 | 12х7 | 14х12 | 15х12 | 6х10 | |

| 10х8 | 14х13 | 11х13 | 10х4 | 14х10 | |

| 15х15 | 6х3 | 6х12 | 14х4 | 15х12 | |

| 5х11 | 12х2 | 7х2 | 8х4 | 13х9 | |

| 10х10 | 9х7 | 15х9 | 7х13 | 6х13 | |

| 12х13 | 15х13 | 7х9 | 7х2 | 12х13 | |

| 6х10 | 14х11 | 13х5 | 7х10 | 10х10 | |

| 11х9 | 10х5 | 8х4 | 14х10 | 13х8 | |

| 8х5 | 6х13 | 5х4 | 14х13 | 10х8 |

Задание 6

Модуль входных сигналов

Разработать структурную схему модуля входных сигналов в соответствии с вариантом задания (табл. 6). В таблицах с 6 по 11 использованы следующие обозначения: МПИ, И41 - магистральные параллельные интерфейсы; ШД - разрядность шины данных; RDY - сигнал готовности внешнего устройства (ВУ); АДР - режим адресного обмена; ПР - обмен в режиме прерывания программы; ДИАГН - диагностика модуля. Примеры модулей рассмотрены в [7].

Таблица 6

| № варианта | Интерфейс | Режим обмена | ШД | Входы |

| МПИ | ПР (по всем сигналам) | |||

| МПИ | АДР | |||

| И41 | ПР+ДИАГН (ПР по всем сигналам) | |||

| И41 | ПР (по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| И41 | ПР (по всем сигналам) | |||

| И41 | АДР+ДИАГН | |||

| И41 | АДР+ДИАГН | |||

| И41 | АДР | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) |

Продолжение табл. 6

| № варианта | Интерфейс | Режим обмена | ШД | Входы |

| И41 | АДР | |||

| И41 | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | АДР | |||

| И41 | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| И41 | ПР (по RDY ВУ) | |||

| И41 | ПР+ДИАГН (ПР по RDY ВУ) | |||

| МПИ | АДР+ДИАГН | |||

| МПИ | ПР (по всем сигналам) | |||

| И41 | ПР (по всем сигналам) | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | АДР | |||

| И41 | ПР (по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | АДР | |||

| И41 | АДР | |||

| И41 | АДР+ДИАГН | |||

| И41 | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | ПР (по RDY ВУ) | |||

| И41 | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | АДР | |||

| И41 | АДР+ДИАГН | |||

| МПИ | ПР (по всем сигналам) | |||

| МПИ | АДР+ДИАГН | |||

| И41 | ПР (по RDY ВУ) | |||

| И41 | ПР (по всем сигналам) | |||

| И41 | АДР+ДИАГН | |||

| МПИ | АДР+ДИАГН | |||

| И41 | ПР (по RDY ВУ) | |||

| МПИ | ПР (по всем сигналам) | |||

| И41 | АДР+ДИАГН | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | ПР (по всем сигналам) | |||

| МПИ | АДР | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | АДР+ДИАГН | |||

| МПИ | АДР+ДИАГН | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | АДР | |||

| И41 | ПР+ДИАГН (ПР по всем сигналам) |

Окончание табл. 6

| № варианта | Интерфейс | Режим обмена | ШД | Входы |

| И41 | ПР (по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по RDY ВУ) | |||

| И41 | ПР (по RDY ВУ) | |||

| МПИ | ПР+ДИАГН (ПР по всем сигналам) | |||

| МПИ | ПР (по RDY ВУ) | |||

| МПИ | ПР (по всем сигналам) |

Задание 7