Основы проектирования на плис 4 страница

8. Элемент XOR2. Назначение выводов: I0, I1,-входы, О-выход. Выполняемая функция О=I0^I1. Таблица истинности элемента ХOR2 приведена в таблице 8.

Таблица 8- таблица истинности элемента ХOR2

| Входы | Выход | |

| I0 | I1 | О |

9. Элемент XOR4. Назначение выводов: I0, I1,I2, I3 -входы, О-выход. Выполняемая функция О=I0^I1^I2^I3.Таблица истинности элемента XOR4 может быть получена из предыдущих материалов.

Содержание отчета

Отчет по каждой работе должен содержать: название работы, ее цель, результаты, схемы и вывод по работе.

Лабораторная работа №3

Комбинационная схема

Цель: Изучение способов комбинирования логических элементов в схемы.

Приборы: Стенд на основе ПЛИС XC9572XL, программа XilinxISEDesignSuite14.4

Общие указания:

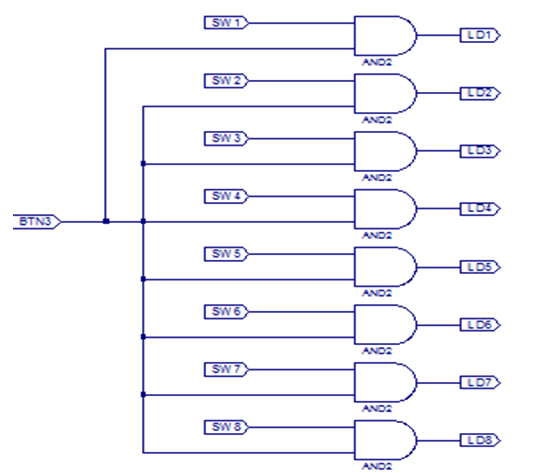

1. При нажатии кнопки BTN3 происходит зажигание светодиодов LD8-LD1 в соответствии с положением переключателей SW8-SW1 соответственно.

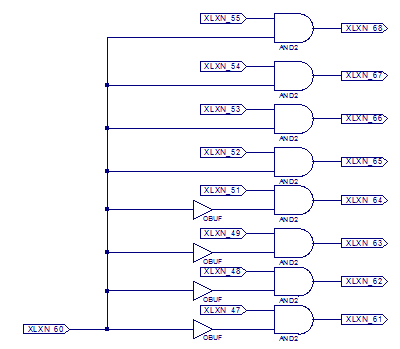

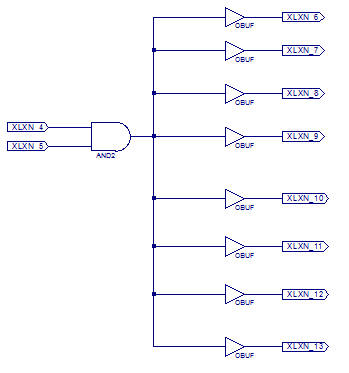

На рисунке 32 изображен первый вариант комбинационной схемы для исследования

Рисунок 3.25. - Схема 1

2. При нажатии кнопки BTN5 светодиоды LD8-LD5 загораются в соответствии с инвертирующими значениями переключателей SW8-SW5 соответственно. Светодиоды LD4-LD1 загораются в соответствии с положением переключателей SW4-SW1.

На рисунке 3.26 изображен второй вариант исследований (см. рис. 3.26)

Рисунок 3.26 - Схема 2

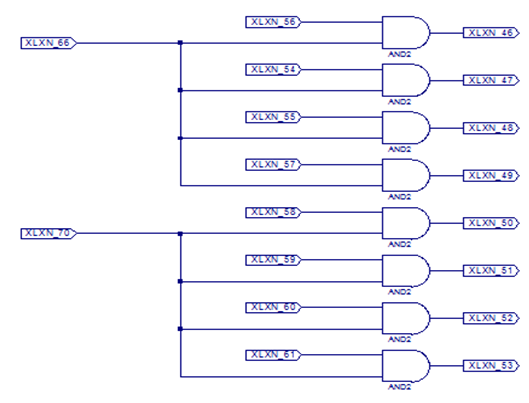

3. При нажатии BTN1 загорание светодиодов LD8-LD5 происходит в соответствии с переключателями SW8-SW5, а загорание светодиодов LD4-LD1 происходит в соответствии с инвертирующим значением переключателей SW4-SW1.

На рисунке 3.27 изображена схема 3

Рисунок 3.27-Схема 3

4. Принажатии кнопки BTN4 или BTN2 загорание всех светодиодов происходит в соответствии с инвертированными значениями соответствующих переключателей.

На рисунке 3.28 изображена схема 4

Рисунок 3.28 - Схема 4

Содержание ответа: Отчет по каждой работе должен содержать: название работы, ее цель, результаты, схемы и вывод по работе.

Лабораторная работа №4

Конечно – автоматные структуры

Цель: Ознакомление с программированием и использованием триггеров. Изучение элементов: FD, LD, FDCP, FTC, CB4CE, CD4CE, COMP4, D2_4E, D3_8E, D4_E16, M2_1, M4_1E.

Общие указания:

1. FD- D триггер. Назначение выводов:D - информационный вход; D. С - вход синхронизации; Q – выход. Таблица истинности элемента FD приведена в таблице 1

Таблица 1- Таблица истинности элемента FD

| Вход С | Вход D | Выход Q | Режим Работы |

| / | Загрузка 0 (сброс) | ||

| / | Загрузка 1 (установка) | ||

| Х |  | Хранение | |

| Х |  | Хранение 0 |

2. LD– D Триггер с потенциальным управлением (D- защелка). Назначение выводов:D - информационный вход ; G - вход синхронизации; Q – выход. В отличие от предыдущего варианта, вход синхронизации отсутствует. Обычно такие триггеры используются как последовательные регистровые схемы или элементы задержки.

Таблица истинности элемента LD приведена в таблице 2.

Таблица 2- Таблица истинности элемента LD

| Вход G | Вход D | Выход Q | Режим работы |

| Передача данных со входа D(0) на выход триггера | |||

| Передача данных со входа D(1) на выход триггера | |||

| / | Фиксация входных данных (0) в триггере | ||

| / | Фиксация входных данных (1) в триггере | ||

| Х |  | Хранение |

3. FDCP- D триггер с асинхронным сбросом и асинхронной установкой. Назначение выводов: D-информационный вход D; C-Вход синхронизации; CLR-вход сброса; PRE-вход установки,Q- выход. Таблица истинности элемента FDCP приведена в таблице 3.

Таблица 3- Таблица истинности элемента FDCP

| Вход CLR | Вход PRE | Вход С | Вход D | Выход Q | Режим работы |

| / | Загрузка 0 (сброс) | ||||

| / | Загрузка 1(установка) | ||||

| Х |  | Хранение | |||

| Х |  | Хранение | |||

| Х | Х | Асинхронная установка | |||

| Х | Х | Х | Асинхронный сброс |

4. FTC- Tриггер с асинхронным сбросом. Назначение выводов: С-вход синхронизации; Т-вход разрешения переключений; CLR-вход сброса; Q- выход.

Таблица истинности элемента FTC приведена в таблице 14.

Таблица 4- Таблица истинности элемента FTC

| Вход CLR | Вход Т | Вход С | Выход Q | Режим Работы |

| / |  | Переключение | ||

| Х |  | Хранение | ||

| Х |  | Хранение | ||

| Х |  | Хранение | ||

| Х | Х | Асинхронный Сброс |

5. СВ4СЕ- четырехразрядный двоичный счетчик с асинхронным сбросом и входом разрешения счета.

Таблица 5- Таблица истинности элемента СВ4СЕ

| С | CLR | СЕ | QI | TC | CEO | Режим работы |

| Х | Х | Асинхронный сброс | ||||

| / | Счет | Счет (Q[3;0]#1111) | ||||

| / | Счет | Счет Q[3;0]=1111) | ||||

| Х |  |  | Хранение |

Назначение выводов: С- тактовый вход; СЕ- вход разрешения счета; CLR-вход сброса; Q0-Q3- выходы (0-3 разряды); ТС-выход переноса (выход завершения счета); СЕО- выход разрешения счета (СЕО=ТС&СЕ).

Таблица истинности СВ4СЕ приведена в таблице 5.

6.СD4СЕ- четырехразрядный двоично-десятичный счетчик с асинхронным сбросом и входом разрешения счета. Назначение выводов: С- тактовый вход, СЕ-вход разрешения счета, CLR-вход сброса, Q0-Q3- выходы (0-3 разряды), ТС-выход переноса (выход завершения счета), СЕО-выход разрешения счета (СЕО=ТС&СЕ).Таблица истинности элемента СD4СЕ приведена в таблице 6.

Таблица 6- таблица истинности элемента СD4СЕ

| C | CLR | СЕ | QI | TC | CEO | Режим работы |

| Х | Х | Асинхронный сброс | ||||

| / | Счет | Счет (Q[3;0]=1111) | ||||

| / | Счет | Счет (Q[3;0]=1111) | ||||

| Х |  |  | Хранение |

7.СОМР4 - цифровой четырехразрядный компаратор. Назначение выводов: А0-А3-выходы первого операнда(разряды 0-3), В0-В3-выходы второго операнда(разряды 0-3), EQ- выход А=В. Таблица истинности элемента СОМР приведена в таблице 7.

Таблица 7- таблица истинности элемента СОМР

| Соотношение значений сигналов на входах А0-А3, В0-В3 | Выход EQ |

| IA0=IB0 и IA1=IB1 и IA2=IB2 и IA3=IB3 | |

| IA0#IB0 или IA1#IB1 или IA2#IB2 или IA3#IB3 |

8. D2_4E- дешифратор с 2 на 4 со входом разрешения, преобразующий двухразрядный двоичный код, поступающий на входы А0 А1, в напряжение высокого уровня, появляющиеся на одном из четырех входов D0-D3, при наличии сигнала высокого уровня на входе Е. Таблица истинности элемента D2_4E приведена в табл. 8.

Таблица 8- Таблица истинности элемента D2_4E

| Е | А0 | А1 | D0 | D1 | D2 | D3 | Режим работы |

| Преобразование двоичного кода в напряжение высокого уровня на соответствующем выходе | |||||||

| Х | Х | Стробирование |

9. D3_8E- дешифратор с 3 на 8 со входом разрешения, преобразующий трехразрядный двоичный код, поступающий на входы А0-А2, в напряжение при наличии сигнала высокого уровня на входе Е.

10. D4_16E- дешифратор с 4 на 16 со входом разрешения, преобразующий двухразрядный двоичный код, поступающий входы А0-А3, в напряжение высокого уровня, появляющиеся на одном из четырех входов D0-D15, при наличии сигнала высокого уровня на входе Е. Назначение выводов: Е-вход разрешения, А0-А3-входы (разряды 0-3), D0-D15-выходы(0-15 разряды).

11. М2_1- двухвходовый мультиплексор (2 в 1) с инверсией по одному входу. Назначение выводов D0, D1- информационные входы,S0-вход выбора, O-выход.

12. М4_1Е-четырехвходовый мультиплексор (4 в 1) со стробированием. Назначение выводов: D0-D3-информационные входы,S0,S1- входы выбора,O-выход.

Лабораторная работа №5

Делитель частоты

Цель:ознакомиться с принципами деления частоты.

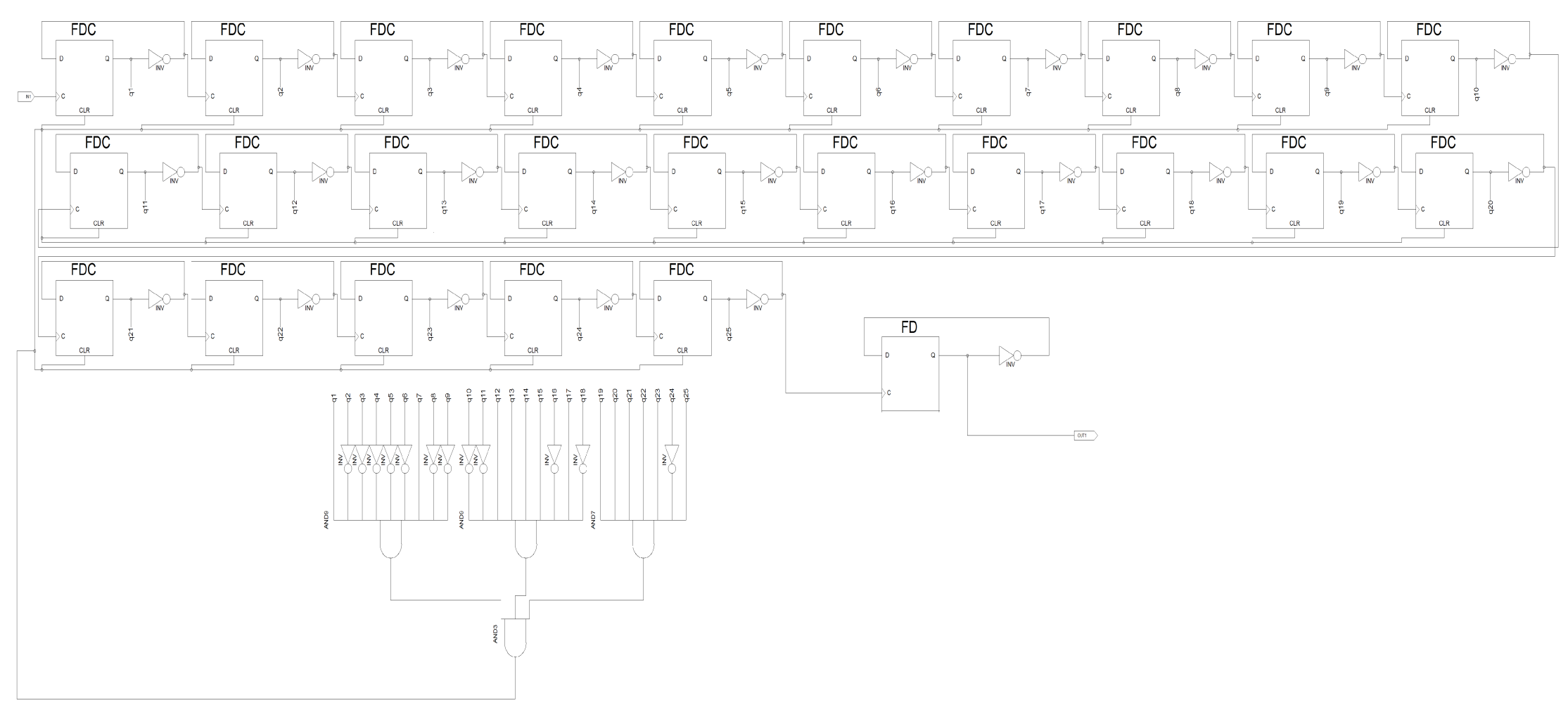

Общие указания:Построить делитель частоты, чтобы 50МГц делилось в 5*106 раз , чтобы получить в итоге 1Гц. Построить делитель частоты на D-триггерах. Необходимо выбрать количества триггеров и собрать схему, соответствующую заданию.

1. Деление будет производиться в 2 этапа. На первом этапе частота делится на 25000000 раз, в итоге получаются короткие импульсы с частотой в 2 Гц. На следующем этапе импульсы подаются на Т-триггер для формирования меандра с частотой 1Гц.

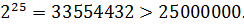

3.Необходимо составить схему, состоящую из 25 D- триггеров, т.к.

4. Необходимо организовать элемент, который будет сбрасывать все триггеры в ноль по приходу 25000000-ого импульса. Сигнал сброса будет подаваться на Т-триггер.

На рисунке 3.30 изображена схема делителя частоты.

Рисунок 3.30 - Схема делителя частоты.

Лабораторная работа №6