MVI B,0 ;обнуляем регистр В

DAD B ;(H-L) ← (H-L)+(B-C)

MOV A,M ;(A) ←([H-L])

MOV C,A ;(C) ←(A)

JMP M1

NAT: db 0Еh,0h,0h,0h,0h,0h,0h,0h,4h,0h,0h,0h,8h

Include stack.asm

End

Алгоритм программы (основной) формирователя сигналов сложной формы

| Инициализация системы |

Установка нач. сост-я счетч Й  |

Формирование задержки  |

Ввод управляющих сигналов  |

Хранение  |

Выделение  |

|

| Да |

| Нет |

Выделение  |

|

| Да |

Инкремент счетчика  |

|

| Да |

| Нет |

| Нет |

Преобр. кода  , вывод yyYYYYYYYYYYYY , вывод yyYYYYYYYYYYYY  |

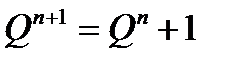

Алгоритм преобразователя кода (Блок 2)

|

Алгоритма временной задержки

(Блок 3)

| 3.5 |

| 3.4 |

| 3.3 |

| 3.2 |

| 3.1 |

| Загрузка в регистровую пару BC константа V |

| Декремент регистровой парыBC |

Формирование признака ненулевого результата  |

| Пустые команды |

|

| Да |

| Нет |

Программа формирователя сигналов сложной формы

INPORT equ 1

OUTPORT equ 2

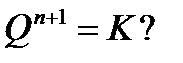

K equ 9

DEL equ 2h

includeinit.asm

BEGIN:

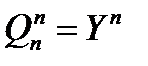

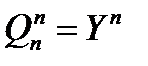

M1 MVIC,00

M2 JMPPREOBR

M3 JMP DELAY

M4 IN INPORT

MOV B,A

ANI 01h

JZ M1

MOVA,B

ANI02h

JZM2

INR C

MOVA,C

SUI K

JZ M1

JMPM2

PREOBR:

LXI H,NAT

MOV E,C

MVID,0

DADD

MOV A,M

OUT OUTPORT

JMP M3

DELAY:

PUSH B

LXI B,DEL

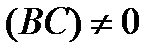

M5 DCX B

MOV A,C

ORA B

NOP

NOP

NOP

JNZ M5

POP B

JMP M4

NAT:

db 99h,0CBh,0E4h,0E4h,0CBh,0FDh,0E4h,0CBh,80h

include stack.asm

End

Лекция

Организация интерфейса ввода/вывода данных

Способы организации ввода/вывода данных в микропроцессор.

Интерфейс – совокупность унифицированных технических и программных средств, необходимых для подключения внешних устройств к МП. Например, АЗУ, ПЗУ, устройства ввода/вывода.

Интерфейс ввода/вывода данных предназначен для следующих задач:

· Синхронизация между МП и устройствами ввода/вывода данных.

· Выбор направления и способа обмена данных между МП и устройствами ввода/вывода данных.

Направление - ввод или вывод.

Способ передачи – параллельный или последовательный обмен.

Приведение в соответствие уровней и форм сигналов.

В микропроцессорной системе (МПС) организованы 2 способа организации ввода/вывода данных:

1) Ввод/вывод данных только с использованием аккумулятора (в изучаемом 8-ми разрядном МП).

2) Обмен данными, минуя аккумулятор и центральный микропроцессор (режим ПДП).

Режим ПДП или обмен данными прямого доступа между запоминающим устройством и устройствами ввода/вывода данных. ПДП – прямой доступ к памяти.