Методы проектирования одного разряда искусственного нейрона на многоуровневых схемах памяти

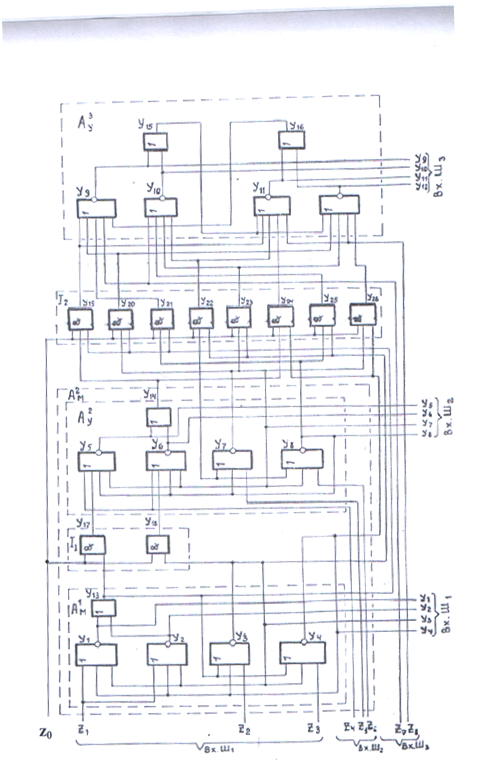

Рассмотрим схему трехуровневого элементарного искусственного нейрона на МУСП (рис. 12.6) и его работу.

| Рис. 12.6.Трехуровневое устройство элементарного нейрона |

Каждая МФСП  (j = 1, 2, 3) состоит из четырех (n = 4) логических элементов ИЛИ-НЕ, разбитых на mj (2 ≤ mj≤ 4) групп. Элементы

(j = 1, 2, 3) состоит из четырех (n = 4) логических элементов ИЛИ-НЕ, разбитых на mj (2 ≤ mj≤ 4) групп. Элементы  и

и  разбиты на три группы так, что в одной группе находится два логических элемента ИЛИ-НЕ, а в двух остальных группах по одному. Элементы МФСП

разбиты на три группы так, что в одной группе находится два логических элемента ИЛИ-НЕ, а в двух остальных группах по одному. Элементы МФСП  разбиты на две группы по два элемента ИЛИ-НЕ в каждой. Число Mj запоминаемых состояний в каждой МФСП

разбиты на две группы по два элемента ИЛИ-НЕ в каждой. Число Mj запоминаемых состояний в каждой МФСП  определяются по формуле (4.4) и (4.10):

определяются по формуле (4.4) и (4.10):

М1 = М2 = (22 -1) + (21 -1) + (21 -1) = 5;

М3 = (22 -1) + (22 -1) = 6.

В тех группах, где число БА больше 1 (Ri > 1)i, выходы БА взаимосвязаны с входами БА других групп через логический элемент ИЛИ, что сокращает межгрупповые связи в МФСП  .

.

Выходы БА тех групп, где Ri = 1, и логических элементов ИЛИ тех групп, где Ri > 1, МФСП  и

и  поступают на тактируемые управляющим входом z0 логические элементы И комбинационных схем I1 и I2.

поступают на тактируемые управляющим входом z0 логические элементы И комбинационных схем I1 и I2.

Числа re сохраняющих входных сигналов в МФСП  и

и  определяются по формуле (4.14):

определяются по формуле (4.14):

re2 = (22 -1) × (21 -1) × (21 -1) =3;

re3 = (22 -1) × (22 -1) =6.

Зная число rej сохраняющих входных сигналов e(Δ), которые управляют МФСП  , можно определить необходимое число rуi логических элементов И комбинационных схем I1 и I2 по формуле (5.9).

, можно определить необходимое число rуi логических элементов И комбинационных схем I1 и I2 по формуле (5.9).

rу1 = 3 – 1 = 2; rу2 = 9 – 1 = 8.

Число М3 запоминаемых состояний трехуровневой памяти определяется по формуле (5.3):

М3 = 3 × 3 × 2 = 18.

Выходы комбинационных схем I1 и I2 поступают на входы БА управляемых МФСП  тех групп, где число БА более одного (Ri > 1). Связи между выходами элементов И схемы I1 и входами БА МФСП

тех групп, где число БА более одного (Ri > 1). Связи между выходами элементов И схемы I1 и входами БА МФСП  и между выходами элементов И схемы I2 и входами БА МФСП

и между выходами элементов И схемы I2 и входами БА МФСП  определяются из значений ej(Δ) входных сигналов МФСП

определяются из значений ej(Δ) входных сигналов МФСП  и

и  . Сохраняющие ej(Δ) входные сигналы характеризуются тем, что хотя бы в двух группах БА на входных узлах значение должно быть равно одному логическому нулю. Сохраняющие ej(Δ) входные сигналы МФСП

. Сохраняющие ej(Δ) входные сигналы характеризуются тем, что хотя бы в двух группах БА на входных узлах значение должно быть равно одному логическому нулю. Сохраняющие ej(Δ) входные сигналы МФСП  и

и  представлены в табл. 12. 1 и 12.2.

представлены в табл. 12. 1 и 12.2.

Таблица 12.1

Сохраняющие ej(Δ) входные сигналы МФСП

| Значение сигналов  на входах элементов yi на входах элементов yi | |||

| y5 | y6 | y7 | y8 | |

| ||||

| ||||

|

Таблица 12.2

Сохраняющие ej(Δ) входные сигналы МФСП

| Значение сигналов  на входах элементов yi на входах элементов yi | |||

| y9 | y10 | y11 | y12 | |

| ||||

| ||||

| ||||

| ||||

| ||||

| ||||

| ||||

| ||||

|

В соответствии с табл. 12.1 и 12.2 выходы элементов И схем Ij (j = 1, 2) и входами соответствующих МФСП  (j = 1, 2) определяются единичными значениями ej(Δ) входных сигналов МФСП

(j = 1, 2) определяются единичными значениями ej(Δ) входных сигналов МФСП  . Например, вход y17 элемента И схемы I1 соединяется в соответствии с табл. 12.1 со входом элемента y5, а выход y18 второго элемента И схемы I1 соединяется со входом элемента y6 МФСП

. Например, вход y17 элемента И схемы I1 соединяется в соответствии с табл. 12.1 со входом элемента y5, а выход y18 второго элемента И схемы I1 соединяется со входом элемента y6 МФСП  . Таким образом, в соответствии с табл. 12.2 (рис. 12.6) соединяются выходы элементов y9 – y12 МФСП

. Таким образом, в соответствии с табл. 12.2 (рис. 12.6) соединяются выходы элементов y9 – y12 МФСП  . Устанавливающие xi(t) входные сигналы имеют на входе только одной группы значении логического нуля, а на входах всех остальных групп МФСП значения логических единиц. Входные сигналы xi(t) МФСП

. Устанавливающие xi(t) входные сигналы имеют на входе только одной группы значении логического нуля, а на входах всех остальных групп МФСП значения логических единиц. Входные сигналы xi(t) МФСП  представим в табл. 12.3, 12.4 и 12.5.

представим в табл. 12.3, 12.4 и 12.5.

Таблица 12.3

Устанавливающие xi(t) входные сигналы МФСП

| Входные сигналы xi | Значение входных узлов zj | Значение выходных узлов уj | Состояния Аj | |||||

| z1 | z2 | z3 | у1 | у2 | у3 | у4 | ||

| x1 | А1 | |||||||

| x2 | А2 | |||||||

| x3 | А3 | |||||||

| x4 | А4 |

При значении управляющего входа z0 = 0 трехуровневая память работает как трехразрядный параллельный регистр. Сигналы x1, x2, x3 устанавливают соответственно запоминаемые состояния А1, А2 и А3 (табл. 12.3), которые сохраняются при одном входном сигнале, когда на всех входных узлах zj (j = 1, 2, 3) значения равны логическому нулю (x1= x2= x3 =0). Состояние А4, однозначно установленное входным сигналом x4, не сохраняется ни при каких входных сигналах. Поэтому в детерминированном режиме работы входной сигнал x4 является запрещенным.

Таблица 12.4

Устанавливающие xi(t) входные сигналы МФСП

| Входные сигналы xi | Значение входных узлов zj | Значение выходных узлов уj | Состояния Аj | |||||

| z4 | z5 | z6 | у5 | у6 | у7 | у8 | ||

| x5 | А5 | |||||||

| x6 | А6 | |||||||

| x7 | А7 | |||||||

| x8 | А8 |

Сигналы x5, x6, x7 устанавливают соответственно запоминаемые состояния А5, А6, А7 (табл. 12.4), которые сохраняются при входном сигнале, когда z4 = z5 = z6 = 0. Состояние А8, установленное входным сигналом x8, не сохраняется при других входных сигналах. Поэтому в детерминированном режиме входной сигнал x8 является запрещенным.

Таблица 12.5

Устанавливающие xi(t) входные сигналы МФСП

| Входные сигналы xi | Значение входных узлов zj | Значение выходных узлов уj | Состояния Аj | ||||

| z7 | z8 | у1 | у2 | у3 | у4 | ||

| x9 | А9 | ||||||

| x10 | А10 | ||||||

| x11 | А11 |

Входные сигналы x9 и x10 устанавливают соответственно запоминаемые состояния А9 и А10 (табл. 12.5), сохраняемые при входном сигнале z7 = z8 = 0. Входной сигнал x11 является запрещенным, потому что установленное состояние А11 не сохраняется ни при каком входном сигнале МФСП  .

.

Таким образом, при z0 = 0 каждая МФСП Aj (j = 1, 2, 3) работает как элементарный автомат 2-го рода в параллельном трехр2азрядном регистре и их работа не зависит друг от друга. Общее число МN запоминаемых состояний данного регистра можно определить по формуле (6.2):

МN = 3 × 3 × 2 = 18.

При z0 = 1 трехуровневая память преобразуется в объединенный элементарный автомат А, в котором работа управляемых МФСП  в определенных блоках их состояний зависит от состояний автоматов стратегии

в определенных блоках их состояний зависит от состояний автоматов стратегии  и их выходных функций, реализованных на комбинационных схемах выходов I1 и I2.

и их выходных функций, реализованных на комбинационных схемах выходов I1 и I2.

Представим в табл. 12.3 блоки состояний МФСП  , сохраняемые при вполне определенных состояниях МФСП

, сохраняемые при вполне определенных состояниях МФСП  .

.

В табл. 12.4 блоки состояний МФСП  , сохраняемые при вполне определенных объединенных состояниях автомата стратегии

, сохраняемые при вполне определенных объединенных состояниях автомата стратегии  .

.

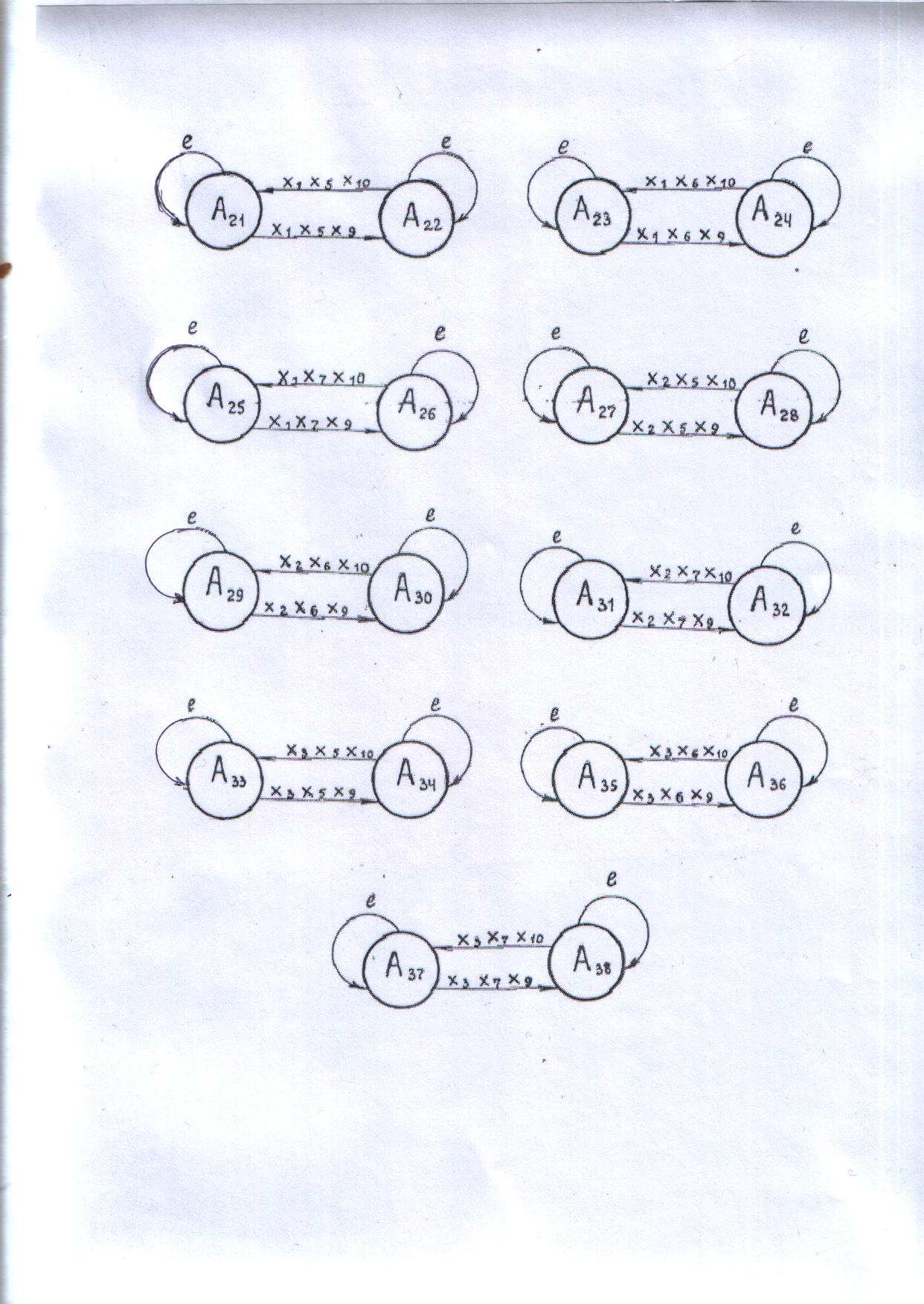

Объединенный трехуровневый элементарный автомат А способен функционировать как девять RS-триггеров (рис. 12.7). При функционировании по алгоритму RS-триггера МФСП  и

и  , реализующие автомат стратегии

, реализующие автомат стратегии  , не изменяют свои состояния. В этом случае состояния триггера могут изменяться только под воздействием входных сигналов х9 и х10, поступающих на входные узлы z7 и z8 управляемой МФСП

, не изменяют свои состояния. В этом случае состояния триггера могут изменяться только под воздействием входных сигналов х9 и х10, поступающих на входные узлы z7 и z8 управляемой МФСП  .

.

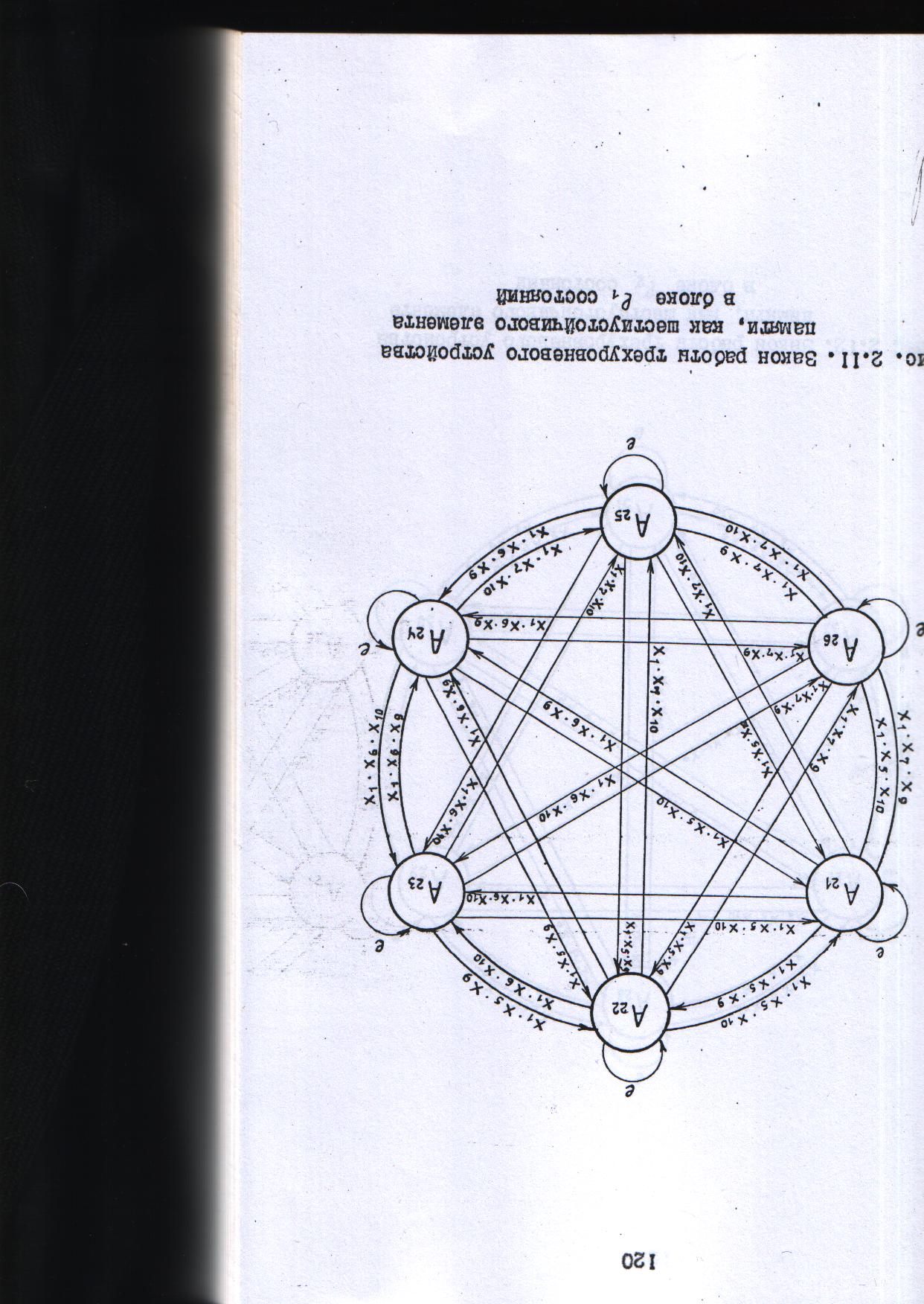

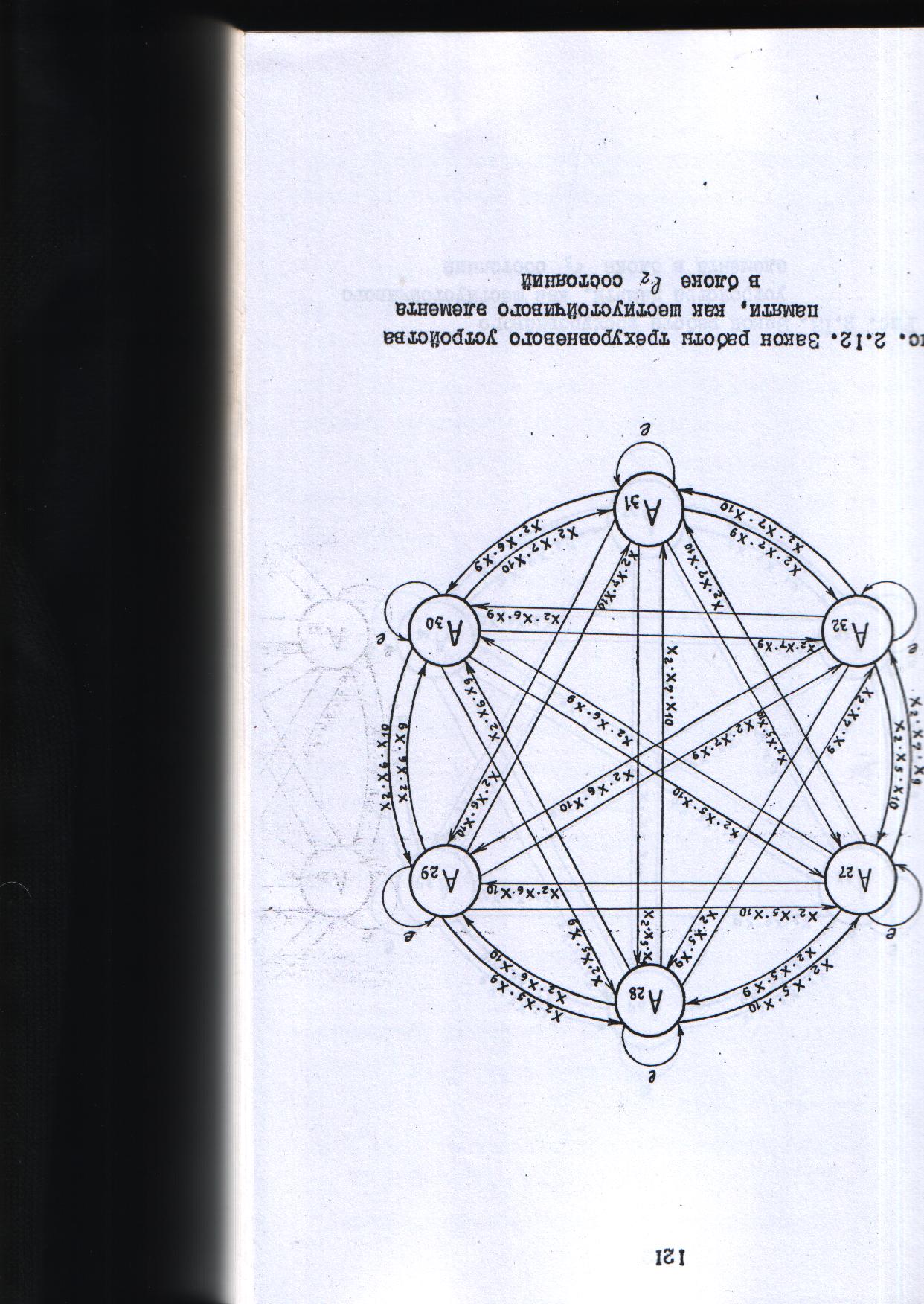

Состояния всех девяти триггеров способны сохраняться при одном входном сигнале е(Δ), когда на всех входных узлах zj (j = 1, 2, …, 8) значения равны логическому нулю. При неизменном состоянии автомата стратегии  объединенный трехуровневый автомат способен функционировать в детерминированном режиме как шести устойчивый элемент памяти в следующих блоках πj (j = 1,2,3) состояний: π1(А21 – А 26), π2(А27 – А 32), π3(А33 – А 38),

объединенный трехуровневый автомат способен функционировать в детерминированном режиме как шести устойчивый элемент памяти в следующих блоках πj (j = 1,2,3) состояний: π1(А21 – А 26), π2(А27 – А 32), π3(А33 – А 38),

Переходы из одного состояния в другое в каждом из блоков π1 (А21 – А26), π2 (А27 – А32), π3 (А33 – А38). Могут происходить только под действием входных сигналов хi(t), поступающих на входные узлы zj(j= 4 - 8) управляемых МФСП  и

и  (рис. 12.8 – 12.10).

(рис. 12.8 – 12.10).

Таблица 12.6

Сохраняемые объединенные состояния автомата

Состояние МФСП  | Выходные сигналы МФСП  | Выходные сигналы МФСП  | Объединенные состояния автомата  | ||||||

| у1 | у2 | у3 | у4 | у5 | у6 | у7 | у8 | ||

| А1 | А12 | ||||||||

| А13 | |||||||||

| А14 | |||||||||

| А2 | А15 | ||||||||

| А16 | |||||||||

| А17 | |||||||||

| А3 | А18 | ||||||||

| А19 | |||||||||

| А20 |

Таблица 12.7

Объединенные состояния трехуровневого автомата А

Объединен- ное состоя- ние автома- та  | Выходные сигналы МФСП  | Выходные сигналы МФСП  | Выходные сигналы МФСП  | Объединен- ное состоя- ние автома- та А | |||||||||

| у1 | у2 | у3 | у4 | у5 | у6 | у7 | у8 | У9 | У10 | У11 | У12 | ||

| А12 | А21 | ||||||||||||

| А22 | |||||||||||||

| А13 | А23 | ||||||||||||

| А24 | |||||||||||||

| А14 | А25 | ||||||||||||

| А26 | |||||||||||||

| А15 | А27 | ||||||||||||

| А28 | |||||||||||||

| А16 | А29 | ||||||||||||

| А30 | |||||||||||||

| А7 | А31 | ||||||||||||

| А32 | |||||||||||||

| А18 | А33 | ||||||||||||

| А34 | |||||||||||||

| А19 | А35 | ||||||||||||

| А36 | |||||||||||||

| А20 | А37 | ||||||||||||

| А38 |

Установка входным сигналом х1, х2 или х3 одно их трех состояний автомата  . Автомат А способен функционировать в определенных блоках πj (j = 1, 2, 3) состояний под воздействием сигналов х5, х6, х7, х9 и х10.

. Автомат А способен функционировать в определенных блоках πj (j = 1, 2, 3) состояний под воздействием сигналов х5, х6, х7, х9 и х10.

Под одновременном появлении соответствующих триад из входных сигналов х1, х2, х3, х5, х6, х7, х9 и х10 автомат способен функционировать как 18-значный элемент памяти во всем множестве своих состояний А21 – А38. Например, при появлении на входных узлах zj (j = 1, 2, …, 8) входных сигналов х1, х5 и х10 автомат переходит в состояние А21, а при появлении сигналов х3, х7 и х9 – в состояние А38 и т.д.

Таким образом, трехуровневое устройство памяти в этих детерминированных режимах функционирует как элементарный автомат 2-го рода и способен работать как девять RS-триггеров (рис. 12.7), как три шестеричных элемента (рис. 12.8-12.10) или как один 18-ричный элемент памяти, используя все свои 18 состояний.

Трехуровневое устройство памяти способно осуществлять укрупненные переходы в схемах управляемых МФСП  при изменениях состояний стратегии, под воздействием устанавливающих хМ (t) входных сигналов автоматов стратегии

при изменениях состояний стратегии, под воздействием устанавливающих хМ (t) входных сигналов автоматов стратегии  .

.

При изменении состояний в двухуровневом автомате стратегии  трех-уровневое устройство способно функционирует в двух своих блоках µi (i = 1,

трех-уровневое устройство способно функционирует в двух своих блоках µi (i = 1,

2) состояний: в блоке µ1, содержащем девять состояний А21, А23, А25, А25, А27, А29, А31, А33, А35, А37 и в блоке µ2, содержащем девять таких состояний А22, А24, А26, А28, А30, А32, А34, А36, А38.

При изменении состояний в автомате стратегии  трехуровневое устройство памяти способно функционировать в трех блоках µi (i = 1, 2, 3), соответственно содержащих по шесть состояний µ1{A21-A26}; µ2{A27-A32}; µ3{A33-A38}. Укрупненные переходы, зависимые от входных сигналов х(t) и е(Δ), представлены в табл. 12.8.

трехуровневое устройство памяти способно функционировать в трех блоках µi (i = 1, 2, 3), соответственно содержащих по шесть состояний µ1{A21-A26}; µ2{A27-A32}; µ3{A33-A38}. Укрупненные переходы, зависимые от входных сигналов х(t) и е(Δ), представлены в табл. 12.8.

| Рис. 12.6.Закон работы трехуровневого устройства памяти как девяти RS-триггеров |

| Рис.12.7. Закон работы трехуровневого устройства памяти, как шести устойчивого элемента в блоке е1 состояний |

Таким образом, во время укрупненных переходов в детерминированном режиме трехуровневое устройство памяти функционирует как элементарный автомат 3-го рода [3].

Переходы во всех детерминированных режимах трехуровневого автомата А происходят под воздействием элементарных однозначных слов p0(T), состоящих из входных сигналов xi(t), которые однозначно устанавливают запоминаемые состояния в МФСП  ,

,  и

и  , и одного входного сигнала е(Δ), то есть p0(T) = xi(t), е(Δ).

, и одного входного сигнала е(Δ), то есть p0(T) = xi(t), е(Δ).

| Рис.12.8. Закон работы трехуровневого устройства памяти, как шести устойчивого элемента в блоке е2 состояний |

Таблица 12.8