Основы проектирования на плис 3 страница

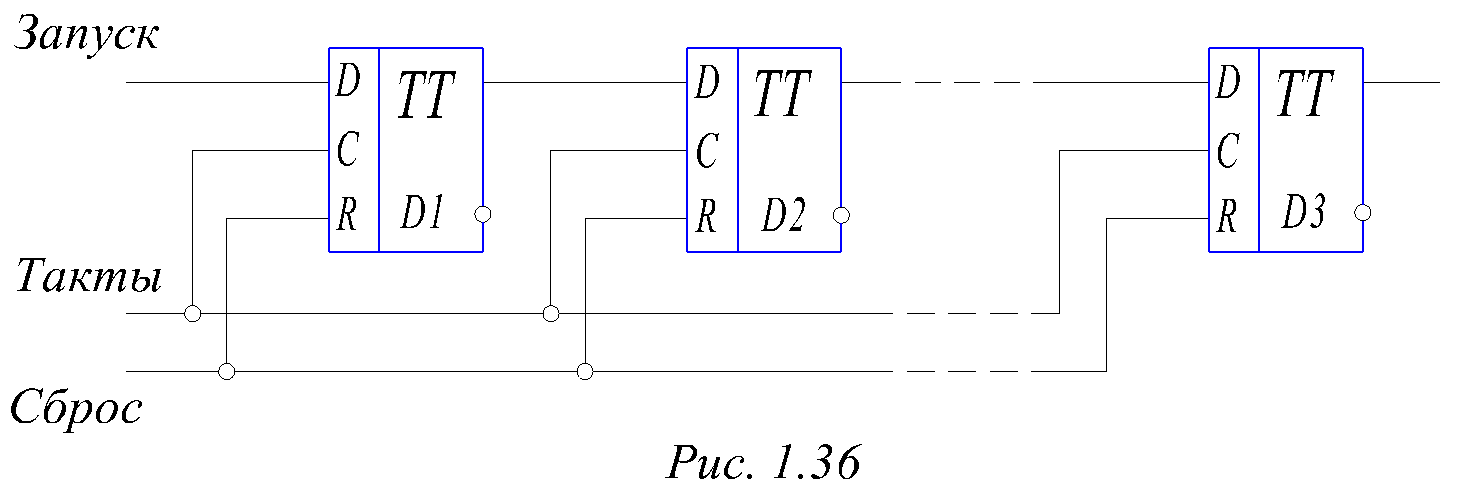

Более целесообразна тактируемая задержка. Она реализуется последовательно включенной цепочкой D – триггеров, как показано на рис. 1.36. Количество триггеров S определяет время задержки ТЗ = ST, где Т – период следования тактовых импульсов.

Рисунок 1.36. – Схема задержки на S тактов

Особенностью рассмотренной схемы является то, что длительность управляющих импульсов может быть произвольной; длительность выходных импульсов пропорциональна входным, но кратна Т. Кроме того, путем незначительного усложнения схемы время задержки можно регулировать. Для этого выходы триггеров подключаются через управляемый мультиплексор.

Регистры

Регистры в цифровой технике носят исключительный характер вследствие многообразия выполняемых ими функций. Они могут быть просто элементами памяти, могут выполнять функции преобразователей кода. Они используются как составная часть более сложных устройств, например, микропроцессоров, сложных систем управления, в том числе программируемых.

Обычно принято выделять последовательные и параллельные регистры. Они отличаются методами занесения, хранения и выдачи кодов. Возможны универсальные, последовательно – параллельные регистры.

Аппаратная реализация регистров может быть различной, включая из физическую природу. Мы основной упор сделаем на D – триггерах, поскольку они наиболее благоприятны для ПЛИС.

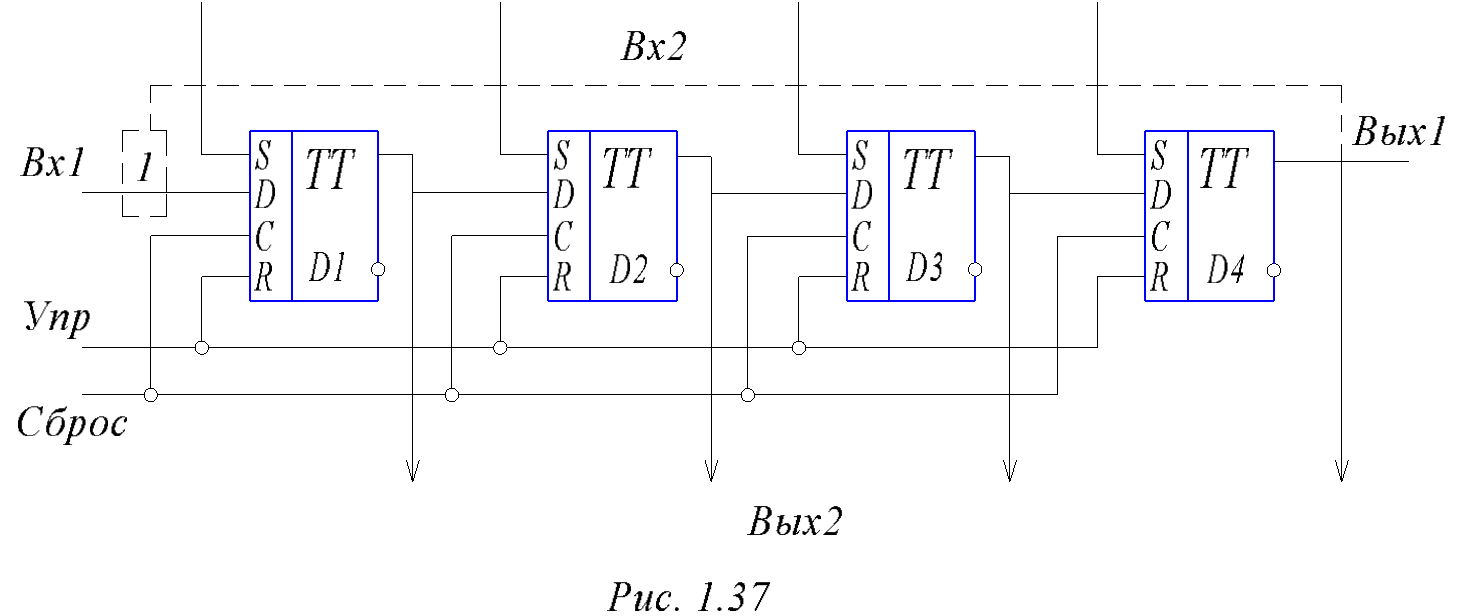

Универсальный последовательно – параллельный регистр на 4 разряда изображен на рис. 1.37. Регистр состоит из 4 D – триггеров D1 – D4. Вход первого триггера (Вх 1) может служить для ввода последовательного кода. Для этого одновременно с кодом на управляющий вход подаются 4 продвигающих импульса. Требование к ним: они должны подаваться с частотой импульсов последовательного кода, причем желательно, чтобы фронты продвигающих импульсов приходились на средины импульсов входного кода. Это позволит снизить зависимость от дрожания фронтов.

Перед началом работы регистра его нужно очистить, т.е. привести все триггеры в 0, для чего на все их входы R подается импульс «Сброс».

После занесения кода в регистр и прекращения подачи продвигающих импульсов информация в нем может храниться любое время. Ее можно убрать двумя способами: или обычным сбросом (тогда она стирается), или подачей на управляющий вход продвигающих импульсов. Тогда на выходе последовательного кода (Вых 1) появляется код для его приема другими устройствами. Если код в регистр занесен, а продвигающих импульсов нет, регистр по сути выполнил функцию преобразователя последовательного кода в параллельный.

Рисунок 1.37. – Универсальный регистр

Если Вх 1 не задействовать, а подавать параллельный код на входы безусловной установки S, то регистр просто сохранит эту информацию. При этом она может быть считана в любое время, т.е. асинхронно по вых 2 или считается в последовательном коде с Вых 2. При этом регистр очищается. Это и есть преобразование параллельного кода в последовательный.

Возможен и такой вариант включения. На входе устанавливается схема ИЛИ (показана штриховой линией). Если в регистр занести код по последовательному или параллельному входу, а потом подавать на управляющий вход тактовые импульсы, образуется динамический регистр, в котором этот код циркулирует до сброса.

При использовании ПЛИС легко можно увеличить емкость такого регистра до любого нужного числа разрядов.

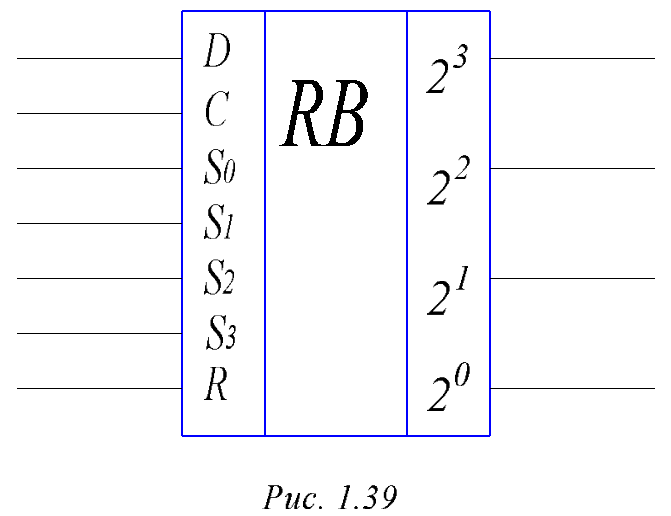

На электрических схемах регистры часто изображаются в виде, приведенном на рис. 1.39. В особых комментариях это изображение не нуждается.

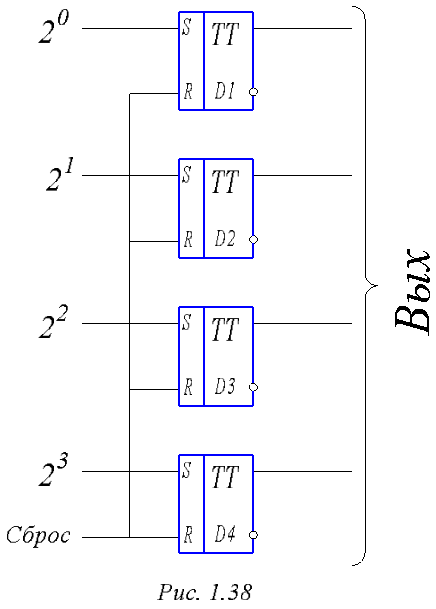

Рисунок 1.38. - Параллельный регистр

Рисунок 1. 39 - Изображение регистра

Счетчики

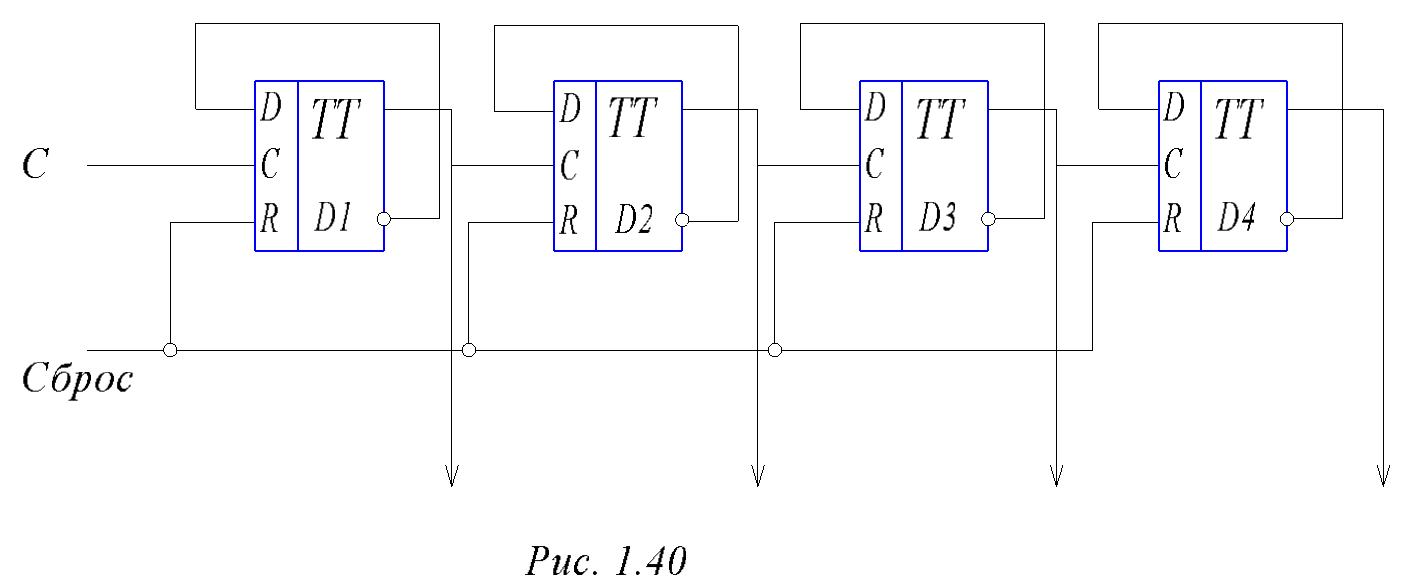

Среди множества различных типов счетчиков рассмотрим простейший – счетчик двоичного кода на D – триггерах. Схема четырехразрядного двоичного счетчика приведена на рис. 1.40. D –триггеры D1…. D4 работают в счетном режиме за счет обратных связей на D – входы. Триггеры включены последовательно, в результате чего каждый последующий триггер образует как бы старший разряд относительно предыдущего. Общая шина «Сброс» заводится на все R - входы триггеров. Счетчик легко можно синтезировать на любое число разрядов.

Рисунок 1.40. - Четырехразрядный двоичный счетчик

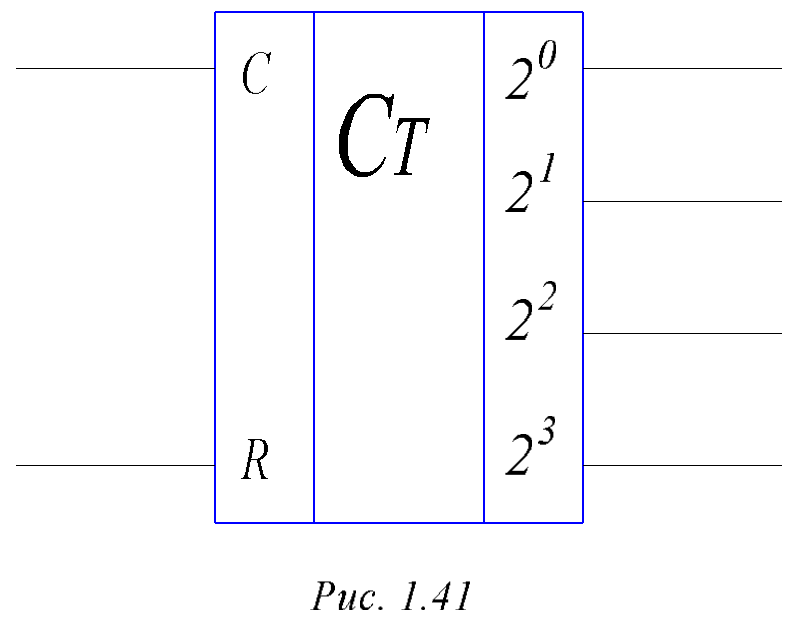

На рис. 1.41 показано изображение счетчика на принципиальных схемах.

Рисунок 1.41. – Изображение счетчика

Распределители импульсов

Это специализированные устройства с одним тактовым входом и несколькими выходами, причем в каждый момент времени единица присутствует только на одном из входов, а переключение выходов делается поочередно. Распределители (Р) предназначены для управления сложными системами путем разнесения очередности выполнения ими операций во времени.

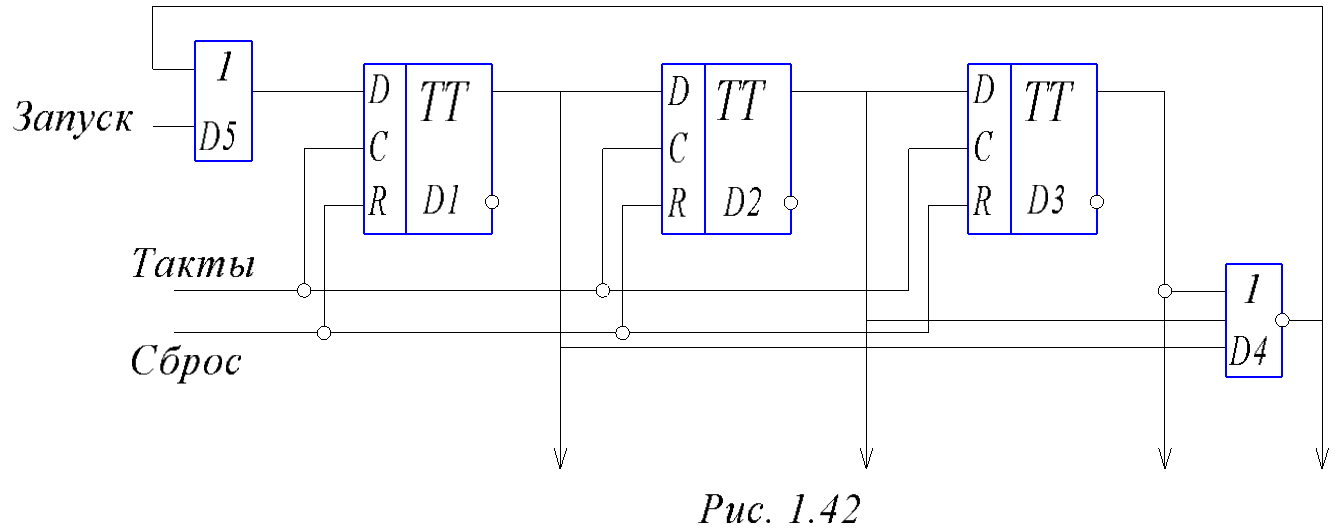

Возможны два варианта реализации распределителей: на D – триггерах и на счетчиках с дешифраторами. Первый вариант, на D – триггерах, приведен на рис. 1.42. Триггеры D1 – D3 образуют последовательную сдвиговую цепочку, а элементы D4 и D5 реализуют обратную связь для автоматического продолжения работы. При подаче импульса «Запуск» единица последовательно перемещается по цепочке триггеров. Когда единица проходит последний триггер, на выходе D4 появляется 1, повторно запускающая схему. Обязательное условие при этом – ограничение на длительность запускающих импульсов. Если она превышает период тактовой частоты. Выходные импульсы распределителя взаимно перекрываются.

Рисунок 1.42. - Распределитель импульсов на D - триггерах

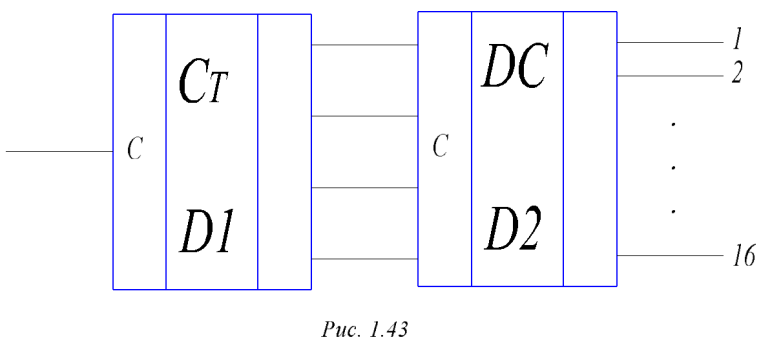

Второй вариант распределителя приведен на рис.1.43. При подаче тактовых импульсов на вход С счетчика коды на его выходах последовательно возрастают, в результате чего на выходах дешифратора последовательно появляются импульсы. Схема сложнее предыдущей, но работает более надежно.

Рисунок 1.43. - Распределитель, 2 вар.

Генераторы псевдослучайных последовательностей

Генераторы псевдослучайных последовательностей (далее ПСП) являются очень важной составляющей инженерной практики. Они используются в множестве практических приложений, в том числе при испытании новой техники, моделировании внешних воздействий, отказов элементов и т.д.

Генераторы ПСП объективно сравниваются по следующим характеристикам.

1. Период повторения ТП. Как правило, после некоторого цикла работы выходные коды генератора повторяются. Чем длиннее период, тем качественнее генератор. Если генератор вырабатывает кодовые последовательности размером в R разрядов, максимальный период повторения составляет 2R слов.

2. Равномерное распределение значений в выделенном диапазоне. Чаще всего это диапазон от 0 до 1; в противном случае его нормируют.

3. Соседние члены ПСП не должны быть связанными друг с другом. Это выражается в том, что корреляционная функция ПСП должна быть близкой к δ - функции, а ее спектральная плотность должна быть равномерной в достаточно большом диапазоне.

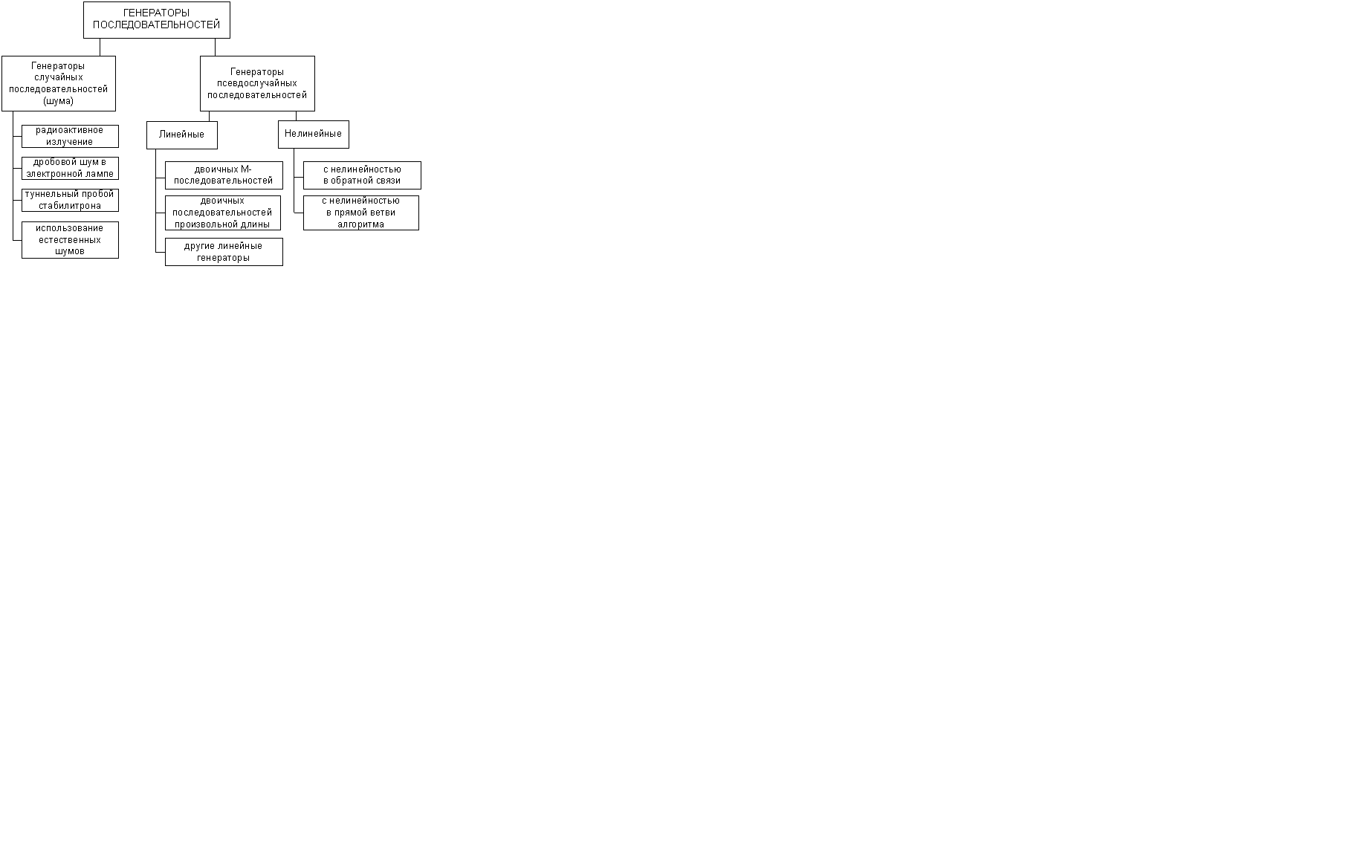

На рис. 1.44 приведен классификатор шумовых последовательностей

Рисунок 1.44. - Классификатор шумовых последовательностей

Как видно из классификатора, существует два типа генераторов. Первая группа, собственно генераторы шума, используют естественные источники и не применимы для ПЛИС. Остановимся более подробно на второй составляющей классификатора. Среди множества линейных генераторов ПСП наиболее применимы генераторы последней группы.

Исторически первые генераторы ПСП использовали деление двух чисел по рекурсивной процедуре, заключающейся в следующих шагах.

1. Выбираются два числа, А и В. Числа должны быть взаимно простыми, т.е. не иметь общих сомножителей. Производится деление А на В с получением частного С.

2. Выбирается часть частного и делится на В.

Далее процедура 2 повторяется до получения результата, совпадающего с первым частным. Очевидно, что следующие деления приведут к повторению последовательности.

Недостатком этого метода является трудность подбора делимого и делителя, так как от этого зависит период повторения. Кроме того, сама операция деления достаточно продолжительная, что ограничивает производительность генератора.

Модификация этого метода - целочисленное деление в кольце по модулю 2. При этом используется деление полубесконечного кода 1000000... на образующий полином []. Процедура и схемотехника деления будут показаны в разделе "корректирующие коды". В данном разделе отметим следующие особенности метода.

а) Сильная зависимость от выбора образующего полинома. Поиск неприводимых полиномов высоких степеней являлся ранее достаточно сложной задачей. Сейчас она разрешима в связи с заметно возросшей производительностью современных микропроцессорных и компьютерных систем.

б) Желательно производить поиск для полиномов нечетных степеней, так как при нечетных степенях количество неприводимых полиномов больше.

в) Следует учитывать один недостаток метода: если текущий остаток начинается с 0, следующий определится обычным сдвигом кода на разряд влево, т.е. неслучаен. То же наблюдается для двух и более 0 в начале остатка. Это влияет на корреляционную функцию потока случайных кодов.

Для автоматизации поиска неприводимых полиномов следует использовать следующие особенности неприводимых полиномов.

1. Код неприводимого полинома степени s начинается и оканчивается 1. Это сокращает время поиска, так как количество претендентов снижается вчетверо.

2. Неприводимый полином является нерегулярным и несимметричным. Например, коды типа 10000...1 или 10101...01 можно не рассматривать при поиске.

3. Если некоторый полином оказался неприводимым, то неприводим и полином с инверсией его разрядов. Простой пример: полином 1011 неприводим; тогда и полином 1101 также неприводим

Алгоритм поиска неприводимых полиномов выглядит достаточно просто. Из множества претендентов на неприводимость составляется список претендентов с учетом предыдущих ограничений. Выбирается первый элемент из списка, после чего проводится деление на него кода 10000000... с вычислением количества полученных остатков. Если оно составляет для полинома степени S значение 2S - 1, полином неприводим, как и его зеркальное отображение. После этого проверяется следующий претендент из списка. Отметим, что при возрастании S количество неприводимых полиномов возрастает в показательной зависимости, причем для четной и нечетной степеней показатели различны.

Предложенную методику вычисления неприводимых полиномов можно взять за основу построения генераторов ПСП более высоких степеней. Приведем некоторые, являющиеся оригинальными творениями авторов.

1. Пусть задано некоторое множество неприводимых полиномов степени S. Произведение двух и более таких полиномов может быть взято за основу генератора ПСП. Пусть полученный при этом полином степени 2S приводим, в качестве генератора ПСП он будет иметь более высокие характеристики, чем исходный.

2. Псевдослучайная последовательность существенно зависит от выбора начального значения. При этом возможен следующий вариант ее удлинения. При первоначальном задании кода начального значения генератор вырабатывает последовательность случайных чисел из R значений, после чего задается другой код. Его можно взять, например, изменив предыдущий на 1 или на другое оговоренной число. Можно использовать принцип автоключа, выбрав в качестве очередного начального значения последнюю кодовую комбинацию с выхода генератора. Еще один вариант - циклический сдвиг влево или вправо предыдущего начального значения.

3. Основной признак окончания ПСП - появление не его выходе кода 1000000.... Дальше коды ПСП повторяются. Поэтому в любом случае появление такого кода на выходе автоматически должно приводить к изменению режима работы генератора одним из описанных выше способов.

3 Лабораторный практикум на базе ПЛИС XC9572XL

3.1. Описание стенда

Микросхема XC9572XL была выбрана из-за ряда преимуществ, таких как:

1) ПЛИС с архитектурой CPLD;

2) самое большое количество циклов запись/стирание (не менее 10 тыс.);

3) доступность и относительная дешевизна;

4) большой срок хранения конфигурации;

5) поддержка JTAG;

6) простота программирования;

7) бесплатное программное обеспечение для разработок;

8) наличие большой библиотеки элементов.

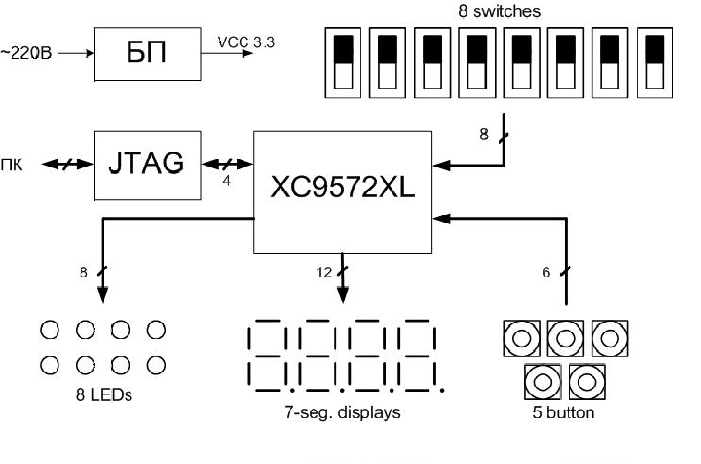

Микросхема XC9572XL – высокопроизводительная ПЛИС семейства XC9500XL, емкостью 1600 логических вентилей и минимальной задержкой распространения сигнала контакт – контакт (5 нс). Состоит из четырех 54V18 функциональных блоков. [7] На рис. 3.1 изображена структурная схема стенда.

Рисунок 3.1 – Структурная схема стенда

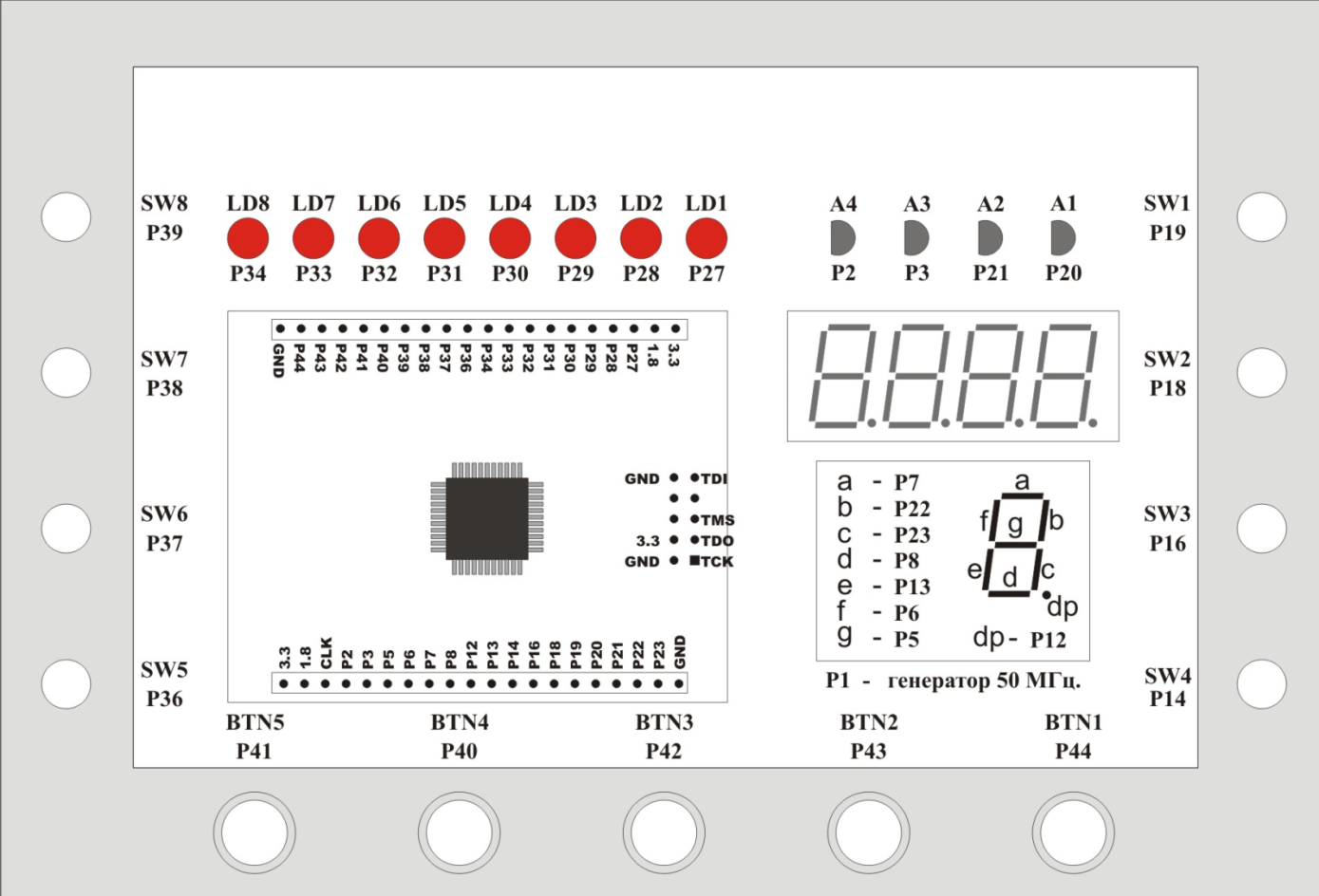

На рис.3.2 изображен внешний вид стенда

Рисунок 3.2 - Внешний вид стенда

Здесь (дальше описание всех элементов стенда)

3.2. Принципиальная схема платы ПЛИС

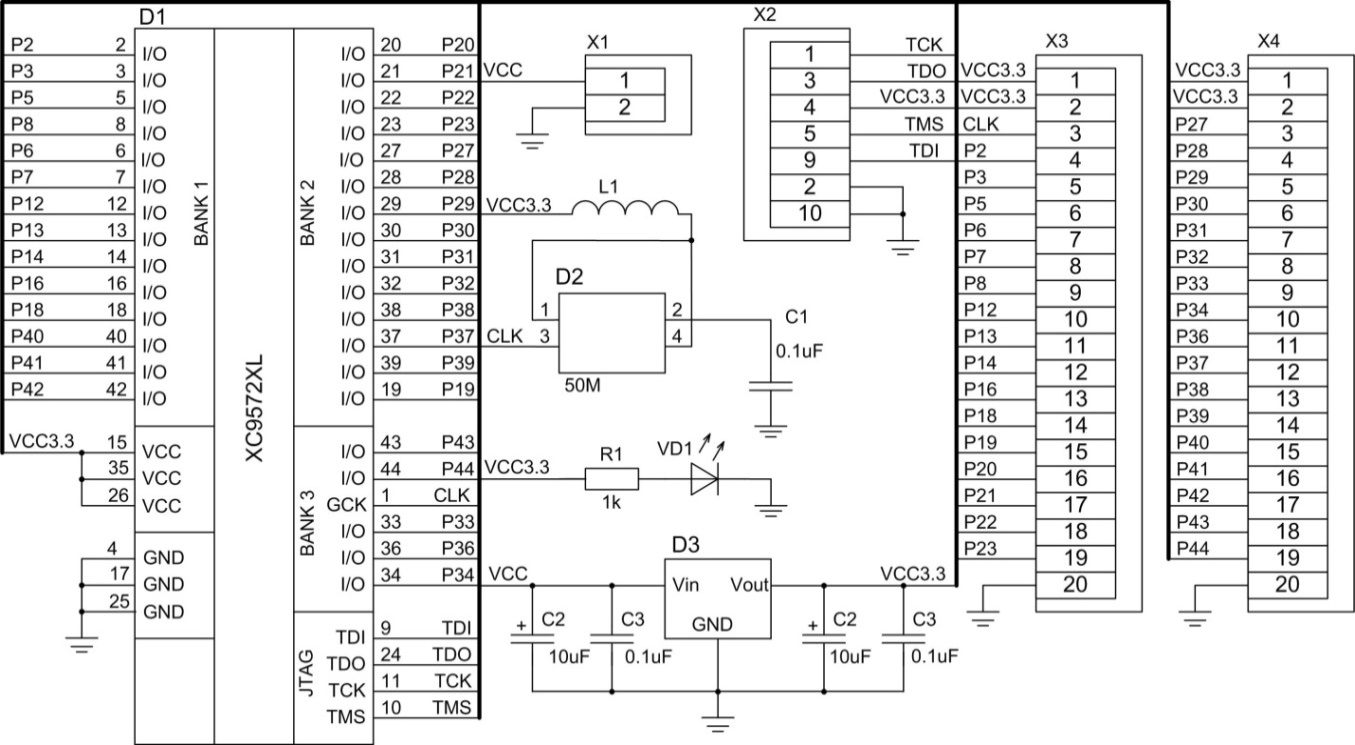

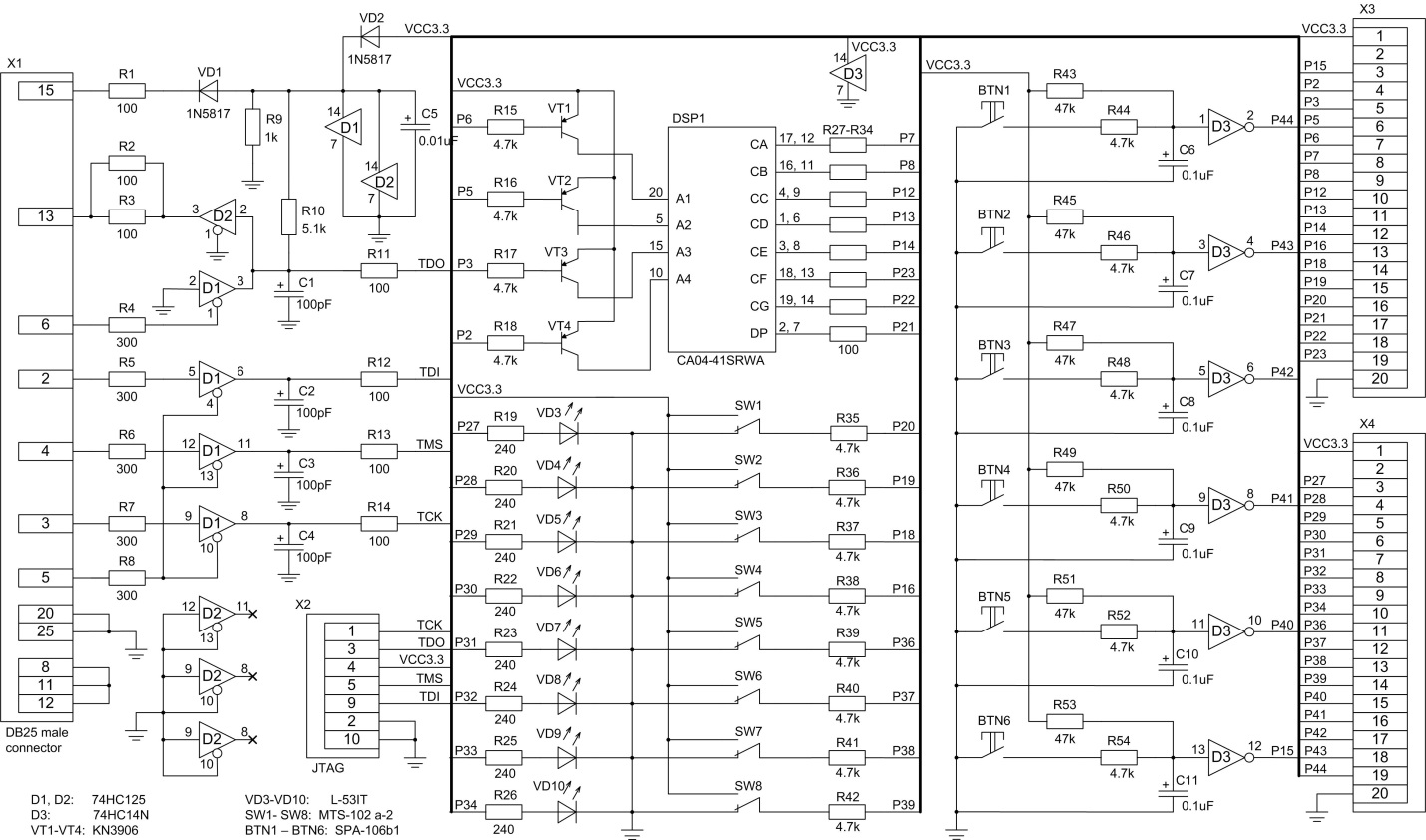

На рисунке 3.3 изображена принципиальная схема ПЛИС.

Рисунок 3.3 – Принципиальная схема ПЛИС

Плата ПЛИС состоит из:

-Микросхемы ПЛИС (D1);

- Кварцевого генератора на 50 МГц (D2, L1, C1);

- Светодиодного индикатора подачи напряжения на плату (VD1, R1);

- Преобразователя напряжения (C2,C3,C4,C5,D3);

- Пользовательских разъемов (Х1, Х2, Х3, Х4).

3.2. Принципиальная схема стенда

На рисунке 3.4 изображена принципиальная схема стенда

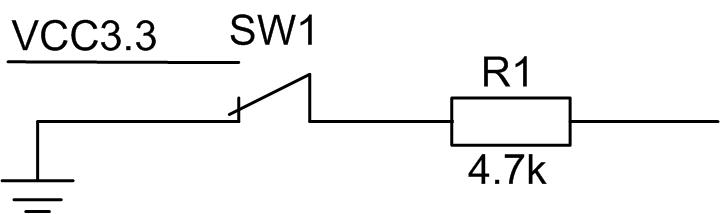

Рисунок 3.4. – Принципиальная схема стенда

Плата учебного стенда имеет в своем составе разъемы:

- X1 – для подключения к компьютеру;

- X2 – для подключения к плате ПЛИС (разъем программирования);

- X3, X4 – пользовательские разъемы.

Также на плате расположены:

- Программатор, состоящий из блока X1, резисторов R1 - R14, диодов VD1, VD2, конденсаторов C1 – C5, блока X2, D1,D2;

- Четырехсимвольный семисегментный индикатор (VT1, VT2,VT3, VT4);

- Блок светодиодов (VD3, VD4, VD5, VD6, VD7, VD8, VD9, VD10);

- Блок переключателей (SW1, SW2, SW3, SW4, SW5, SW6, SW7, SW8);

- Блок кнопок (BTN1, BTN2, BTN3, BTN4, BTN5, BTN6).

3.3. Составляющие элементы стенда

Светодиоды

Восемь отдельных светодиодов подключены к выходам ПЛИС (LD1- P27, LD2- P28, LD3- P29, LD4- P30, LD5- P31, LD6- P32, LD7- P33, LD8- P34.

На рис. 3.5 изображена схема подключения светодиодов.

Рисунок 3.5. – Схема подключения светодиодов

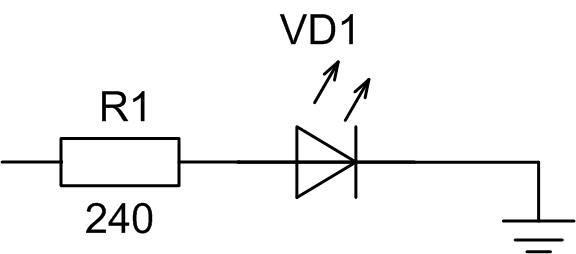

Кнопки

Пять кнопок подключены к выходам ПЛИС (BTN1- P44, BTN2- P43, BTN3- P42, BTN4- P40, BTN5- P41,). Кнопки присоединены к VCC3.3 через резистор 47кОм. Когда кнопка нажата, ее контакты подключаются к «земле» через резистор 4.7кОм. На делителе напряжения 47кОм - 4.7кОм (1/10 от VCC3.3) возникает сигнал логического нуля и держится все время пока кнопка нажата. Подавление дребезга обеспечивают RC - фильтр и триггер Шмитта D1. Эта схема создает высокий логический сигнал, когда кнопка нажата.

На рис. 3.6 изображена схема подключения кнопок.

Рисунок 3.6. – Схема подключения кнопок

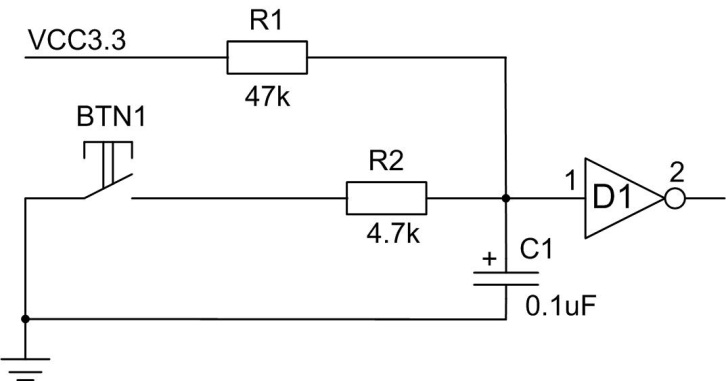

Переключатель

Восемь переключателей подключены к выходам ПЛИС (SW1- P19, SW2- P18, SW3- P16, SW4- P14, SW5- P36, SW6- P37, SW7- P38, SW8-P39). Переключатели используют 4.7 кОм резистор для токовой защиты входов ПЛИС.

На рис.3.7 изображена схема подключения переключателей.

Рисунок 3.7. – Схема подключения переключателей

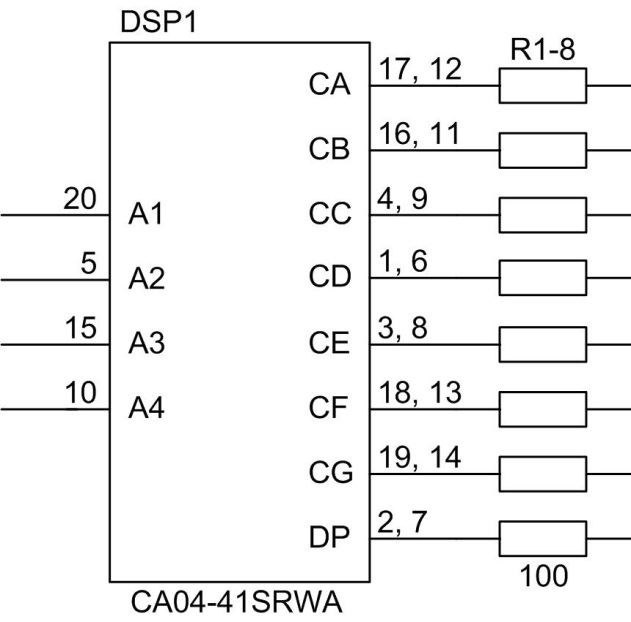

Светодиодный дисплей

Семисегментный светодиодный дисплей подключен к выходам ПЛИС (a- P13, b- P22, c- P23, d- P5, e- P12, f- P8, g- P6, dp-P7, A1- P20, A2- P21, A3- P3, A4- P2).

Катоды всех 32 сегментов (см. рис. 3.8) на дисплее собраны в 8 групп (СА, СВ, СС, CD, CE, CF, CG, DP). Аноды всех 32 сегментов на дисплее собраны в 4 группы.

.

Рисунок 3.8. – Схема подключения светодиодного дисплея

Схема создает мультиплексированный дисплей и организована по принципу динамической индикации.

Лабораторная работа №1

Изучение системы проектирования Xilinx ISE Design Suite 14.4.

1. Создание нового проекта.

1.1.Для запуска программы находим на рабочем столе ISE Design Suite 14.4.

На рис. 3.9 изображен ярлык программыISEDesignSuite 14.4.

Рисунок 3.9 -Ярлык программы ISE Design Suite 14.4.

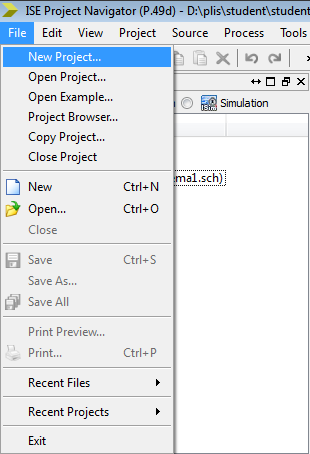

1.2.В верхнем левом углу панели управления программы (см. рис. 3.10) выберите: Project Setting Project.

.

Рисунок 3.10. - Панель NewProject

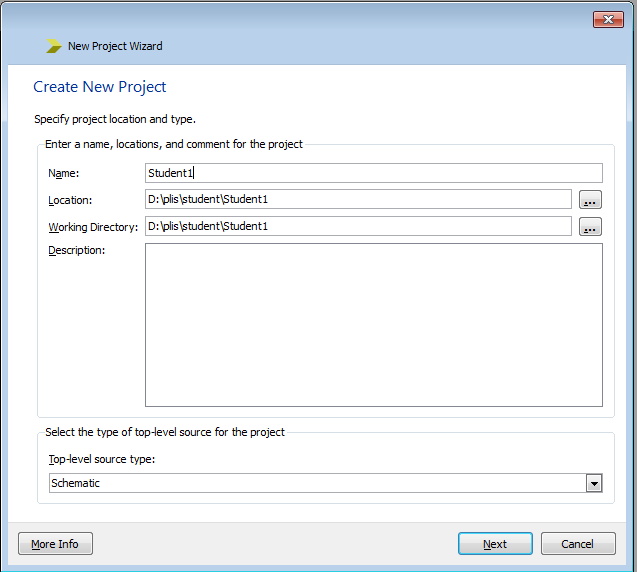

1.3. На экране появится окно для указания места \

На рис. 3.11 изображена панель Create New Project.

Рисунок 3.11 - Панель Create New Project

1.Введите имя проекта: Name

2. Укажите место расположения: Location

3.Выберите основной тип проекта:Schematic

4.Затем нажмите:Next

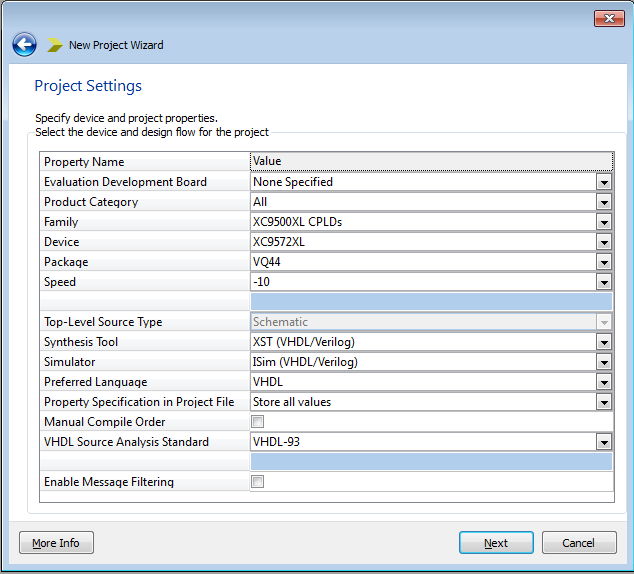

1.4.Окно настройки проекта: Project Setting

На рис. 3.12 изображено окно Project Setting

Рисунок 3.12 - Окно Project Setting

1.В строке (Family) выберите семейство ПЛИС:XC9500XLCPLDs.

2.В строке (Device) выберите ПЛИС Данного устройства:XC957XL.

3.Укажите (VQ44) комплектацию XC957XL (ПЛИС).

4.Выберите (Speed) скорость работы.

5. Выберите (PreferredLanguage) подходящий язык перевода вашей схемы.

6. Нажмите (Next).

2. Работа с проектом

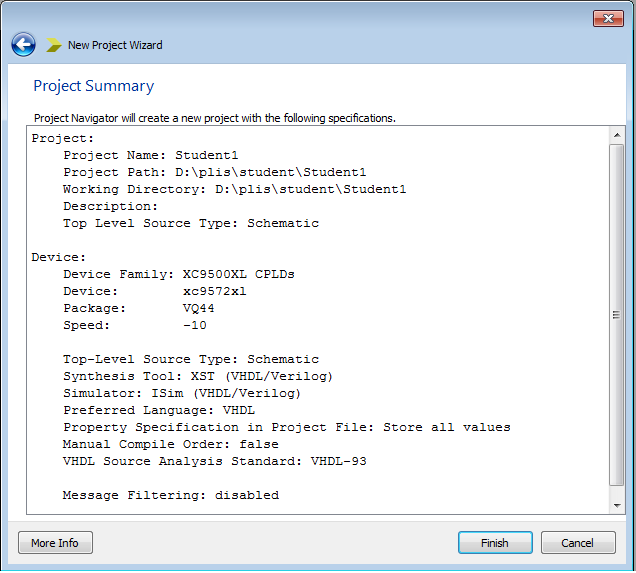

Описание созданного проекта: Project Summary

На рис. 3.13 изображена панель Project Summary

Рисунок 3.13. - Окно Project Summary

Для завершения создания проекта нажмите :Finish

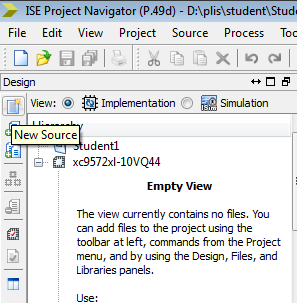

Выберите на панели управления :NewSource

На рис. 3.13 изображено окно New Source

Рисунок 3.13 - Окно New Source

На рис. 3.14 изображено окно Select Source Type

Рисунок 3.14 - Окно Select Source Type

В данном окне выберите основной тип создания проекта «Schematic» затем «File Name» после чего нажните «Next→Finish».

3. Работа со схемами.

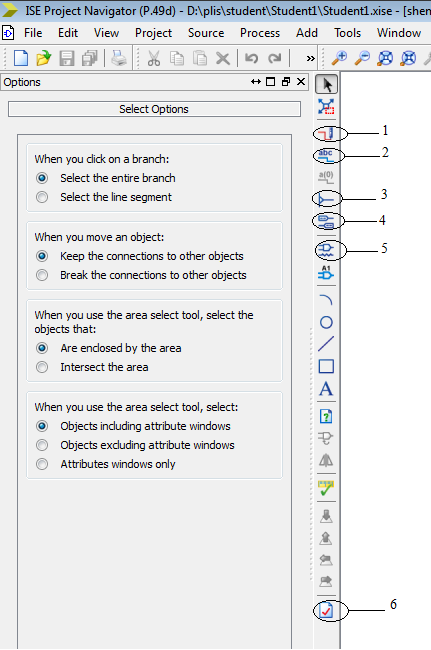

3.1 Панель управления

На рис.3.15 изображена панель управления

Рисунок 3.15 - Панель управления

Здесь обозначено:

1-Добавить проводник.

2-Изменение имени компонентов схемы.

3-Добавление шин.

4-Задание выходов(входов).

5-Выбор элементов. 6-Выбор размера рабочей области.

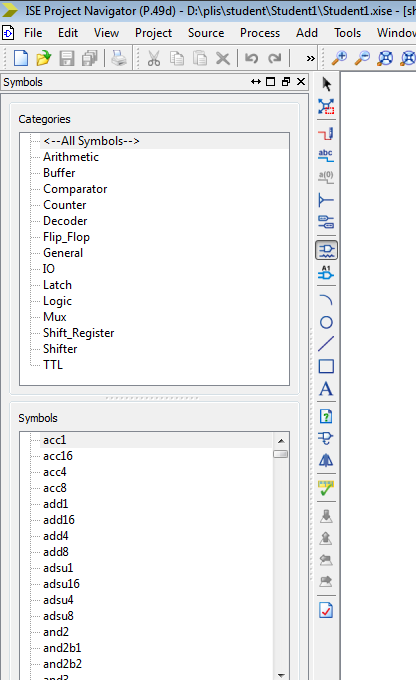

3.2 Выбор элементов

Для выбора элемента в панели инструментов нажмите на значок «Add Symbol». Элементы расположены по категориям. Выберите элемент и переместите курсор в рабочую область. Затем в нужном вам месте двойным нажатием левой кнопки мыши поставьте элемент

На рис.3.16 изображена панель выбора элементов.

Рисунок 3.16 - Панель выбора элементов

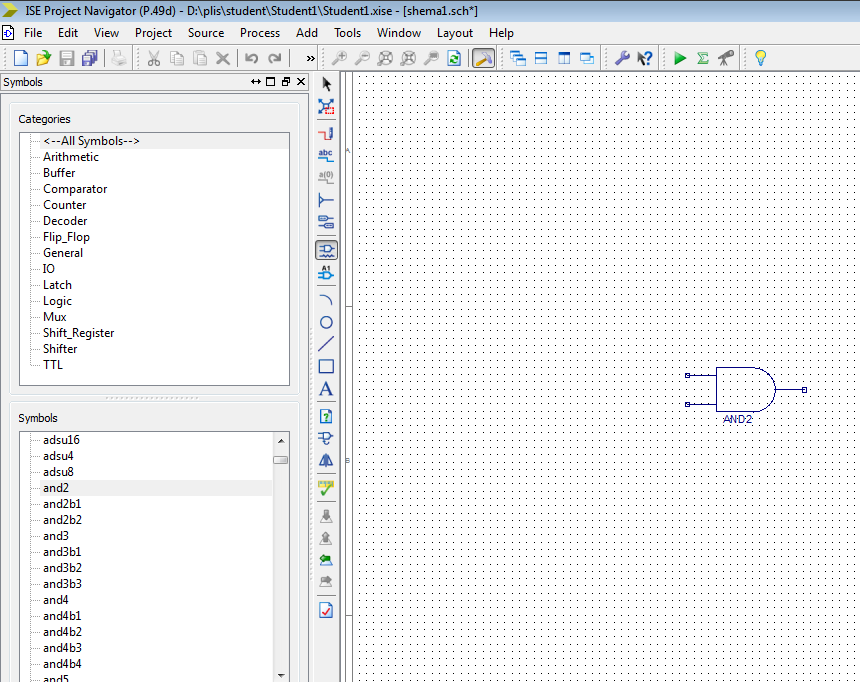

На рис. 3.17 приведен пример выбранного элемента and2.

Рисунок 3/17/ - Пример выбора элемента

Для того, чтобы соединить элементы в панели инструментов, нажмите «AddWire» затем соедините необходимые вам элементы.

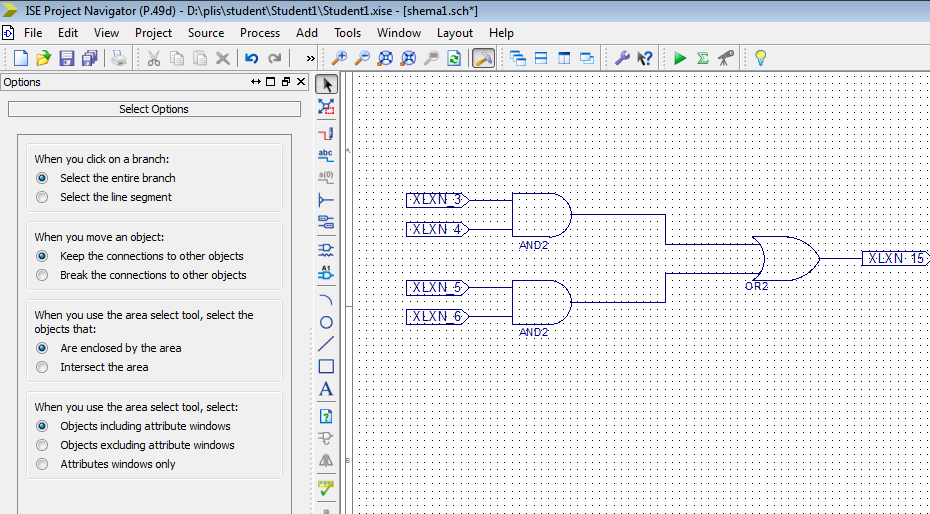

На рис. 3.18 изображен пример схемы.

Рисунок 3.18 - Пример схемы

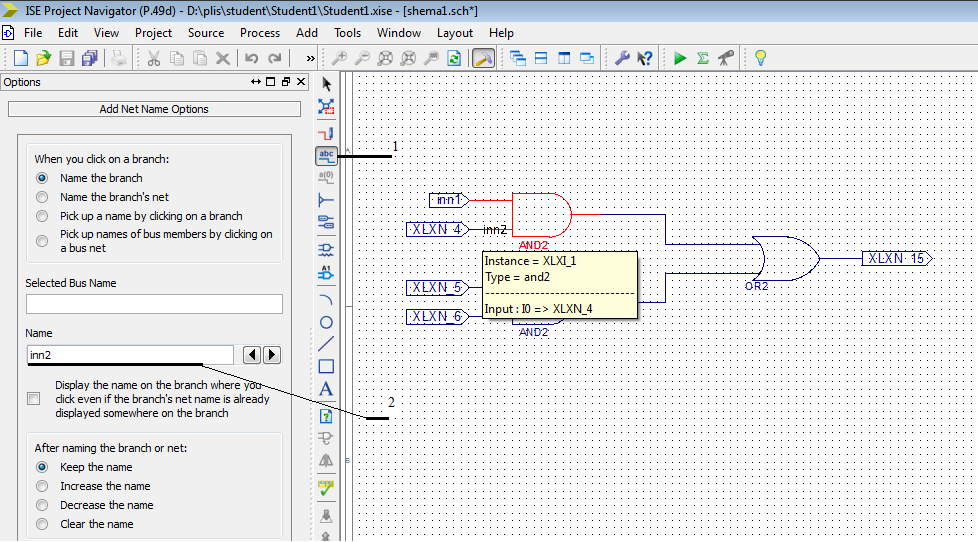

Затем, используя «AddI/OMarker», задайте для вашей схемы входы и выходы.

На рис.3.19 изображен пример использования AddI/OMarker

Рисунок 3.19. - Пример AddI/OMarker

1.Функция «AddName» используется для определения названий цепей и шин.

2. Строка определения имени.

Конфигурация входов (выходов).

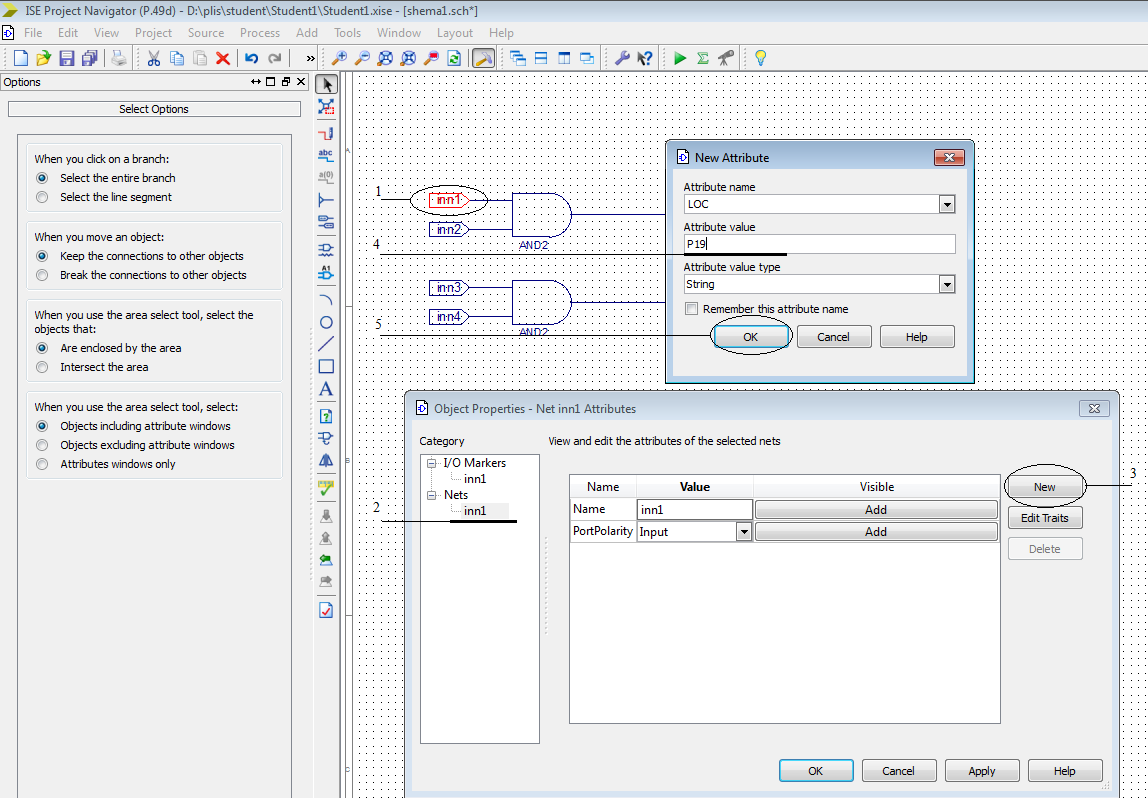

На рисунке 3.20 приведен пример конфигурации входов.

Для того, чтобы связать схему с устройством, необходимо соотнести ее входы (выходы) с входами (выходами) ПЛИС. Это делается следующим образом.

1. Выберите вход (выход) вашей схемы; двойным нажатием вызывается окно «Object Properties-Net Attributes».

2. В разделе «Nets» выбираем нужный вход (выход).

3. В правом верхнем углу окна нажимаем «New».

4. В строке «Attribute value» задаем нужный вход (выход). ( Название входов и выходов начинается с английской буквы «Р», что означает Pin (вывод), далее идет его номер).

5. Нажимаем «Ok».

Рисунок 3.20 - Конфигурация входов.

Перенос схемы на устройство

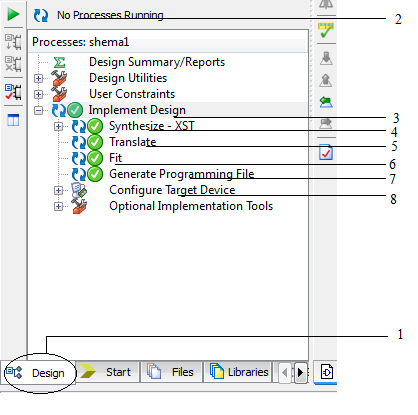

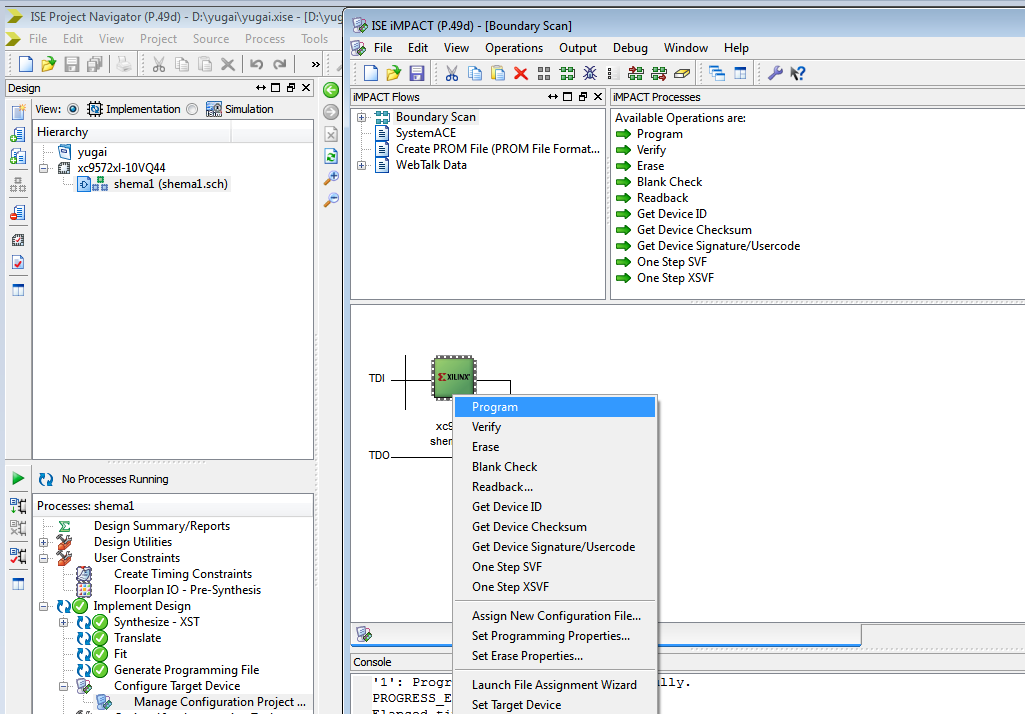

На рисунке 3.21 изображен перенос схемы на устройство. Для этого нужно выполнить следующие действия.

1. В левом нижнем углу программы нажимаем «Design»

2., 3. Двумя нажатиями левой кнопки мыши выберите «ImplementDesign» старт проверки схем.

4. «Synthesize-XSI» программа осуществляет синтез вашей схемы.

5. «Translate» эта операция переводит созданный проект (схему) на язык VHDL.

6. «Fit» определение ресурсов, занятых вашей схемой на ПЛИС(XC9572XL).

7. «GenerateProgramming» - генерация файла проекта.

8. Двойным щелчком запустите «Manage Configuration Project (IMPACKT)» - средство переноса программного кода ПЛИС.

Рисунок 3.21 - Перенос схемы на устройство

6. Перенос программного кода на ПЛИС.

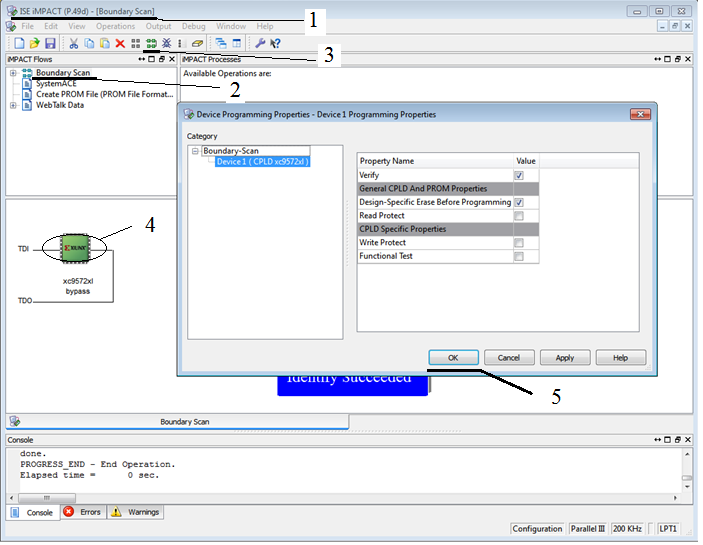

На рисунке 3.22 изображен перенос программного кода.

Рисунок 3.22 - Перенос программного кода

1. Программа переноса кода «ISEIMPACT».

2. Двойным щелчком выберите«Boundary Scan».

3. Выберете «InitializeChain» - инициализацию цепи.

4. Определение файла с вашим проектом.

5. Нажмите «Ok».

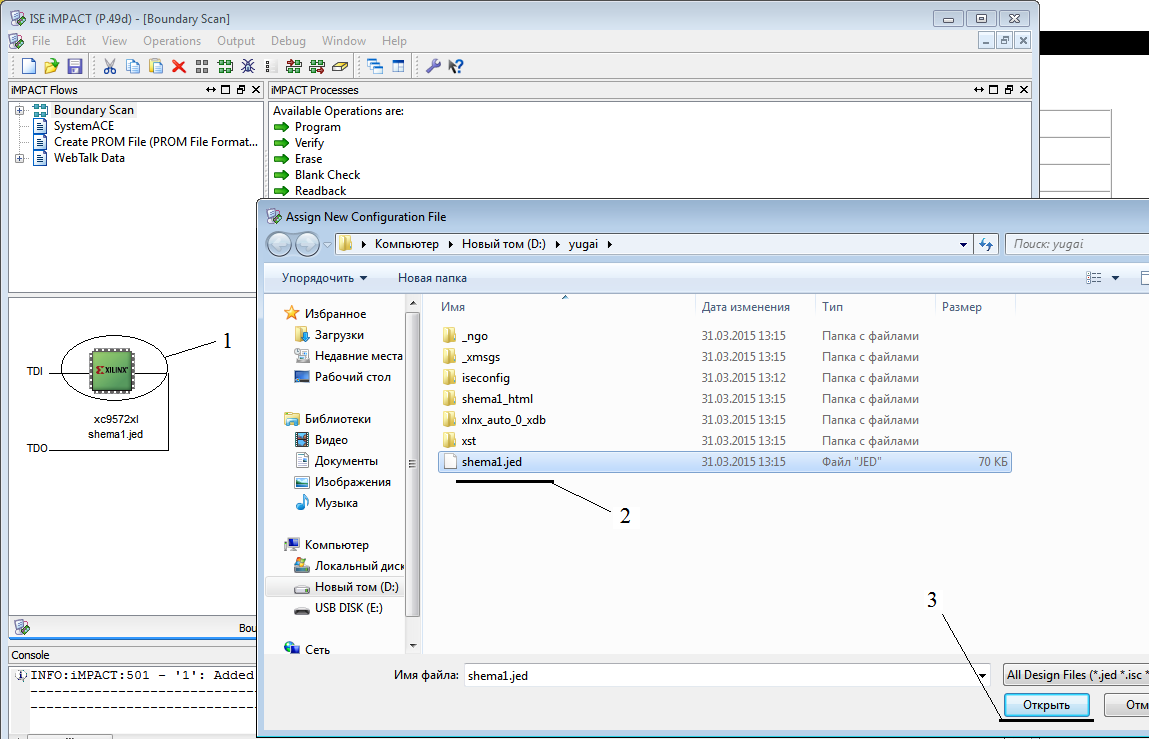

На рисунке 3. 23 изображено окно выбора схемы

Рисунок 3.23 - Выбор схемы

1. Двойным нажатием откройте «Assign New Configuration File».

2. Найдите свою схему.

3. Нажмите «Открыть».

На рисунке 3.24 изображено окно программирования.

Рисунок 3.24 - Программирование

Проделайте все пункты программирования для заданного вам варианта схемы.

Лабораторная работа №2

Элементы стандартной логики

Цель работы:ознакомление с элементами стандартной логики. ИзучитьэлементыAND2, AND3, AND3B1, NAND2, OR2, NOR2, NOR3, XOR2, XOR4, INV.

Общие указания

1. Элемент AND2. Назначение выводов: I0, I1-входы, О-выход. Выполняемая функция О=I0&I1. Таблица истинности элемента AND2 приведена в таблице 1.

Таблица 1- таблица истинности элемента AND2

| Входы | Выход | |

| I0 | I1 | O |

| X | ||

| X | ||

2. Элемент AND3.Назначение выводов: I0, I1, I2-входы, О-выход. Выполняемая функция О=I0&I1&I2.Таблица истинности элемента AND3приведена в таблице 2.

Таблица 2- таблица истинности элемента AND3

| Входы | Выход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||

3. Элемент AND3B1.Назначение выводов: I0, I1, I2-входы, О-выход. Выполняемая функция О=~I0&I1&I2. Таблица истинности элемента AND3B1 приведена в таблице 3.

Таблица 3-таблица истинности элемента AND3B1

| Входы | Выход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||

4. Элемент NAND2. Назначение выводов: I0, I1- входы, О- выход. Выполняемая функция О=~(I0&I1).таблица истинности элемента NAND2 приведена в таблице 4.

Таблица 4-таблица истинности элемента NAND2

| Входы | Выход | |

| I0 | I1 | O |

| X | ||

| X | ||

5. Элемент OR2. Назначение выводов: I0, I1-входы, О-выход. Выполняемая функция О=I0│I1. Таблица истинности элемента OR2 приведена в таблице 5.

Таблица 5- таблица истинности элемента OR2

| Входы | Выход | |

| I0 | I1 | O |

| X | ||

| X | ||

6. Элемент NOR2.Назначение выводов: I0, I1-входы, О-выход. Выполняемая функция О=~(I0│I1). Таблица истинности элемента NOR2 приведена в таблицу 6.

Таблица 6- таблица истинности элемента NOR2

| Входы | Выход | |

| I0 | I1 | O |

| X | ||

| X | ||

7. Элемент NOR3. Назначение выводов: I0, I1,I2-входы, О-выход. Выполняемая функция О=~(I0│I1│I2). Таблица истинностиэлемента NOR3 приведена в таблице 7.

Таблица 7- таблица истинностиэлемента NOR3

| Входы | Выход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||