Сравнительная оценка базовых логических элементов

Интегральные микросхемы семейства транзисторно-транзисторной логики ТТЛ характеризуются сравнительно высоким быстродействием при относительно большой потребляемой мощности, высокой помехоустойчивостью и большой нагрузочной способностью. Промышленность выпускает несколько разновидностей ТТЛ интегральных микросхем (ИМС), в том числе ИМС с диодами Шоттки (ТТЛШ) повышенного быстродействия (но большей мощности потребления) и маломощные (но с меньшим быстродействием) .

Микросхемы ЭСЛ-типа являются наиболее быстродействующими. Это обусловлено, в частности, тем, что транзисторы элемента работают в активном режиме, что исключает время выхода из насыщения; перезарядка нагружающих вывод емкостей происходит достаточно быстро через малое выходное сопротивление эмиттерных повторителей. Наряду с высоким быстродействием и большой нагрузочной способностью ЭСЛ-элемент отличается меньшей, чем ТТЛ-элемент, помехоустойчивостью (ввиду того, что для его переключения достаточен небольшой перепад входного напряжения), а также относительно большим потреблением энергии (за счет работы транзисторов в активном режиме и малых сопротивлений резисторов, дополнительно обеспечивающих быстродействие), что повышает требования к источникам питания и системе охлаждения.

Микросхемы КМОП-типа отличаются исключительно малым потреблением энергии, за счет чего температура кристалла не превышает допустимой при весьма большом количестве компонентов на нем. Это позволяет изготовлять большие интегральные схемы (БИС) КМОП-типа с наивысшей в настоящее время степенью интеграции. Малая потребляемая мощность позволяет использовать аппаратуру на КМОП ИМС при ограниченных возможностях источников питания. Вместе с этим КМОП ИМС отличают высокая помехозащищенность, а большое входное сопротивление КМОП-элемента, нагружающего данный, обеспечивает его высокую нагрузочную способность (большой коэффициент разветвления по выходу). Наряду с этим КМОП-элемент имеет ограниченный коэффициент объединения по входу. Это связано с тем, что число входов равно числу нагрузочных транзисторов; за счет значительного падения напряжения на большом количестве отпертых нагрузочных транзисторов напряжение U1,лог. 1 на выходе может существенно снизиться. По быстродействию микросхемы КМДП-типа принципиально уступают микросхемам ЭСЛ- и ТТЛ-типов.

В табл. 2.2.3 сведены усредненные параметры элементов рассмотренных типов. Конкретные параметры микросхем разных серий приведены в справочниках.

Таблица 2.2.3

| Параметр | Тип логики | |||

| ТТЛ | ТТЛШ | ЭСЛ | КМОП | |

| Напряжение Еп, В | -5,2 | 3...15 | ||

| Напряжение лог. 1 U1, В | 2,4 | 2,7 | -0,9 | =Еп |

| Напряжение лог.0 U°, В | 0,4 | 0,5 | -1,6 | = 0 |

| Быстродействие t3, нс | 2,9 | |||

| Помехоустойчивость Uпом, В | Не менее 0,4 | Не менее 0,5 | 0,2 | Не менее 0,3 Еп |

| Потребляемая мощность, Рпот, мВт | 0,1 | |||

| Коэффициент разветвления по выходу, Краз | ||||

| Коэффициент объединения по входу, Коб | 2...5 |

Заметим, что в ряде случаев цифровое устройство приходится выполнять на микросхемах разных типов (например, ТТЛ и ЭСЛ). При этом для согласования уровней лог. 1, а также лог. 0 применяют преобразователи уровней

Комбинационные устройства

Шифраторы и дешифраторы

Шифратор (кодер)

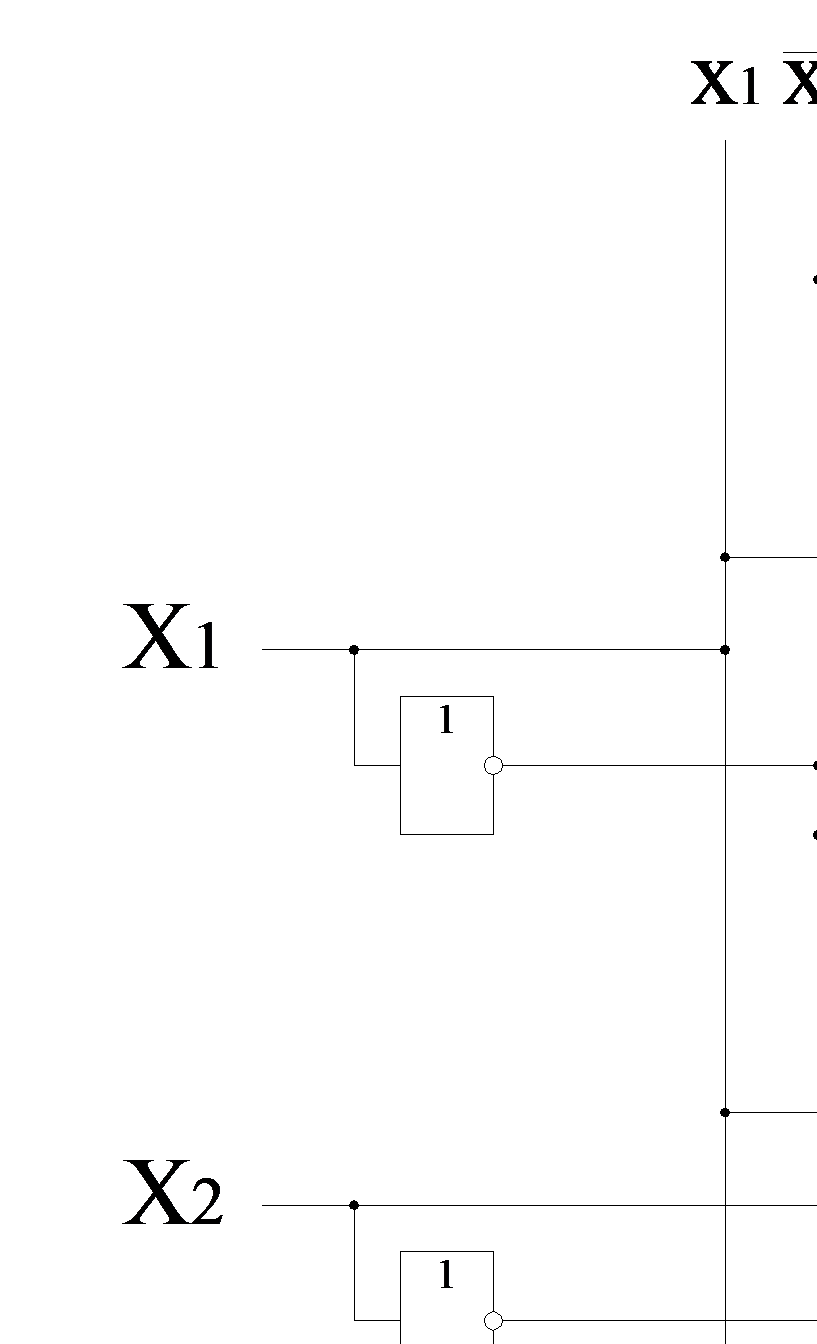

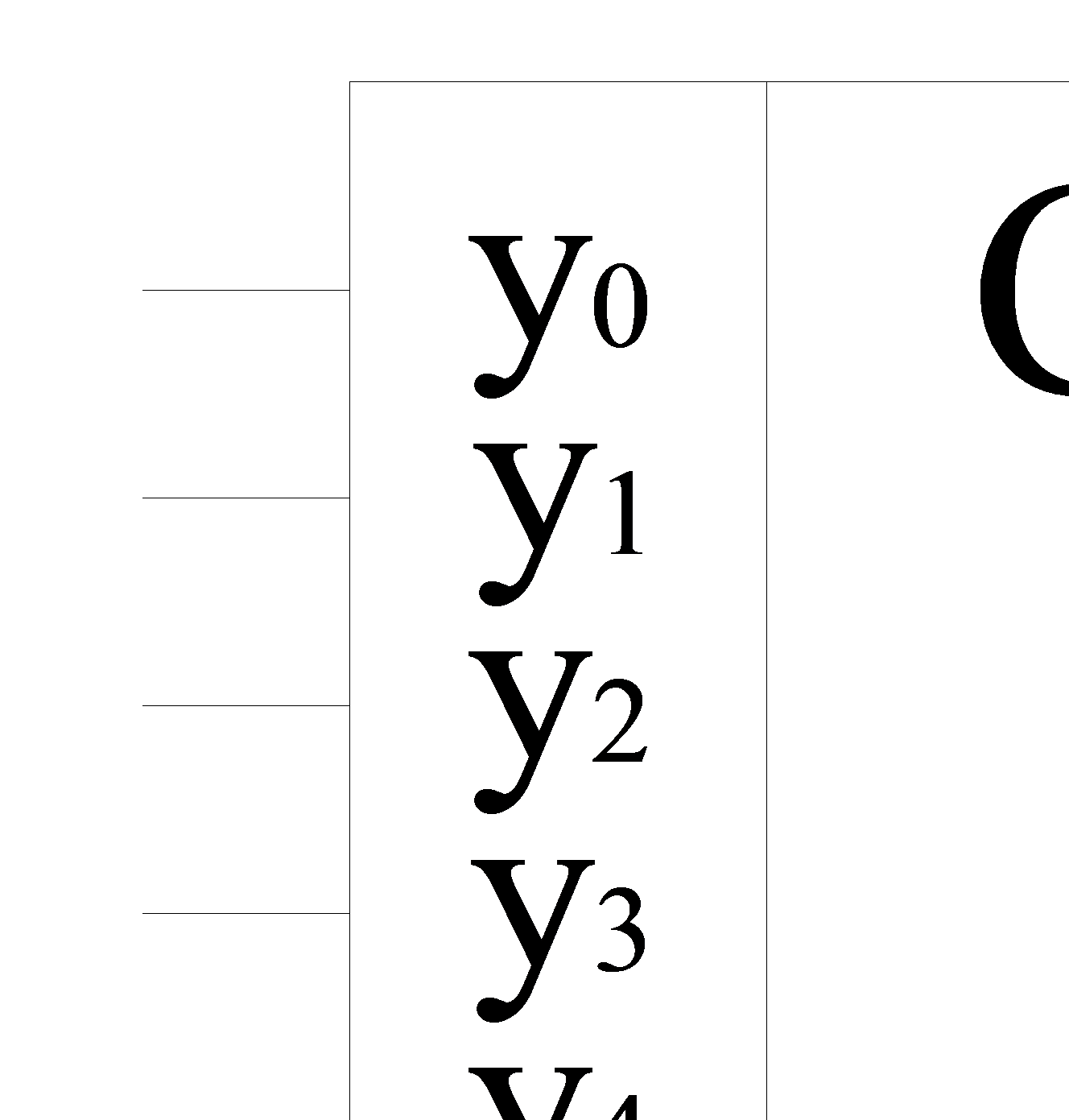

Шифратор служит для преобразования десятичного числа в двоичный код. Шифратор имеет входы У, пронумерованные в десятичной системе счисления и выходы Х, соответствующие отдельным разрядам двоичного числа. Чтобы преобразовать десятичное число в двоичное, необходимо активный логический уровень («0» или «1») подать на вход, номер которого в десятичной форме соответствует преобразуемому числу. При этом на выходах Х формируется соответствующий двоичный код.

|

|

Запишем логические выражения для выходов Х.

Х1=У1 v Y3 v Y5 v Y7 v Y9

Х2=У2 v Y3 v Y6 v Y7

Х4=У4 v Y5 v Y6 v Y7

Х8=У8 v Y9

В соответствии с полученными выражениями построим схему шифратора.

Дешифратор (декодер)

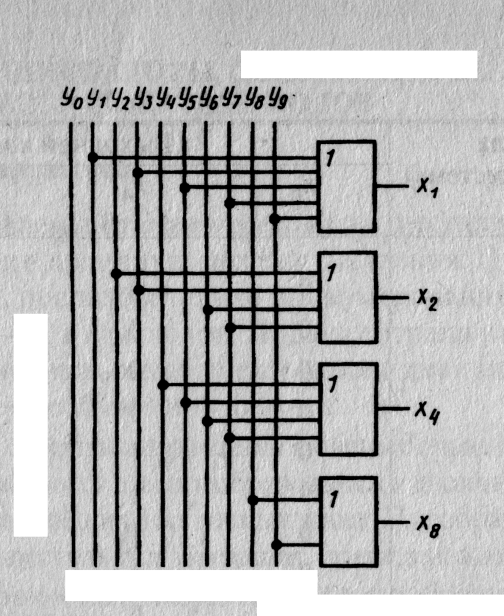

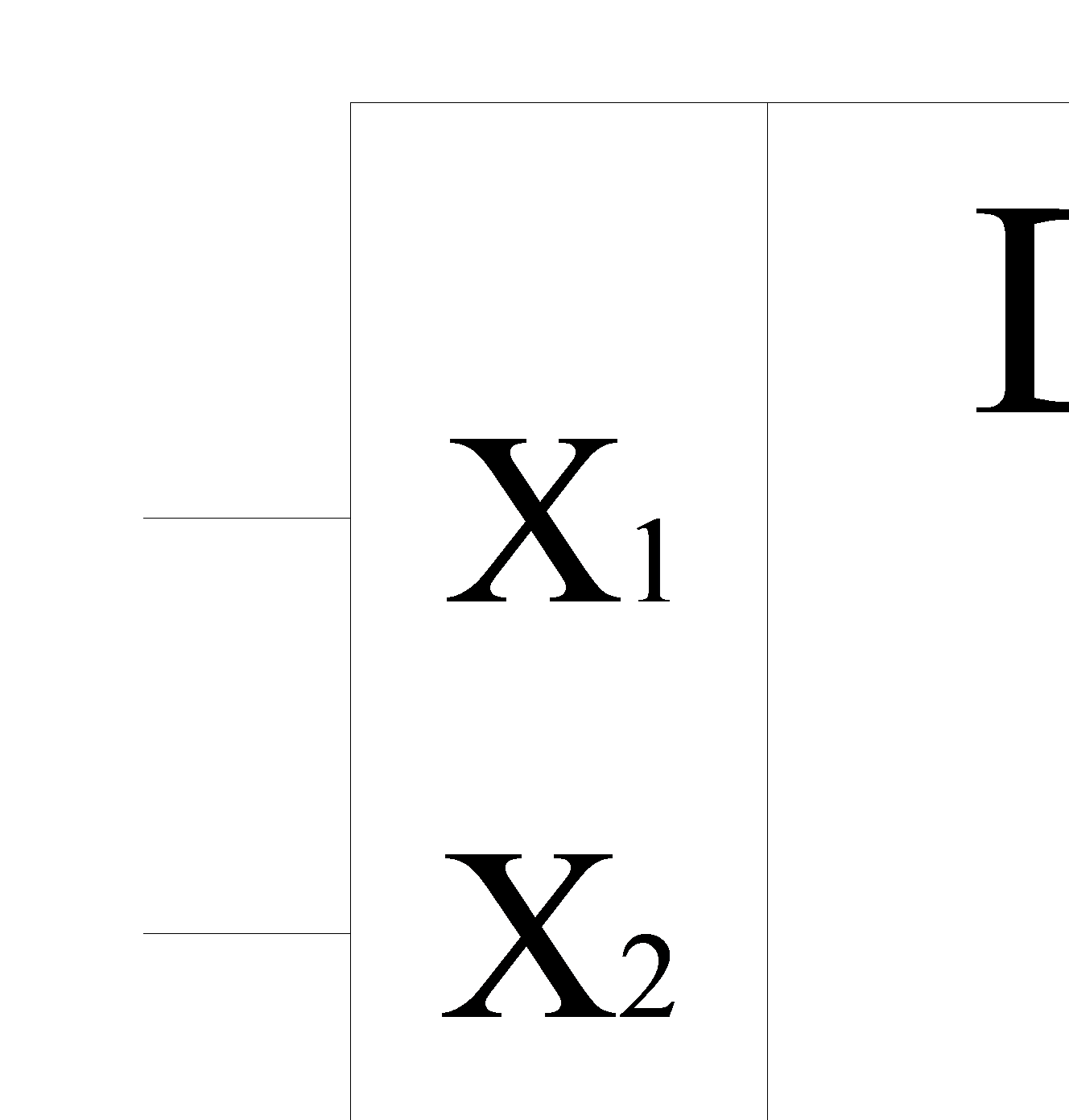

Выполняет обратную шифратору функцию, т.е. преобразует двоичный код в десятичное число. Дешифратор имеет входы Х, соответствующие отдельным разрядам двоичного числа и выходы У, пронумерованные в десятичной системе счисления. Чтобы двоичное число преобразовать в десятичное, необходимо разряды двоичного числа подать на соответствующе входы Х. При этом активный логический уровень («0» или «1») формируется на одном из выходов, номер которого в десятичной форме соответствует преобразуемому коду.

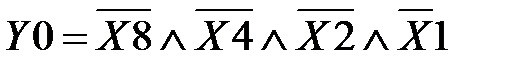

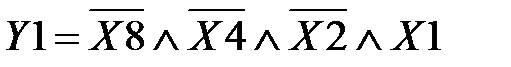

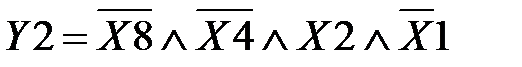

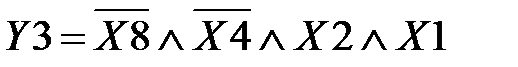

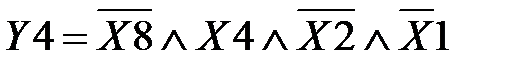

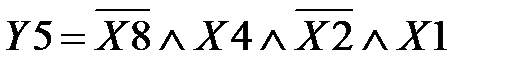

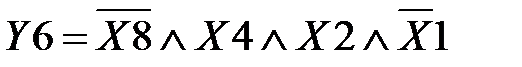

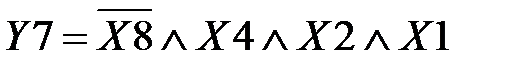

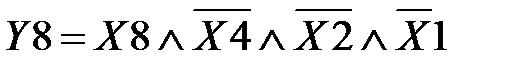

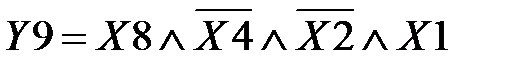

Логические выражения для выходов У

|           |

В соответствии с логическими выражениями построим схему дешифратора.