Процесс передачи сообщения 3 страница

Первыми принимаются и распознаются 48 бит адреса получателя. Приемник может распознавать индивидуальный физический адрес станции, групповой (multicast) адрес и широковещательный (broadcast) адрес. Пока контроллер не проведет сравнение адреса, полученного в пакете, со своим адресом, заданным в ячейках памяти параметров, никакие данные не записываются в буферы данных.

|

При приеме нового кадра вначале проверяется бит I/G (Individual/Group) в поле адреса приемника. Если это индивидуальный адрес (бит I/G = 0), то, проверяя физический адрес, контроллер сравнивает его с единственным адресом, указанным в 48-битной ячейке PADDR1 памяти параметров, если бит IAM = 0 в регистре PSMR. Если же бит IAM = 1, то специальная хэш-таблица индивидуальных адресов в ячейках IADDR1-IADDR4 используется для сравнения и распознавания группового адреса.

Если это групповой адрес (бит I/G = 1), то вначале контроллер проверяет, является ли адрес широковещательным. Широковещательный адрес представляет собой код, состоящий только из единицы. Если прием широковещательных адресов разрешен (бит BRO = О в регистре PSMR), то кадр принимается. Если же бит BRO = 1, то все кадры с широковещательными адресами отбрасываются, даже если установлен бит PRO = 1.

Если сравнение адреса прошло успешно, то начинается прием кадра, независимо от значения сигнала на контакте  (Reject). Если это групповой, но не широковещательный адрес, то производится сравнение адреса с использованием хэш-таблицы групповых адресов в ячейках GADDR1-GADDR4.

(Reject). Если это групповой, но не широковещательный адрес, то производится сравнение адреса с использованием хэш-таблицы групповых адресов в ячейках GADDR1-GADDR4.

Если проверка адреса прошла неудачно и в регистре режима PSMR установлен бит PRO = 0, т. е. проверка адреса должна была выполняться для всех кадров, то кадр отбрасывается. Если же бит PRO = 1, то кадры принимаются без проверки адреса, если сигнал на контакте  пассивный, и отбрасываются, если сигнал

пассивный, и отбрасываются, если сигнал  активный. При этом в слове состояния последнего буфера приема кадра устанавливается бит признака М (Miss). Если бит М = 1, то кадр был принят без контроля адреса, а если бит М = 0, то кадр был принят после проверки совпадения поля адреса получателя и адреса станции.

активный. При этом в слове состояния последнего буфера приема кадра устанавливается бит признака М (Miss). Если бит М = 1, то кадр был принят без контроля адреса, а если бит М = 0, то кадр был принят после проверки совпадения поля адреса получателя и адреса станции.

Если внешняя САМ-память используется при сравнении адресов, то следует установить режим без проверки совпадения адресов (promiscuous), установив бит PRO = 1, и тогда кадр может быть отброшен, если от САМ-памяти будет выставлен активный сигнал  во время приема кадра. Если САМ-память используется для хранения адресов, которые должны быть отброшены, а не приняты, то сигнал на контакте rrjct для САМ-памяти должен быть инвертирован.

во время приема кадра. Если САМ-память используется для хранения адресов, которые должны быть отброшены, а не приняты, то сигнал на контакте rrjct для САМ-памяти должен быть инвертирован.

Если сравнение адресов закончилось успешно, то контроллер проверяет бит незанятости Е в слове состояния следующего буфера в таблице RxBD, и если буфер свободен (бит Е = 1), то прием данных производится в этот буфер. Если при приеме кадра обнаружена коллизия, то текущий буфер может быть использован для приема нового кадра. Когда буфер заполнен, то контроллер сбрасывает бит Е := 0 и, если в слове состояния установлен бит прерывания 1 = 1, генерирует запрос на прерывание.

Если длина принимаемого кадра превышает размер буфера приема, то контроллер проверяет незанятость следующего буфера в таблице RxBD и, если буфер не занят, продолжает прием кадра в новый буфер. Максимальная длина приемного буфера задается пользователем в ячейке MRBLR протокол-независимой памяти параметров SCC-контрол-лера. При работе с Ethernet-протоколом рекомендуется в эту ячейку записывать значение не меньше 64 байт.

По окончании приема кадра, когда сигнал несущей станет пассивным, подсчитывается контрольная сумма принятого кадра и кадр сохраняется в буфере.

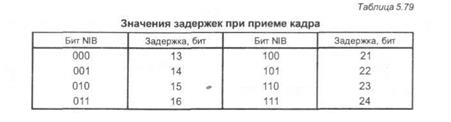

При приеме кадра Ethernet-контроллер постоянно проверяет длину кадра на максимальное и минимальное значение. Максимальная длина кадра данных (или число байт между начальным ограничителем и концом кадра) задается в ячейке MFLR памяти параметров и по стандарту 802,3 она равна 1518 байт. Если получен кадр, длина которого превышает значение MFLR, то излишек кадра отбрасывается, а 1518 байт кадра записываются в буфер. В слове состояния последнего буфера устанавливается бит LG := 1 (LonG). При этом длина кадра, записанная в ячейку длины последнего буферного дескриптора, является длиной реально принятого кадра. Специальный вычитающий счетчик в ячейке DMA_CNT контролирует, сколько байт кадра передано в буфер памяти. Минимальная длина кадра данных задается в ячейке MINFLR памяти параметров, и по стандарту 802,3 она равна 64 байтам. Если получен кадр, длина которого меньше значения MINFLR и бит RCH = 0 в регистре режима PSMR, то этот кадр отбрасывается и в слове состояния последнего буферного дескриптора текущего кадра устанавливается бит SH := 1 (SHort), если же бит RCH = 1, то кадр будет принят.

Пользователь может управлять процессом записи байтов кадра в буферы памяти по системной шине. Для этого предназначены ячейки MAXD1, MAXD2. Ячейка MAXD1 используется, если сравнение адресов прошло успешно, а ячейка MAXD2 - в режиме без проверки совпадения адресов (promiscuous mode). Пользователь имеет возможность остановить запись данных в память при передаче установленного в этих ячейках числа байт, и остаток кадра будет отброшен. Затем контроллер дождется окончания приема всего кадра, или пока не будет принято MFLR байт кадра, и заполнит в слове состояния буфера биты статуса принятого кадра и длину реально принятого кадра. Если такая остановка не требуется, то при инициализации в эти ячейки заносится значение 1518 байт. Эти ячейки могут быть использованы для контроля состояния сети, например, для приема только заголовков пакета, содержащих адресное поле, для проверки работающих в сети станций.

После завершения приема кадра, и если бит SIP в регистре PSMR установлен в «1», то байт информации (этот байт называется tag-байт) с контактов 23-16 параллельного порта В будет добавлен в последний буфер кадра. Если эти контакты настроены как выходы, то байт данных читается из регистра PBDAT. Если кадр данных отбрасывается, то и tag-байт тоже отбрасывается. Далее контроллер устанавливает в слове состояния буфера бит последнего буфера L := 1, заполняет биты состояния принятого кадра и сбрасывает бит незанятости Е := 0. Затем контроллер генерирует маскируемое прерывание, которое сообщает процессору, что кадр данных принят и находится в памяти, и переходит к ожиданию приема следующего кадра данных.

Для временного хранения принятой информации каждый Ethernet-контроллер имеет внутренние буферы FIFO. Данные из FIFO по SDMA-каналам под управлением RISC-контроллера начинают передаваться в соответствующие буферы памяти. Если RISC-контроллер не успевает очищать ячейки FIFO для приема новой информации из сети, и в момент прихода новой порции данных все ячейки FIFO окажутся занятыми, то возникает ошибка переполнения буферов overrun. При этом контроллер будет вынужден записать новые данные поверх старых, что приведет к потере информации. Далее текущий буфер закрывается, в его слове состояния устанавливается бит ошибки переполнения OV := 1 и через регистр событий генерируется, если оно разрешено, RXF-прерывание к центральному процессору и увеличивается счетчик потерянных кадров в ячейке DISFC памяти параметров. После вышеуказанных действий контроллер переходит в режим «охоты» и ожидает новый кадр данных.

Если при приеме правильного кадра данных нет свободных буферов в памяти для сохранения информации, то кадр будет потерян. Признаком этой ошибки является установка бита ошибки занятости BSY := 1 в регистре событий Ethernet-контроллера и увеличение счетчика потерянных кадров в ячейке DISFC памяти параметров.

Если Ethernet-контроллер принял кадр данных с длиной, не кратной 8 битам, то вначале он проверяет контрольную сумму кадра, и если будет обнаружена ошибка проверки CRC суммы, то регистрируется ошибка принятия невыравненного кадра, устанавливается бит ошибки NO := 1 в слове состояния BD и увеличивается счетчик принятых, некратных 8, кадров в ячейке ALEC памяти параметров. Если же ошибка проверки CRC не регистрируется, то продолжается обычный прием кадров.

Если при приеме кадра данных контроллер обнаруживает ошибку проверки CRC контрольной суммы, то текущий буфер закрывается, устанавливается бит ошибки CRC := 1 в его слове состояния, устанавливается бит RXF-прерывания в регистре событий и увеличивается счетчик CRC ошибок в ячейке CRCEC памяти параметров. После приема кадра с ошибкой проверки CRC суммы приемник переходит в режим поиска нового кадра.

Пользователь может также управлять процессом приема кадра при помощи команд ENTER HUNT MODE и INIT RX PARAMETERS. Команда CLOSE RxBD при работе с Ethernet-контроллером не применяется.

Проверка адресов с помощью САМ-памяти. САМ-память (контекстно-адресуемая или ассоциативная память) предназначена для сравнения адресов станции и адреса получателя в пакете. Ethernet-контроллер может подключаться к внешней контекстно-адресуемой САМ-памяти двумя способами: через последовательный интерфейс и/или через системную шину. Для включения того или иного режима пользователь должен просто разрешить работу с определенными внешними контактами и аппаратно подключить внешние схемы блока памяти. Если при работе пользователь отключит выбранные контакты контроллера, то текущий кадр может быть потерян.

При работе с внешней САМ-памятью можно также использовать внутреннюю логику выработки сигналов  блока системной интеграции.

блока системной интеграции.

При работе с последовательным интерфейсом после распознавания начального ог-

раничителя контроллер выставляет сигнал начала приема  = 0 (receive start). Этот

= 0 (receive start). Этот

сигнал выставляется только на один битовый интервал во время приема второго бита

адреса назначения.

Логические схемы САМ-памяти используют комбинацию сигналов  , RXD, RCLK для записи в память полей кадра и для генерации сигнала «записи» к микросхеме САМ-памяти для начала сравнения адреса. Сигнал RENA от микросхемы EEST может быть использован для прекращения сравнения адресов, если при приеме кадра обнаружено состояние коллизии.

, RXD, RCLK для записи в память полей кадра и для генерации сигнала «записи» к микросхеме САМ-памяти для начала сравнения адреса. Сигнал RENA от микросхемы EEST может быть использован для прекращения сравнения адресов, если при приеме кадра обнаружено состояние коллизии.

После окончания сравнения адреса кадра и, если текущий кадр должен быть отбро-шен, логика САМ-памяти вырабатывает активный сигнал «отмена приема»  = О (receive reject). Получив этот сигнал, контроллер прекращает прием кадра в системную память, и текущий буфер будет подготовлен для приема нового кадра данных. Поэтому сигнал

= О (receive reject). Получив этот сигнал, контроллер прекращает прием кадра в системную память, и текущий буфер будет подготовлен для приема нового кадра данных. Поэтому сигнал  должен быть выставлен до момента завершения приема кадра. Если сравнение адресов прошло успешно, то сигнал

должен быть выставлен до момента завершения приема кадра. Если сравнение адресов прошло успешно, то сигнал  не выставляется.

не выставляется.

Дополнительно логика САМ-памяти может выставлять дополнительную служебную информацию на линии РВ23-РВ16 параллельного порта В. Этот tag-байт выставляется на линии РВ23-РВ16 не раньше, чем закончится прием кадра без коллизий, и будет сброшен сигнал RENA. Если в регистре режима PSMR Ethernet-контроллера установлен бит SIP = 1, то этот дополнительный байт данных (tag-байт) контроллер сохранит в последнем буфере памяти принятого кадра данных. Tag-байт удерживается на линиях порта В, пока коммуникационный контроллер сигналом на линиях  -

-  не подтвердит , что tag-байт записан в память. Длина tag-байта не включается в общую длину принятого кадра, которую контроллер записывает в поле длины последнего буферного дескриптора RxBD.

не подтвердит , что tag-байт записан в память. Длина tag-байта не включается в общую длину принятого кадра, которую контроллер записывает в поле длины последнего буферного дескриптора RxBD.

В режиме параллельного интерфейса во время записи кадра данных в память, т. е. каждый цикл шины данных коммуникационный контроллер выставляет сигналы подтверждения SDMA-доступа  -

-  . Отметим, что эти сигналы не используются при работе контроллера канала с другими коммуникационными протоколами. САМ-логика использует эти сигналы для разрешения записи данных в САМ-память одновременно с записью их в системную память контроллера. Преимущество этого способа состоит в том, что запись в САМ-память данных производится по системной шине в параллельном виде.

. Отметим, что эти сигналы не используются при работе контроллера канала с другими коммуникационными протоколами. САМ-логика использует эти сигналы для разрешения записи данных в САМ-память одновременно с записью их в системную память контроллера. Преимущество этого способа состоит в том, что запись в САМ-память данных производится по системной шине в параллельном виде.

Сигналы  -

-  выставляются в течение всех циклов шины при записи кадра данных в буфер памяти. Одна комбинация сигналов

выставляются в течение всех циклов шины при записи кадра данных в буфер памяти. Одна комбинация сигналов  -

-  определяет,что

определяет,что

по шине передаются первые 32 бита кадра (

по шине передаются первые 32 бита кадра (  =1 ,

=1 ,  = 0)другая комбинация определяет, что передаются данные из середины кадра (

= 0)другая комбинация определяет, что передаются данные из середины кадра (  = 0,

= 0,  = 1), и третья комбинация определяет, что в память записываются последние 32 бита кадра (SDACK2 = 0, SDACK1 = 0), но только если к данным кадра добавлен tag-байт. Tag-байт должен быть включен в три байта последней 32-битной пересылки по шинам контроллера.

= 1), и третья комбинация определяет, что в память записываются последние 32 бита кадра (SDACK2 = 0, SDACK1 = 0), но только если к данным кадра добавлен tag-байт. Tag-байт должен быть включен в три байта последней 32-битной пересылки по шинам контроллера.

Если контроллер использует 32-битную шину данных, то 32 бита данных кадра записываются в память за один цикл шины. Если используется 16- или 8-битная шина, то для записи 32 бит данных требуется два или четыре цикла шины. В этом случае сигналы  -

-  выставляются в течение всех циклов шины, которые требуются для передачи всех 32 бит данных.

выставляются в течение всех циклов шины, которые требуются для передачи всех 32 бит данных.

Алгоритм проверки адреса при работе с таблицей адресов. Специальная команда SET GROUP ADDRESS используется для установки в «1» одного из 64 бит четырех индивидуальных/групповых регистров фильтров GADDR1-GADDR4 или IADDR1-IADDR4. Для того чтобы индивидуальный или групповой адрес был занесен в хэш-таблицу, пользователь перед передачей контроллеру этой команды должен записать требуемый адрес в ячейку TADDR (TADDR_H, TADDR_M, TADDR_L) памяти параметров. При выполнении команды SET GROUP ADDRESS RISC-контроллер проверяет в ячейке TADDR значение бита I/G и определяет, в какую хэш-таблицу - индивидуальную или групповую - будет занесен адрес. Далее 48-битный адрес преобразуется в один из 64 бит. Для этого он пропускается через 32-разрядную контрольную сумму CRC32. В результате получается 6-битная контрольная сумма, двоичный код которой представляет число от 1 до 64. Два старших бита контрольной суммы определяют номер одного из четырех регистров xADDR1-xADDR4, а оставшиеся четыре бита - номер бита в регистре, который будет установлен в «1».

Если требуется удалить адрес из хэш-таблицы, то Ethernet-контроллер должен быть выключен и хэш-таблица должна быть очищена. Пользователь может записать код «все 0» в регистры IADDR1-IADDR4 и GADDR1-GADDR4 для сброса хэш-таблиц и всех адресов после системного сброса и при включении Ethernet-контроллера. После этого следует восстановить адреса, которые надо сохранить, так как на один бит в хэш-таблице может быть назначено несколько адресов.

При приеме кадра содержимое поле адреса приемника по этому же алгоритму пропускается через CRC32 контрольную сумму. И если бит с вычисленным номером в ячейке хеш-таблицы равен единице, то кадр данных принимается. Если же бит равен нулю, то кадр отбрасывается. Эффективность хэш-таблиц возрастает с увеличением числа используемых адресов.

Обработка коллизий. Если при передаче кадра контроллер регистрирует состояние коллизии, то он в течение 32 битовых интервалов продолжает передачу «1» битов (JAM pattern). Если коллизия обнаруживается во время передачи преамбулы, то контроллер завершает передачу преамбулы, а затем передает 32 «1».

Если коллизия обнаруживается в течение 64 битовых интервалов после начала передачи кадра, то передача кадра останавливается, передатчик ожидает случайное количество заданных временных интервалов и делает попытку повторного выхода в сеть. Этот интервал называется Slot time и равен 512-битовым интервалам или 52 мкс.

Если коллизия обнаруживается после передачи или 64 битовых интервалов (если бит LCW = 0 в регистре режима) или после 56 битовых интервалов (если бит LCW = 1), то повторная передача кадра не производится, буфер закрывается, устанавливается бит ошибки LC := 1 в слове состояния буферного дескриптора и генерируется запрос на прерывание ТХЕ через регистр событий. Этот случай носит название «поздняя коллизия» (Late Collision).

Если коллизия обнаружена при приеме кадра, то прием останавливается. Бит ошибки LC := 1 в слове состояния буфера устанавливается, только если длина принятой части кадра не менее значения параметра MINFLR, или если разрешен прием коротких кадров (бит RSH = 1 в регистре режима), или если зарегистрирована поздняя коллизия.

При работе в петлевом режиме для тестирования работы обнаружения коллизий приемника и передатчика пользователь может запрограммировать принудительную выработку состояния коллизии после передачи каждого кадра данных. Для включения этого режима необходимо установить бит FC := 1 в регистре режима Ethernet-контроллера. Если же бит FC = 0, то схемы контроллера работают в обычном режиме.

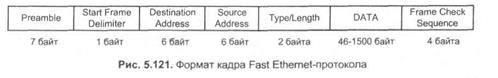

Fast Ethernet-контроллер. Fast Ethernet-контроллер является дальнейшим расширением Ethernet-контроллера и реализует сетевой протокол стандарта IEEE 802.3u. Так же как и просто Ethernet, контроллер Fast Ethernet поддерживает метод доступа «множественный доступ с прослушиванием несущей и обнаружением коллизий» CSMA/CD (Carrier-Sense Multiple Access/Collision Detect) и использует кадр данных стандартного формата. Ethernet Fast Ethernet-протокол реализуется через Mil-интерфейс (media-independent interface). Формат кадра протокола Fast Ethernet представлен на рис. 5.121.

Применение во всех версиях Ethernet-сетей одного типа кадра данных значительно облегчает совместную работу оборудования 10/100 Мбит/с и упрощает соединение раз-носкоростных Ethernet-сегментов. Кадр начинается со стандартной 7-байтовой преамбулы, которая представляет собой чередование «1» и «0», затем идет 1-байтовое поле начального ограничителя кадра (Start Frame Delimiter, SFD). При передаче преамбула и поле SFD автоматически вставляются, а при приеме автоматически удаляются самим контроллером.

Поля адреса получателя и отправителя занимают 48 бит. 10/100 МАС-подуровень (Media Access Control) реализует функции обработки адресов в принимаемых пакетах (широковещательного, одиночного, группового), обеспечивает полную поддержку интерфейса МИ, позволяя регистрировать прерывания после обработки полного кадра и каждого отдельного буфера кадра. Анализ поля адреса принимаемых кадров выполняется контроллером тремя способами. Способ Promiscuous - принимаются все кадры, независимо от их адреса, а для фильтрации адресов используется внешняя контекстная САМ-память. Способ Logical - прием кадров выполняется на основе анализа групповых и широковещательных адресов. Способ Physical - анализируется уникальный 48-битный адрес станции. Анализ совпадения адресов станции и в поле принятого кадра обычно производится с использованием механизма хэш-таблицы.

Двухбайтовое поле «Длина/Тип» для локальных сетей, без выхода на другие сети, обычно используется для указания типа кадра.

Поле данных должно быть кратно 8 битам, а его длина может составлять от 48 до 1500 байт. Время передачи самого короткого кадра данных (64 байта) называется slot time. При передаче происходит автоматическое дополнение поля данных служебными символами, если его длина меньше 48 байт.

Для контроля правильности передачи используется 4-байтовое поле контрольной суммы, которое строится по правилу 32-bit CCITT-CRC циклического полинома. Подавление контрольной суммы при передаче и контроль ее при приеме выполняются автоматически.

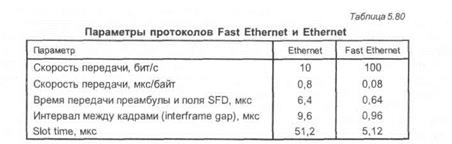

Отличия между Fast Ethernet и Ethernet-протоколами в основном заключаются в изменении временных параметров, которые произошли вследствие увеличения скорости передачи с 10 до 100 Мбит/с (табл. 5.80).

|

Контроллер МРС860Т. Контроллер МРС860Т является дальнейшим расширением семейства МРС860, в дополнение к возможностям контроллера МРС860МН в него добавлен 10/100 Ethernet-контроллер. Таким образом, МРС860Т состоит из трех основных блоков обработки: ядра PowerPC, которое предназначено для выполнения задач общего класса, встроенного в коммуникационный СРМ-модуль RISC-процессора, который выполняет реализацию стандартных коммуникационных протоколов (тех же, что и в МРС860МН), и 10/100 Fast Ethernet-контроллера, который предназначен для реализации 10/100 Мбит/с Ethernet-протокола. Поскольку блок Fast Ethernet реализован как отдельный модуль, имеет свои буферы FIFO и использует для передач данных по внутренней шине режим bursting DMA, то высокоскоростной обмен через сети Ethernet реализуется независимо от СРМ-модуля. Все другие функции СРМ-модуля сохранены в полном объеме. Так, МРС860Т-контроллер поддерживает протокол QMC с 64 временными каналами в режимах HDLC или Transparent.

В отличие от основных SCC-каналов FEC-контроллер не поддерживает набор команд управления от коммуникационного процессора и функционирует полностью автономно.

Контроллер может работать с полудуплексным 100 Мбит/с каналом или полнодуплексным каналом 10 Мбит/с в версиях с тактовыми частотами больше 25 МГц и полнодуплексным 100 Мбит/с каналом в версиях с тактовыми частотами больше 40 МГц. Fast Ethernet-контроллер (Fast Ethernet Controller, FEC) поддерживает три способа подключения к различным внешним трансиверам, выбор режима работы интерфейса производится битом MII_MODE в регистре R_CNTRL:

• 100 Мбит/с 802.3 Media-Independent Interface (Mil);

• 10 Мбит/с 802.3 МП;

• 10 Мбит/с 7-wire interface (7-проводной последовательный интерфейс для обычного 1 0 Мбит/с Ethernet).

|

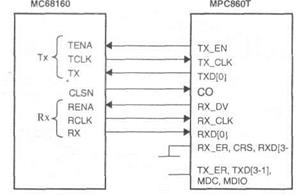

Пример подключения контроллера MPC860 показан на рис.5.122

Рис.5.122 Пример подключения контроллера МРС860 к 10 Мбит/с внешнему трансиверу.

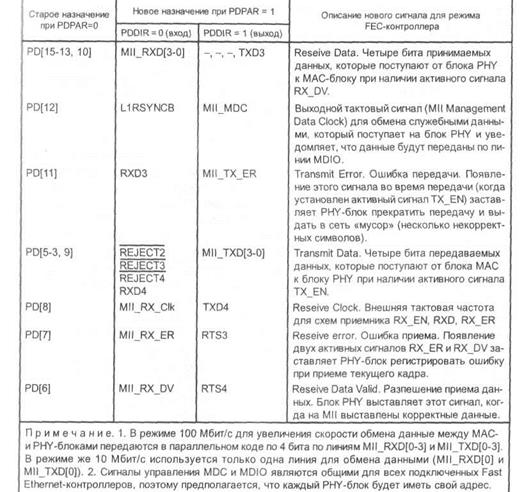

Если контроллер МРС860Т работает в режиме Fast Ethernet-протокола, то для реализации интерфейса Mil (Media Independent 1п1е1тасе)функциональное назначение некоторых внешних контактов будет изменено. Большинство сигналов Mil-интерфейса реализуется через контакты 13-разрядного параллельного порта D. Каждый разряд порта D может быть настроен или на работу как независимый разряд параллельного порта вво-ла/вывода (соответствующий бит в регистре PDPAR = 0), или как функциональный вывод < эммуникационного контроллера (соответствующий бит в регистре PDPAR = 1). Биты в регистре PDDIR определяют направление передачи через выбранную линию порта D РDDIR = 0-BXOfl, PDDIR = 1 -выход). Для включения режима МП-интерфейса требуется записать код 0x1 FFF в регистр PDPAR, код 0x1 С58 в регистр PDDIR.

Если контроллер МРС860Т работает в режиме Fast Ethernet-протокола, то для реализации интерфейса Mil (Media Independent 1п1е1тасе)функциональное назначение некоторых внешних контактов будет изменено. Большинство сигналов Mil-интерфейса реализуется через контакты 13-разрядного параллельного порта D. Каждый разряд порта D может быть настроен или на работу как независимый разряд параллельного порта вво-ла/вывода (соответствующий бит в регистре PDPAR = 0), или как функциональный вывод < эммуникационного контроллера (соответствующий бит в регистре PDPAR = 1). Биты в регистре PDDIR определяют направление передачи через выбранную линию порта D РDDIR = 0-BXOfl, PDDIR = 1 -выход). Для включения режима МП-интерфейса требуется записать код 0x1 FFF в регистр PDPAR, код 0x1 С58 в регистр PDDIR.

Подключение Fast Ethernet-контроллера к внешнему устройству PHY интерфейса производится с использованием следующих 18 сигналов МП-интерфейса (табл. 5.81).

Таблица 5.81 Дополнения в структуре внешних контактов контроллера

Ниже перечислены новые контакты, которые используются при работе МП-интерфейса:

MII_TX_EN - Transmit Enable. Разрешение передачи. Сигнал выставляется, когда на МП выставлены корректные данные, т. е. при начале передачи преамбулы контроллером, и сбрасывается по перепаду TX_CLK для последнего бита кадра.

MII_TX_Clk (Старое назначение контакта - IRQ7) - Transmit Clock. Внешняя тактовая частота для схем передат-чика TX_EN, TXD, TX_ER.

MIICRS - Carrier Receive Sense. Если входной сигнал CRS активен, то в сети присутствуе* какой-то обмен данными.

MII_COL - Collision Detect. Если в сети обнаружена коллизия, то выставляется этот сигнал, ко-с-рый остается активным в течение все- го времени обработки коллизии. Этот сигнал не определе-для полнодуплексного обмена.

MIIJVOO - Management Data I/O. Двунаправленная линия. Используется для обмена служебное информацией между блоками PHY и MAC. Обмен обычно синхронизируется сигналом на линии MDC

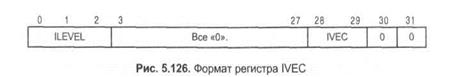

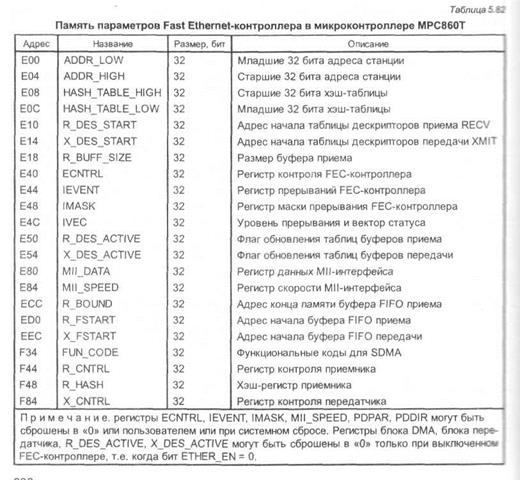

Настройка FEC-контроллера производится с помощью программирования регистров памяти параметров и буферных дескрипторов. Доступ к регистрам, которые расположены во внутренней двухпортовой памяти (табл. 5.82), и к буферным дескрипторам производится в режиме big-endian.

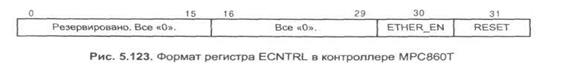

Регистр контроля ECNTRL (рис. 5.123) предназначен для включения/выключения FEC-контроллера пользователем. При установке бита ETHER__NET = 1 FEC-контроллер начинает работать. При сбросе этого бита контроллер немедленно прекращает прием кадра, а передача будет остановлена только после передачи неправильной CRC контрольной суммы в конце текущего кадра. При выключении контроллера указатели FIFO, буферные дескрипторы и схемы DMA сбрасываются.

При установке бита RESET := 1 производится сброс FEC-контроллера, аналогичный аппаратному сбросу или сбросу по команде процессора, все операции приема и передачи немедленно прекращаются.

В регистре R_HASH (рис. 5.124) пользователь может установить максимальную длину используемых кадров в байтах. Напомним, что при приеме/передаче кадра с длиной более указанной будет выработаны прерывания BABR/BABT. Стандарт 802.3 рекомендует устанавливать параметр MAX_FRAME_LENGTH равным 0х5ЕЕ, что соответствует 1518байтам

.

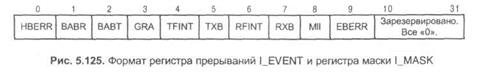

При возникновении определенных событий в канале связи происходит их регистрация в регистре прерываний MEVENT (рис. 5.125). Сброс бита события производится записью в выбранный разряд кода «1». Регистрация прерывания, связанного с любым из событий, может быть замаскирована пользователем при программировании регистра маски I_MASK. Форматы регистров прерываний и маски совпадают. Прерывание разрешено, если соответствующий бит в регистре маски установлен в «1».

Бит HBERR (Heartbeat Error) регистрируется, когда в слове состояния буферного дескриптора передачи был установлен бит ошибки НВС = 1, т. е. была обнаружена ошибка проверки аппаратуры.

Если был принят кадр длиной более 1518 байт, будет зарегистрирована ошибка Babbling Receive Error, которая фиксируется установкой бита ошибки BABR := 1.

Если из-за ошибок пользователя при программировании контроллер передал кадр длиной более 1518 байт, то будет зарегистрирована ошибка Babbling Transmit Error, которая фиксируется установкой бита ошибки ВАВТ := 1.

После завершения передачи полного кадра и заполнения слова состояния последнего буферного дескриптора регистрируется прерывание и устанавливается 6htTFINT :- 1 (Transmit Frame Interrupt). После передачи каждого отдельного буфера текущего кадра регистрируется прерывание и устанавливается бит ТХВ := 1 (Transmit Buffer Interrupt).