Регистр адреса цикла и регистр счетчика цикла (LA и LC)

Содержимое регистра адреса цикла LA указывает на местонахождение слова последней инструкции программного цикла. LC -специальный 16-битный счетчик, определяющий число повторений цикла.

При выполнении инструкции DO содержимое регистра LA помещается в SSH, а регистра LC -в SSL, откуда оно извлекается только после окончания цикла по инструкции ENDDO.

При выборке инструкции по адресу, содержащемуся в LA, проверяется содержимое LC Если содержимое LC не равно единице, оно декрементируется и следующая инструкция выбирается по адресу, находящемуся в верхней ячейке стека. В противном случае PC инкрементируется, флаг цикла сбрасывается, регистры LA и LC восстанавливаются из стека и продолжается нормальное выполнение программы.

Регистр LC программно доступен, и выполнение цикла может быть прекращено программным путем. Регистр LC также используется в инструкции REP.

Системный стек (SS).SS - отдельная внутренняя память размером 15 х 32 бита, разделенная на два блока: SSL и SSH. SSH сохраняет содержимое программного счетчика, SSL - регистра статуса при вызовах подпрограмм и длительных прерываниях. В стеке сохраняются также значения LA и LC при выполнении программных циклов. Стек обеспечивает выполнение 15 длинных прерываний, семи циклов DO, 15 вызовов подпрограмм. Если стек переполняется, возникает немаскируемое прерывание - ошибка стека. Значение PC теряется, что приводит к ошибке программы, выполняющейся, когда возникло прерывание по переполнению стека.

Указатель стека (SP). 6-битный указатель стека определяет последнюю занятую ячейку стека и состояние стека (потеря содержимого, пустой, полный, переполнение). Формат регистра SP указан на рис. 6.21.

Указатель стека (Р0,Р1,Р2—биты 0-3). Показывает последнюю используемую ячейку стека. После аппаратного сброса все биты равны нулю, что означает -стек пуст.

Флаг ошибки стека (SE- бит 4). Показывает возникновение ошибки стека. Если стек заполнен, указатель стека равен 001111, и любая операция, вызывающая запись в стек, приведет к возникновению ошибки стека, т. е. SP будет равен 010000. Аналогично, если SP равен 0, любая операция чтения из стека приведет к возникновению ошибки стека. Флаг ошибки стека остается равным единице, пока пользователь не сбросит его в «0».

Флаг потери содержимого (UF- бит 5). Устанавливается при потере содержимого стека. Сбрасывается в «0» пользователем.

Остальные биты стека зарезервированы для будущих разработок.

Состояния процессора

DSP всегда находится в одном из пяти состояний: нормальное, обработка исключения, сброс, ожидание и останов.

Нормальное состояние процессора связано с выполнением инструкций. Описание выполнения инструкций приведено в описании системы инструкций. Инструкции выполняются с использованием трехуровневого конвейера.

Состояние обработки исключения связано с прерываниями, которые генерируются как внутренними устройствами DSP, так и поступают от внешних источников.

Состояние сброса возникает при появлении сигнала активного уровня на контакте RESET. В этом состоянии происходит сброс внутренних периферийных устройств; регистры модификации устанавливаются в $FFFF; регистр уровней приоритета прерываний очищается; регистр BCR устанавливается в $FFFF, что добавляет 15 состояний ожидания ко всем обращениям к внешней памяти; указатель стека очищается; биты режима масштабирования, режима трассировки, флаг цикла и биты условий в SR сбрасываются, биты маски прерываний в SR устанавливаются в «1»; бит разрешения ПЗУ данных, бит задержки и битстробирования памяти сбрасываются. DSP не выходит из состояния сброса, пока на контакте RESET сохраняется сигнал активного уровня. После выхода из состояния сброса биты операционного режима в OMR загружаются извне по линиям MODA, MODB и выполнение программы начинается с адреса $Е000 в памяти программ в нормальном расширенном режиме или с адреса $0000 в остальных операционных режимах.

Состояние ожидания - это состояние пониженного энергопотребления, в которое процессор переходит при выполнении инструкции WAIT. В состоянии ожидания запрещена внутренняя синхронизация всех устройств на кристалле, за исключением внутренней периферии (генератор частоты работает). Все внутренние процессы остановлены до тех пор, пока не поступит немаскируемое прерывание или не будет произведен сброс.

Состояние останова - это состояние самого низкого энергопотребления, в которое процессор переходит при выполнении инструкции STOP. В этом состоянии генератор частоты отключен. При переходе в состояние останова кристалл сбрасывает все прерывания от периферийных устройств и внешние прерывания. Уровни приоритетов прерываний остаются такими же, как перед выполнением инструкции STOP. Процессор остановлен до тех пор, пока не появится сигнал низкого логического уровня на контакте lRQA или на контакте RESET. Эти события включают генератор, и после стабилизации частоты включается синхронизация всех устройств на кристалле. Период стабилизации частоты определяется битом SD в OMR.

ПОРТА

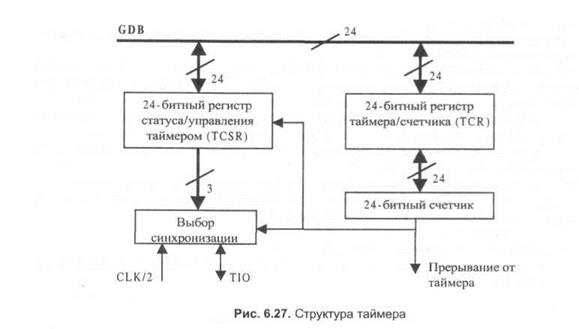

Порт А может использоваться для расширения памяти или обычного ввода/вывода. Шина данных порта А имеет разрядность 24 бита, шина адреса разрядностью 16 бит обеспечивает доступ к памяти за один машинный цикл (рис. 6.22).

Интерфейс порта А

Во время выполнения инструкции могут быть доступны следующие блоки памяти DSP: Х-память данных, Y-память данных, память программ или несколько блоков сразу.

Каждый из этих блоков памяти может быть внутренним или внешним. Шины данных и адреса порта А обеспечивают доступ к внешней памяти.

На рис. 6.22 показаны сигналы порта А. Все сигналы разделены на три функциональные группы: адресные, данных и управления.

Сигналы шины управления также подразделяются на три группы: управление чтением и записью, выбор адресного пространства, управление доступом к шине. Сигналы управления чтением и записью могут быть декодированы как сигналы чтения и сигналы записи или сигнал записи может использоваться в качестве сигнала чтения/записи, сигнал чтения - в качестве выхода разрешения доступа к памяти. Сигналы выбора памяти программ, памяти данных и типа памяти данных могут рассматриваться как дополнительные адресные линии, позволяющие расширять пространство адресуемой памяти от 64Кдо 192Кслов.

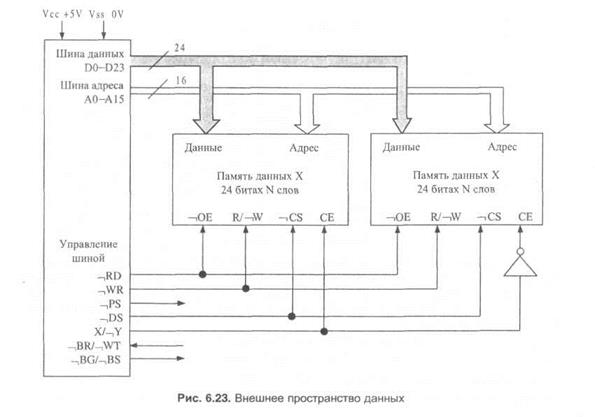

На рис. 6.23 показано использование сигнала выбора памяти данных для доступа к двум блокам памяти данных и использование сигнала XY для переключения между ними.

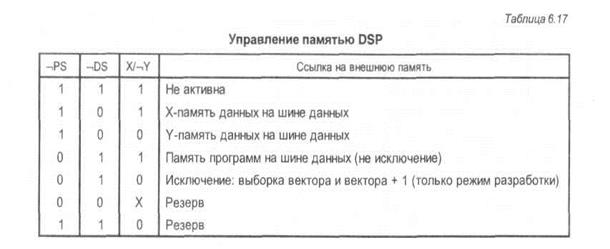

Одиночный блок памяти может использовать сигналы PS, DS, X/Y в качестве дополнительных адресных линий для сегментации памяти на три пространства. В табл. 6.17 приведены варианты использования этих сигналов.

Простой вариант подключения периферийных устройств семейства МС6800 заключается в использовании линии X/Y для указания R/W.

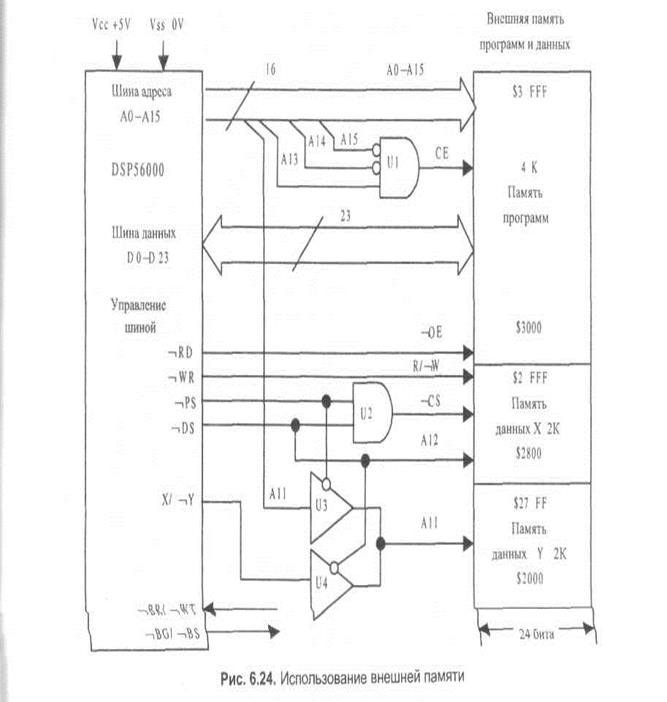

Выбор кристалла периферии должен осуществляться с помощью линий адреса и строба данных так, чтобы регистры периферийных устройств находились в пространствах X и Y по одним и тем же адресам. На рис. 6.24 приведена структурная схема системы ЦОС с внешней памятью на основе DSP56000 и показаны сигналы управления блоками памяти данных и программ.

Для операции чтения применяется чтение памяти X:

MOVE X:PERIPHERAL,XO ; X/Y имеет высокий уровень.

Для операции записи применяется запись в память Y:

MOVE XO,Y:PERIPHERAL ; X/Y имеет низкий уровень.

Отдельные сигналы стробирования чтения и записи, используемые в DSP, являются взаимоисключающими и позволяют осуществлять доступ к двум буферам данных одновременно без конфликта.

Использование внешней логики позволяет подключать более быстрые ОЗУ или внешние буферы данных без конфликтов на шине данных.

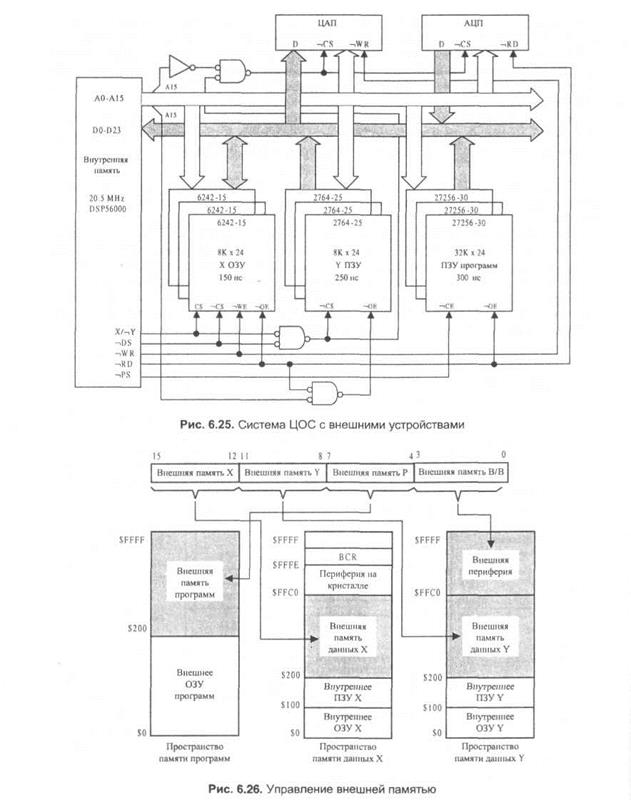

На рис. 6.25 приведен пример расширенной системы с устройствами разного быстродействия.

Регистр управления шиной (ВСR). Регистр определяет синхронизацию расширения шины с использованием сигналов RD и WR и выходных линий данных. Этот регистр имеет адрес $FFFE в памяти X. Каждое из пространств памяти имеет свой собственный

4-битовый BCR, который программирует до 15 состояний ожидания (каждое состояние занимает половину цикла инструкции при доступе к памяти - 50 не на частоте 20 МГц). После сброса процессора все разряды регистра равны единице (15 состояний ожидания). Содержимое BCR должно соответствовать используемой памяти, иначе процессор вставит 15 состояний ожидания между выборками из памяти и DSP будет работать медленнее.

На рис. 6.26 показаны все четыре поля регистра BCR для работы с внешней памятью. Все периферийные устройства на кристалле входят в карту памяти, регистры управления ими расположены в диапазоне адресов X:$FFC0 - X:$FFFF.

Таймер DSP56002

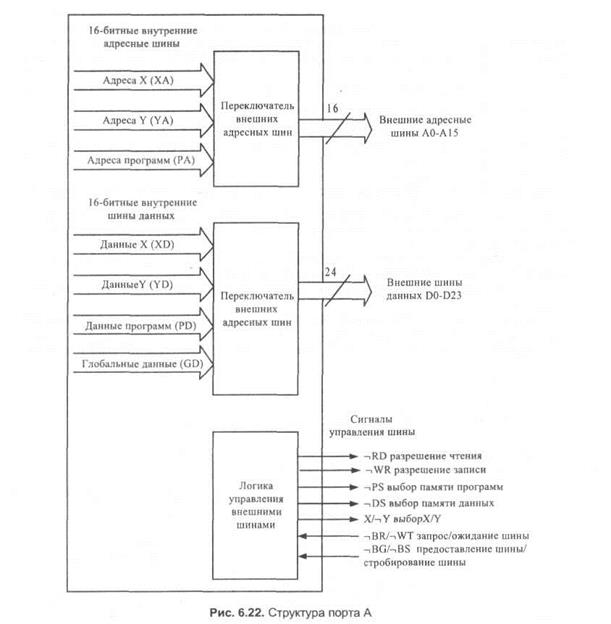

Таймер использует внутреннюю или внешнюю синхронизацию и может прерывать работу процессора через заданное пользователем число тактов или выдавать сигнал внешним устройствам после подсчета внутренних событий.

С внешней средой таймер соединен двунаправленной линией ТIO. Если ТIO используется как вход, модуль таймера функционирует как счетчик внешних событий по этой линии, иначе модуль функционирует как таймер и на линию ТIO выдается пульсация таймера. Линия ТIO может использоваться также как линия ввода/вывода общего назначения.

Таймерный модуль, структура которого приведена на рис. 6.27, включает в себя 24-битный регистр статуса/управления таймером, 24-битный регистр таймера/счетчика, логику выбора синхронизации и генерации прерывания.

|