Организация функционирования микропроцессора

8.2.1. Структурная схема микропроцессора КР580ВМ80А

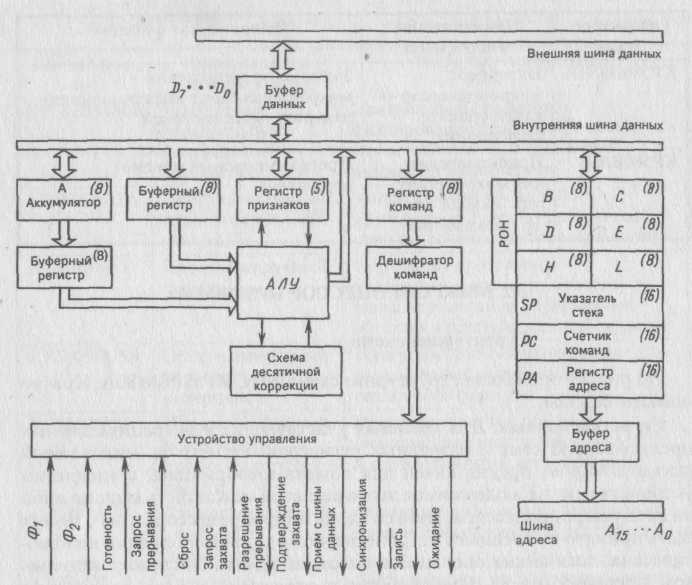

На рисунке 8.2.1.1. приведена структурная схема БИС КР580ВМ80А. Кратко опишем ее узлы.

Регистры данных. Для хранения участвующих в операциях данных предусмотрено семь 8-разрядных регистров. Регистр А (код 111), называемый аккумулятором, предназначен для обмена информацией с внешними устройствами (т.е. содержимое этого регистра может быть выдано либо на вход микропроцессора, либо со входа микропроцессора в него может быть принято от внешнего устройства число), при выполнении арифметических, логических операций и операций сдвига он служит источником операнда (числа, участвующие в операции), в него помещается результат выполненной операции. Шесть других регистров, обозначенных В (код 000), С (код 001) D (код 010), E (код 011), H (код 100), L (код 101), образуют блок регистров общего назначения (РОН) (название связано с тем, что в этих регистрах могут храниться как данные, так и адреса). Эти регистры могут использоваться как одиночные 8-разрядные регистры. Если необходимо хранить 16-разрядные двоичные числа, регистры объединяются в пары ВС, DE, HL.

Указатель стека. Регистр SP (16-разрядный) служит для адресации особого вида памяти, называемой стеком (организация стека будет рассмотрена ниже).

Счетчик команд. Регистр PC (16-разрядный) предназначен для хранения адреса команды; после выборки из оперативной памяти текущей команды содержимое счетчика увеличивается на единицу, и таким образом формируется адрес очередной команды (при отсутствии безусловных и условных переходов).При обращении к памяти в качестве адреса может использоваться и содержимое пары регистров блока РОН. При выдаче адреса содержимое соответствующего регистра передается в 16-разрядный регистр адреса РА, из которого далее через буферы адреса адрес поступает на 16-разрядную шину адреса.

Рисунок 8.2.1.1. Структурная схема БИС КР580ВМ80А

С этой шины адрес может быть принят в оперативную память. Число кодовых комбинаций 16-разрядного адреса равно 216, каждая из этих кодовых комбинаций может определять адрес (номер) одной из ячеек оперативной памяти. Таким образом обеспечивается возможность обращения к памяти, содержащей до 216 = 26 • 210 = 64 К 8-разрядных слов (байтов).

Арифметико-логическое устройство. В 8-разрядном АЛУ предусмотрена возможность выполнения четырех арифметических операций (сложение с передачей переноса в младший разряд и без учета этого переноса, вычитание с передачей заема в младший разряд и без него), четырех видов логических операций (конъюнкции, дизъюнкции, неравнозначности, сравнения), а также четырех видов циклического сдвига. При реализации арифметических и логических операций одним из операндов служит содержимое аккумулятора, результат операции помещается в аккумулятор. Циклический сдвиг выполняется только над содержимым аккумулятора.

Предусмотрена возможность выполнения арифметических операций над десятичными числами, представленными в коде 8421. При хранении десятичного числа разряды регистра делятся на две группы по четыре разряда, и в каждой группе разрядов хранится одна десятичная цифра, представленная в коде 8421. Таким образом, в регистре можно хранить 2-разрядное десятичное число. При выполнении операции суммирования десятичных цифр может потребоваться коррекция результата путем прибавления к нему числа 01102. Такая коррекция результата в каждой 4-разрядной группе результата в микропроцессоре выполняется схемой десятичной коррекции (СДК).

Регистр признаков (РП). Этот 5-разрядный регистр предназначен для хранения определенных признаков, выявляемых в числе, которое представляет собой результат выполнения некоторых операций. Пять триггеров этого регистра имеют следующее назначение:

триггер переноса Тс при выполнении арифметических операций устанавливается в состояние, соответствующее переносу из старшего разряда числа, при выполнении операции сдвига – в состояние, соответствующее содержимому выдвигаемого из аккумулятора разряда;

триггер нуля Tz устанавливается в состояние 1, если результат операции АЛУ или операции приращения содержимого регистра равен нулю;

триггер знака Ts устанавливается в состояние, соответствующее значению старшего разряда результата операции АЛУ или операции приращения содержимого регистра;

триггер четности Тp устанавливается в состояние 1, если число единиц в разрядах результата четное;

триггер дополнительного переноса Tv хранит возникающий при выполнении операции перенос из 4-го разряда.

Блок управления. Состоит из регистра команд, куда принимается первый байт команды, и устройства управления, формирующего управляющие сигналы, под действием которых выполняются микрооперации в отдельных узлах. Управляющее устройство содержит выполненную на программируемой логической матрице управляющую память, в которой хранятся микропрограммы отдельных операций. Пользователь не может изменить содержимого управляющей памяти, а значит, и состава команд.

Буферы. Буферы данных и буферы адреса обеспечивают связь центрального процессора с внешними шинами данных и адреса. Особенность буферов состоит в том, что в каждом разряде они используют логические элементы с тремя состояниями. В них кроме состояний 0 и 1 предусмотрено еще третье состояние, в котором они имеют практически бесконечное выходное сопротивление и оказываются отключенными от соответствующих шин.

8.2.2. Формат данных и команд

Данные (обрабатываемая информация и результаты обработки) хранятся в оперативной памяти и в процессоре в виде 8-разрядных двоичных чисел. Таким образом, слово имеет следующий формат:

| Байт B1 |  |

Для команд используются одно-, двух- и трехбайтовые форматы. Однобайтовая команда занимает одну ячейку оперативной памяти.

| Байт B1 |  |

В разрядах команды записывается вид операции, а также записываются или подразумеваются источники операндов и приемник результата.

Двухбайтовая команда занимает две ячейки оперативной памяти.

| Байт B1 |  |

| Байт B2 |  |

В первом байте двухбайтовой команды указывается код выполняемой операции, во втором байте приводится число, являющееся операндом, либо адрес устройства ввода или вывода при обмене данными с периферийными устройствами

Трехбайтовая команда занимает три ячейки оперативной памяти.

| Байт B1 |  |

| Байт B2 |  |

| Байт B3 |  |

В первом байте трехбайтовой команды указывается код выполняемой операции, во втором и третьем байтах приводится число, являющееся операндом, или адрес ячейки оперативной памяти, где хранится операнд или команда (в командах переходов и обращений к подпрограммам). Во всех случаях байт В2 является младшим, байт В3 – старшим.

8.2.3. Способы адресации

Большинство микропроцессоров выполняют обработку следующих типов целочисленных данных:

• биты; \

• байты;

• слова (16 разрядов);

• двойные слова (32 разряда).

Некоторые типы микропроцессоров обрабатывают также четверные слова (64 разряда), двоично-десятичные, строки символов. В состав современных высокопроизводительных микропроцессоров входят также блоки, производящие обработку чисел, представленных в формате с плавающей точкой (блоки FPU – Floating Point Unit), и выполняющие обработку видео- и аудиоданных, для которых используются специальные форматы представления.

Обрабатываемые данные – операнды могут располагаться в регистрах или памяти (ОЗУ, ПЗУ или кэш-памяти). Выборка операнда – байта, слова или двойного слова производится в соответствии с заданным в команде номером (именем) регистра или адресом соответствующей ячейки памяти.

При размещении в памяти команд и данных используются два варианта расположения байтов в словах:

1)начиная с младшего байта («Little-Endian»);

2)начиная со старшего байта («Big-Endian»).

Различные типы микропроцессоров используют следующие основные способы адресации операндов.

1). Прямая адресация. Операнд выбирается из ячейки памяти, адрес которой содержится в команде.

2). Регистровая адресация. Операнд выбирается из регистра РЗУ, номер (имя) которого указано в команде.

3). Косвенно-регистровая адресация. Операнд выбирается из ячейки памяти, адрес которой содержится в регистре РЗУ, указанном в команде.

4). Косвенно-регистровая адресация со смещением. Операнд выбирается из ячейки памяти, адрес которой является суммой содержимого указанного в команде регистра РЗУ и заданного в команде смещения (смещение может быть положительным или отрицательным числом).

5). Косвенно-регистровая адресация с индексированием и смещением. Операнд выбирается из ячейки памяти, адрес которой является суммой содержимого указанного в команде регистра, индексного регистра и заданного в команде смещения

6). Относительная адресация. Операнд выбирается из ячейки памяти, адрес которой является суммой текущего содержимого программного счетчика PC и заданного в команде смещения (числа со знаком). Этот способ адресации часто используется для формирования адреса команды, к которой переходит программа при выполнении команд ветвления

7). Непосредственная адресация. В этом случае операнд непосредственно содержится в поступившей команде, размещаясь следом за кодом операции (КОП).