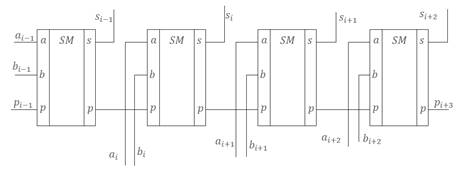

Параллельный сумматор с последовательным переносом.

Параллельный сумматор с последовательным переносом содержит одноразрядные сумматоры, число которых равно разрядности суммируемых двоичных слов. По цепям переноса сумматоры соединены последовательно. Импульс переноса в каждом сумматоре формируется после того, как будет сформирован и поступит на сумматор перенос из предыдущего разряда. Поэтому быстродействие параллельного сумматора с последовательным переносом невысокое.

Функциональная схема параллельного сумматора с последовательным переносом .

Дешифраторы.

Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов.

Если на входы дешифратора подаются бинарные переменные из 0 или 1, то на одном выходе будет 1, на остальных выходах – 0.

В общем случае дешифратор с  входами имеет

входами имеет  выходов. Значения выходных переменных описываются логическими выражениями:

выходов. Значения выходных переменных описываются логическими выражениями:

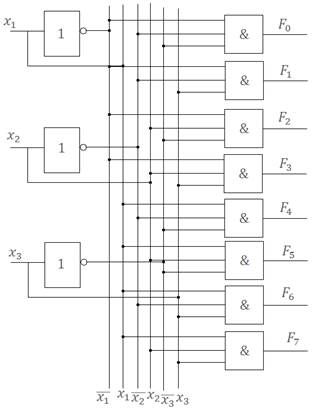

Структура дешифратора представлена на рисунке

Дешифраторы при относительно малом числе элементов и несложной внутренней структуре имеют большое число внешних выходных выводов. Поэтому не изготавливают дешифраторов с более чем 4 информационными входами. Увеличение числа выходов осуществляется путем применения многокаскадных схема.

Мультиплексоры.

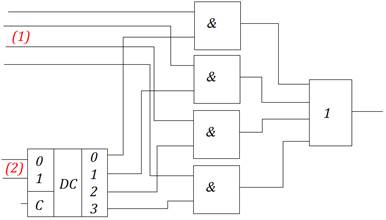

Mультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

информационные каналы,

информационные каналы,  каналы управления.

каналы управления.

Функциональная схема мультиплексора.

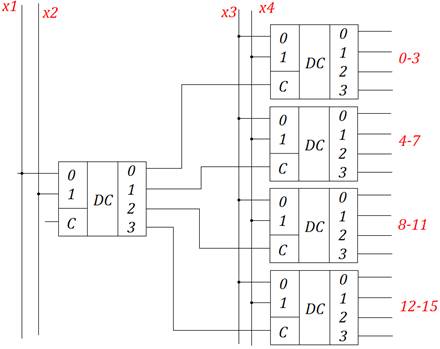

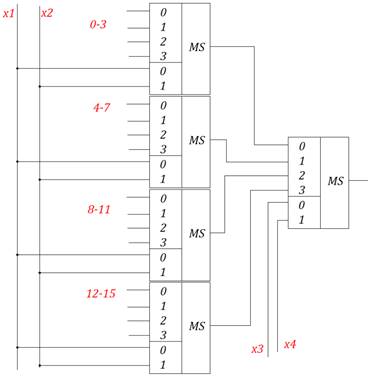

Многокаскадная схема для мультиплексора.

Задание к лабораторной работе №1

1. Из элементов И, ИЛИ, И-НЕ, ИЛИ-НЕ построить функциональную схему одноразрядного комбинационного сумматора.

2. Смоделировать работу одноразрядного комбинационного сумматора.

3. Построить из одноразрядных комбинационных сумматоров 4-хразрядный параллельный сумматор с последовательным переносом.

4. Смоделировать работу 4-хразрядного параллельного сумматора с последовательным переносом.

5. Из элементов И, ИЛИ, И-НЕ, ИЛИ-НЕ построить функциональную схему дешифратора.

6. Смоделировать работу дешифратора.

7. Из отдельных дешифраторов построить многокаскадный дешифратор.

8. Смоделировать работу многокаскадного дешифратора.

9. Из элементов И, ИЛИ, И-НЕ, ИЛИ-НЕ и дешифраторов построить функциональную схему мультиплексора.

10. Смоделировать работу мультиплексора.

11. Из отдельных мультиплексоров построить многокаскадный мультиплексор.

Лабораторная работа № 2.

Целью лабораторной работы является изучение принципов работы RS-триггеров, D-триггеров, T-триггеров, JK-триггеров.

Триггеры

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Одноступенчатые триггеры состоят из одной ступени представляющей собой элемент памяти и схему управления, делятся на триггеры со статическим управлением и триггеры с динамическим управлением.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Двухступенчатые триггеры бывают, как правило, со статическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатые триггеры с динамическим управлением встречаются крайне редко. Двухступенчатый триггер обозначают ТТ.

Триггеры со сложной логикой бывают также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют и асинхронные. Такой триггер изображён на рис. 1, верхний (S) и нижний (R) входные сигналы являются асинхронными.

Работа триггеров описывается с помощью таблицы переключений, являющейся аналогом таблицы истинности для комбинационной логики. Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) либо (t-1) или после подачи сигнала (t+1) или (t). В триггерах с парафазным (двухфазным) выходом имеется второй (инверсный) выход, который обозначают как Q, /Q или Q'.

Типы триггеров

RS-триггеры

RS-триггер асинхронный

| S | R | Q(t) | Q(t) | Q(t+1) | Q(t+1) |

| не определено | не определено | ||||

| не определено | не определено |

Асинхронный RS-триггер с инверсными входами

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

Условное графическое обозначение асинхронного RS-триггера

Логическая схема асинхронного RS-триггера на элементах 2И–НЕ

Асинхронный RS-триггер на логических элементах 2ИЛИ-НЕ

RS-триггер синхронный

| C | S | R | Q(t) | Q(t+1) |

| x | x | |||

| не определено | ||||

| не определено |

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой

где x — неопределённое состояние.

Условное графическое обозначение синхронного RS-триггера

Схема синхронного RS-триггера на элементах 2И-НЕ

D-триггеры

D-триггеры также называют триггерами задержки(от англ. Delay).

D-триггер синхронный

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

| D | Q(t) | Q(t+1) |

D-триггер (D от англ. delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

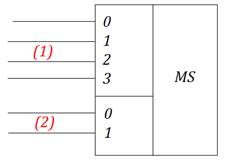

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Условное графическое обозначение D-триггера со статическим входом синхронизации С

T-триггеры

Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2.

Т-триггер асинхронный

Асинхронный Т-триггер не имеет входа синхронизации С.

T-триггер синхронный

| T | Q(t) | Q(t+1) |

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер может строиться на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в двухступенчатом (Master-Slave, MS) D-триггере динамического входа С позволяет получить на его основе T-триггер. При этом инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение  , то есть будет переключаться в противоположное состояние.

, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

JK-триггеры

JK-триггер

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J | K | Q(t) | Q(t+1) |

JK-триггер[18][19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[20].

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом

Задание к лабораторной работе №2.

1. Из элементов И, ИЛИ, И-НЕ, ИЛИ-НЕ построить функциональные схемы RS-триггеров, D-триггеров, T-триггеров, JK-триггеров.

2. Смоделировать работу RS-триггеров, D-триггеров, T-триггеров, JK-триггеров.

Лабораторная работа № 3.

Счетчики.

Целью лабораторной работы является изучение принципов работы 4-хразрядного двоичного суммирующего счетчик с последовательным переносом и 4-хразрядного двоичного суммирующий счетчик с параллельным переносом.

Счетчик импульсов – это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающееся в изменении значения числа в счетчике на 1. По существу счетчик представляет собой совокупность соединенных определенным образом триггеров.

Классификация счетчиков.

По модулю счета:

- двоично-десятичные; двоичные;

- с произвольным постоянным модулем счета;

- с переменным модулем счета.

По направлению счета:

- суммирующие;

- вычитающие;

- реверсивные .

По способу формирования внутренних связей:

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- кольцевые.