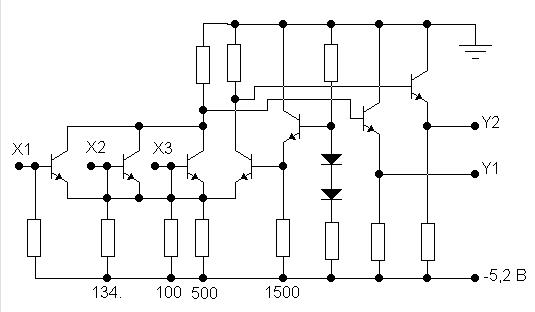

ЭСЛ – эмиттерно-связанная логика

U0 = -0,7 ÷ -0,95 ≈ -0,8

U1 = -1,45 ÷ -1,95 ≈ -1,6

Высокое быстродействие достигается тем, что транзисторы дифференциального каскада и другие не входят в режим насыщения, а также малой разницей между уровнем логического «0» и логической «1» (0,8В). Последнее, в свою очередь, ухудшает помехоустойчивость. Для согласования микросхем различных видов логики используются микросхемы преобразования уровня.

КМОП.

Стандартный КМОП допускает использование Uп от 5В до 15В. Быстродействие изменяется в три раза, возрастает и мощность. Это позволяет непосредственно соединить схемы КМОП и ОУ.

Двунаправленный ключ.

При изменении входного сигнала сопротивление каналов транзистора с n и p каналом изменяется в противоположную сторону. Специальные схемные решения позволяют сделать эквивалентное сопротивление ключа независимым от величины и направления входного сигнала. Величина сопротивления канала ключа достигает единиц Ом. При отсутствии отпирающего напряжения на затворе сопротивление велико (десятки МОм), что равносильно разрыву цепи. Омический характер сопротивления канала позволяет использовать двунаправленные ключи не только для переключения логических сигналов, но и (в отличие от ТТЛ) для переключения аналоговых сигналов, а также для регулировки последних, используя ключ в этом случае в качестве переменного резистора, управляемого напряжением.

Инвертор КМОП

Защитные диоды обязательно присутствуют во всех логических элементах КМОП, так как они подвержены разрушающему воздействию статического электричества. В инверторе VD3, VD5, VD6 защитные элементы от отрицательных импульсов. Диоды VD1, VD2, VD4 защищают вход и выход от положительных выбросов и ограничивают его на уровне Uп+0,6. Для дополнительной защиты входов, особенно при длинных входных проводах, и для устранения паразитных колебаний последовательно с входом включают резистор для ограничения тока заряда включения емкости.

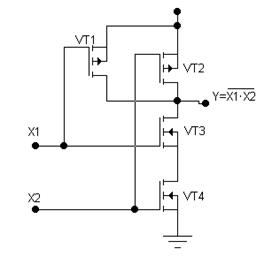

Схема И-НЕ

Схема И-НЕ

При логической «1» n-каналы VT3 и VT4 открыта, а p-канальные VT1 и VT2 – заперты на входе логического «0». При подаче хотя бы одного логического «0» на вход, оказывается запертым одним из VT3 или VT4 и открытым хотя бы один из VT1 и VT2, что даст логическую «1» на выходе.

Схема ИЛИ-НЕ

Схема ИЛИ-НЕ

При двух логических «0» входы VT1 и VT2 закрыты, а VT3 и VT4 открыты. На выходе – логическая «1». При логической «1» на любом из выходов по крайней мере один из n-каналов и хотя бы один из последовательных соединений p-каналов закрыт. На выходе 0.

Существует логические элементы с открытым стоком.

Не использованные входы КМОП надо включать так, чтоб не нарушались условия работы микросхемы в целом. В отличие от ТТЛ можно подключить к Uп напрямую. Нельзя оставлять неподключенными. При случайном соединении выхода с системой питания или с общей линией через открытие. Транзистор пропускает ток, ограниченный только сопротивлением канала и внутренним сопротивлением источника питания. Ток короткого замыкания и мощность рассеивания увеличиваются с ростом напряжения питания. При напряжении питания не более 5В и комнатной температуре 25˚С микросхема не выходит из строя при достаточно долговременном коротком замыкании.

Сопряжение КМОП и ТТЛ.

При сопряжении КМОП и ТТЛ к выходу КМОП можно подключить два входа ТТЛ 155серии и до девяти входов 555 серии. При подключении выхода ТТЛ ко входу КМОП необходимо включить резистор с выхода ТТЛ на источник питания (2кОм) с целью повышения уровня логической «1».

Разновидности функциональных схем:

- комбинационные схемы

- последовательные устройства

Комбинационные схемы характеризуются отсутствием памяти (память – свойство системы сохранять в течении требуемого времени значение сигнала, характеризующее внутреннее состояние цифрового устройства). Сигнал на выходе комбинационного устройства в любой момент времени однозначно определяется сочетанием сигналов на входе и не зависит от его предыдущего состояния. Схемным признаком таких схем является осуществление в цепи обратной связи. Примеры: логические элементы, эл. ключи, дешифраторы, арифметические устройства.

Последовательные схемы обладают памятью и при смене цифр на входе, для предсказания сигнала на выходе, необходимо знать о состоянии, в котором устройство было до этого. В этих устройствах есть обратная связь. Простейшие из них – триггеры, счетчики, резисторы, запоминающие устройства.

Параметры цифровых элементов:

1)надежность – интенсивность отказов  , наработкой на отказ Т, вероятность безотказной работы

, наработкой на отказ Т, вероятность безотказной работы  ;

;

2)стойкость к механическим и климатическим воздействиям - вибрации, ударам, центробежным силам, воздействиям атмосферы и т.д.

3) быстродействие – прямо пропорционально потребляемой мощности;

4) мощность рассеивания;

5) нагрузочная способность - при исполнении микросхем разных серий количество входов будет различным. Оно может быть указано в таблице, либо рассчитано по входным и выходным токам;

6) помехоустойчивость;

7) степень интеграции.

Интегральные триггеры. Асинхронные и синхронные триггеры. RS-, JK-, D- и Т-триггеры. Принцип действия, структурные и принципиальные схемы, временные диаграммы работы триггерных схем, их основные параметры. Применение триггерных схем для создания цифровых систем управления.

Триггеры – класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких возможных) устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Одно из основных применений – запоминание информации.

Под памятью триггера подразумевают способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит или помнит один разряд двоичного числа.

|  | ||||

| Rn | Sn | Q |  | ||

|  | ||||

| н/о | н/о | ||||

| н/о | н/о | ||||

|  | ||||

Недостаток: неопределенное состояние.

Для исключения неопределенного состояния разработаны модификации RS-триггеров, у которых при запрещенных входных комбинациях выходной сигнал принимает следующие значения:

R-триггер - 0

S-триггер - 1

E-триггер – Qn

JK-триггер -

Триггерные системы - RS-триггер как ячейка памяти и устройство управления.

J, K, V, (T)C – внешние входы; Ra, Sa – внешние входы ячейки памяти; Q,  - внешние выходы; S', R' – внутренние входы ячейки пямяти.

- внешние выходы; S', R' – внутренние входы ячейки пямяти.

Функциональное назначение внешних входов

| усл. обозн. | назначение |

| информационные входы | |

| S | вход раздельной установки триггера в состоянии «1» |

| R | вход раздельной установки триггера в состоянии «0» |

| J | вход установки JK-триггера в состоянии «1» |

| K | вход установки JK-триггера в состоянии «0» |

| T | вход счетного триггера |

| D | вход установки D- или DV-триггера в состоянии «1» или «0» |

| управляющие входы | |

| V | подготовительный вход разрешения приема информации |

| C | вход синхронизации (тактирующий) |

УУ – комбинационное устройство, преобразующее входную информацию в комбинацию сигналов, под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний. Изменяя схему УУ и способы ее связи с ячейкой памяти можно получить триггеры с различными функциональными свойствами. Сигнал на информационном входе определяется информацией, которая будет записываться с триггер. С помощью подготовительного сигнала можно в нужный момент прервать действие триггера или группы триггеров, сохраняя информацию на выходе (V-сигнал). Исполнительные сигналы (С-сигнал) задают момент приема входной информации и служат для синхронной работы ряда устройств, образующих функциональные узлы.