Семисегментный индикатор с динамической индикацией.

Цель: собрать схему динамической развертки на данном стенде для вывода четырехзначного числа.

Общие указания:

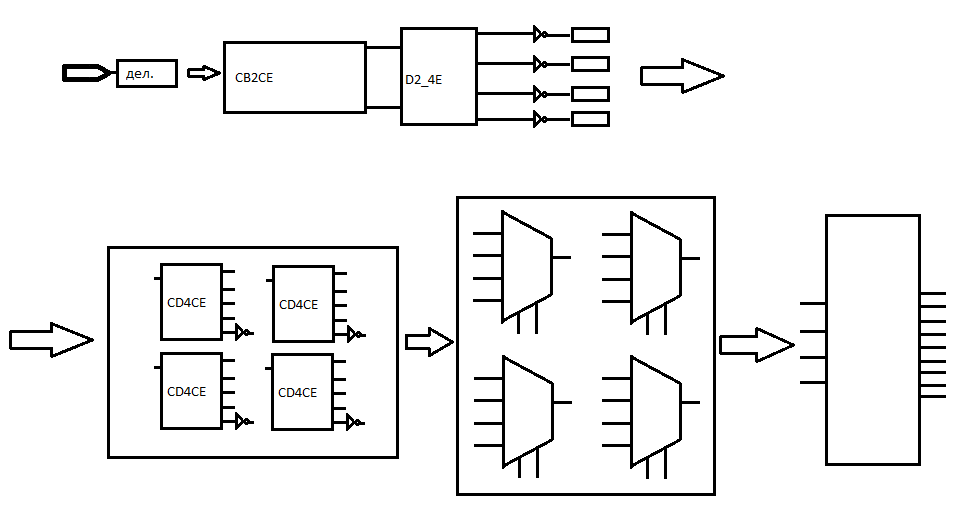

На рисунке 3.31 изображена схема динамической индикации.

Рисунок 3.31- Динамическая индикация

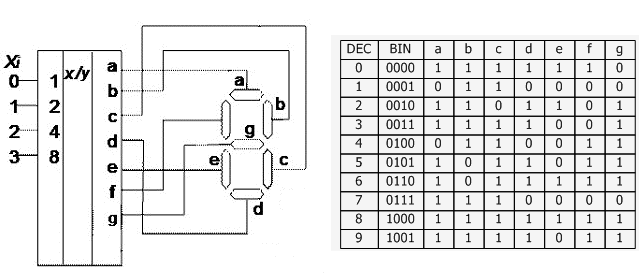

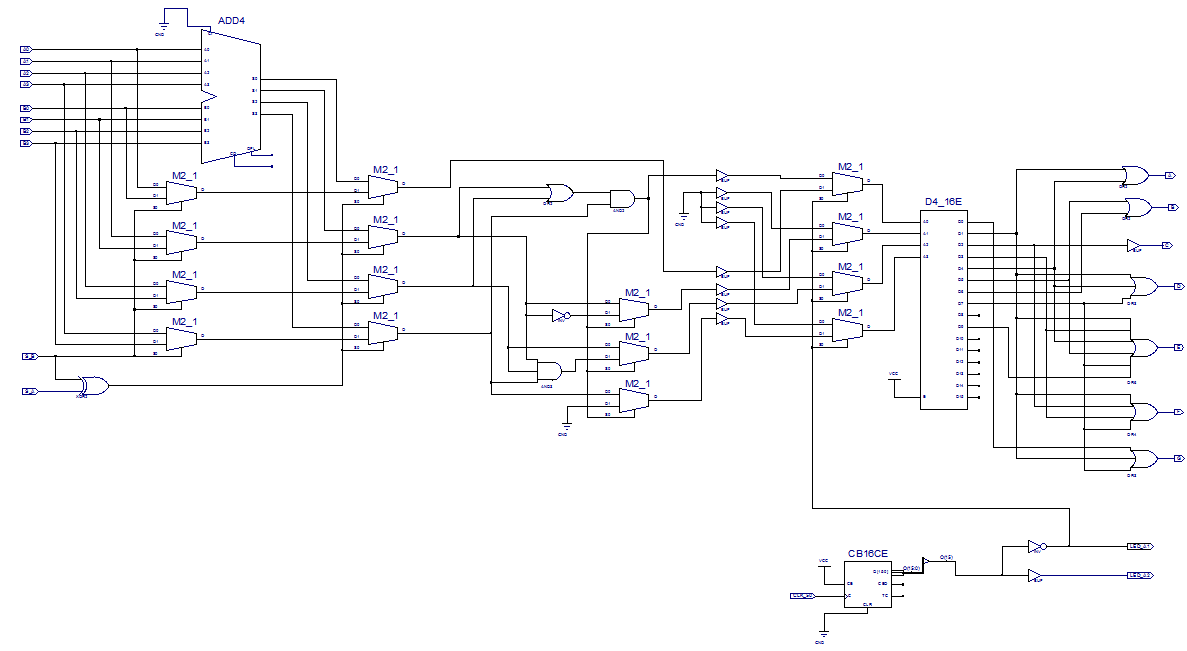

На рис. 3.32 схема подключения преобразователя к семисегментному индикатору

Рисунок 3.32- Схема подключения преобразователя к семисегментному индикатору

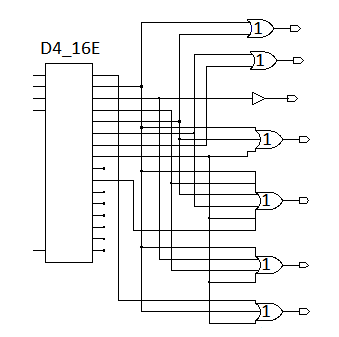

1. Выбираем дешифратор D4_16E. Дешифратор имеет 4 входа и 16 выходов.

2. Собираем схему семисегментного преобразователя на элементах стандартной логики.

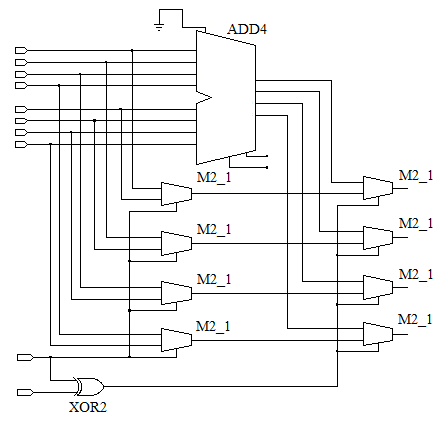

3. На рисунке 3.33 изображена схема динамической развертки.

Рисунок 3.33 - Блок-схема динамической развертки

4. Собранную схему проверить на стенде.

Лабораторная работа №7

Кодер BСD-код

Цель: построить схему кодера BDC кода.

Общие указания:

BCD- схема двоично-десятичного преобразователя (англ. binary-coded decimal), BCD, 8421-BCD — форма записи рациональных чисел, когда каждый десятичный разряд числа записывается в виде его четырёхбитного двоичного кода

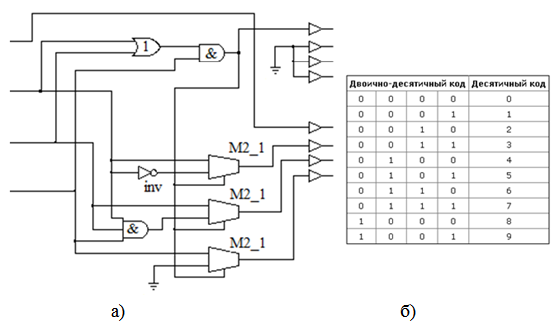

На рисунке 41 изображен BCD код с таблицей истинности

Рисунок 3.34. а)BCD – кодер; б) таблица истинности .

Лабораторная работа №8

Сумматор двоичного кода

На рисунке 42 приведена схема сложения двух четырехразрядных чисел.

Рисунок 3.25. - Схема двоичного сумматора

1. Схема сумматора строится на базовых элементах, находящихся в библиотеке САПР ISEDesignSuite 14.4.

2. Проверить работу сумматора, подключив BCD и динамическую развертку (см. лабораторные №6 и №7)

На рисунке 3.26 изображена схема полного сумматора.

Рисунок 3. 26. - Схема полного сумматора

Процесс разработки комплекса лабораторных работ был разбит на несколько этапов:

- Выбор стенда (ПЛИС XC9500XL);

- Разработка лабораторных работ;

- Решение лабораторных работ.

Применение лабораторных работ предназначено для изучения:

- систем на базе программируемых логических интегральных схем фирмы XILINX с архитектурой CPLD;

- принципов логического проектирования несложных узлов цифровых систем с использованием языков структурно–функционального описания аппаратуры;

- периферийных блоков вычислительных систем;

- подсистем ввода-вывода встраиваемых систем.

Возможно проведение данных лабораторных работ по следующим дисциплинам:

- цифровая схемотехника;

- цифровая обработка сигналов;

- цифровые устройства и микропроцессоры;

БИБЛИОГРАФИЧЕСИКЙ СПИСОК

1 Описание ПЛИС :http://plis.ru/docum#63& (дата обращения: 3.04.2015).

2 Зотов В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. - М.: Горячая линия-Телеком, 2003. - 624 с.

3 Фирма Altera: http://www.altera.ru/s-chego-nachat.html (дата обращения: 11.04.2015).

4Зотов В. Разработка встраиваемых микропроцессорных систем на основе ядра MicroBlaze, реализуемых в ПЛИС семейств FPGA фирмы Xilinx, с помощью «мастера» BaseSystemBuilderWizard // Компоненты и технологии. 2005. №№ 3–4

5 Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. - М.: Горячая линия-Телеком, 2006. - 520 с.

6 Разработка устройства на ПЛИС: http://knowledge.allbest.ru

7. ПЛИС:https://ru.wikipedia.org/wiki/%D0%9F%D0%9B%D0%98%D0%A1

8 Программируемые логические схемы и их применение:http://fpga-faq.narod.ru/ (дата обращения 15.04.2015).