Структура и классификация интегральных триггеров

Интегральные триггеры используются как самостоятельные устройства и, кроме того, входят в состав различных функциональных устройств: счетчиков, регистров, запоминающих устройств и т. п. Современные интегральные триггеры часто строятся на основе нескольких логических элементов, объединенных в одну микросхему. Они могут иметь несколько входов и различаться способами ввода входной информации. Для преобразования входной информации в требуемую комбинацию управляющих сигналов в триггере имеется устройство управления. Это устройство позволяет значительно расширить функциональные возможности триггера.

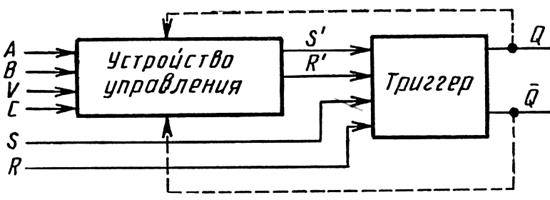

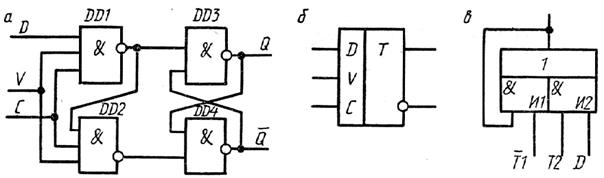

Обобщенная структурная схема триггера с устройством управления показана на рис. 12.5. Входные сигналы

Рис. 12.5 Структурная схема триггерной системы:

А, В — информационные (логические) входы; V — подготовительный вход; С — тактовый (синхронизирующий) вход; S' и R' — внутренние входы;

S и R — внешние входы; Qи Q— внешние выходы

S и R — внешние входы; Qи Q— внешние выходы

А, В, V, С, S, R в зависимости от выполняемой роли подразделяются на информационные (логические), подготовительные (разрешающие) и исполнительные (командные). Входы триггера, на которые подаются эти сигналы, соответственно носят названия: информационные (логические), предустановочные (подготовительные) и тактовые (синхронизирующие). В зависимости от назначения триггера предустановочные и тактовые входы могут отсутствовать, в то время как информационные входы имеются у каждого триггера.

На схемах входы триггера обозначают буквами латинского алфавита в соответствии с табл. 12.1. По названиям информационных входов называют и триггеры: RS-триггер, D-триггер, JK-триггер и др.

В зависимости от схемы управляющего устройства триггеры делятся на синхронные и асинхронные (от греч. а — не, син — вместе, хронос — время). Асинхронные триггеры имеют только информационные (логические) входы, и в них запись информации осуществляется в момент ее поступления. В синхронных триггерах запись информации, поступившей на информационные входы, происходит только при поступлении на синхронизирующий (тактирующий) вход дополнительного командного импульса. Синхронные триггеры могут иметь и асинхронные входы, которые обычно служат для установки триггера в нужное исходное состояние.

Асинхронные триггеры используются в качестве коммутаторов, ключей, счетчиков импульсов, делителей частоты повторения импульсов и т. п. Синхронные триггеры применяются в вычислительной и цифровой технике.

Табл. 12.1. Функциональное назначение входов триггера

Работой триггеров можно управлять путем изменения уровней входных сигналов при достижении ими определенных порогов срабатывания, а также фронтами и срезами, возникающими при изменении этих уровней. Триггеры, переключающиеся по уровню входных сигналов, называют триггерами со статическим управлением, а по фронтам и срезам — триггерами с динамическим управлением.

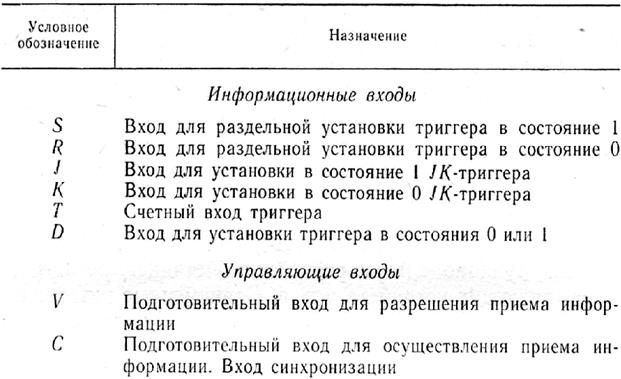

На схемах триггер изображают прямоугольником, разделенным вертикальной линией на две части (рис. 12.6): правая часть — основное поле, левая — дополнительное. В основном поле помещается буква Т, а в дополнительном у каждого входа пишется буква (метка), указывающая на его функциональное назначение в соответствии с табл. 12.1.Статические прямые входы и выходы отображают прямыми линиями без каких-либо индикаторов, а инверсные имеют дополнительный индикатор в виде маленького кружка на стороне прямоугольника (рис. 12.6, а). Динамические входы обозначают небольшими треугольниками.

Рис. 12.6. Условные обозначения триггеров

У прямых динамических входов, вызывающих «опрокидывание» триггера при изменении уровня сигнала от 0 к 1, острие треугольника направлено внутрь поля (рис. 12.6, б), а у инверсных, вызывающих опрокидывание триггера при изменении уровня сигнала от 1 до 0,— наружу (рис. 12.6, в).

У триггера может быть несколько информационных входов, связанных в группы операциями И либо ИЛИ. Группа входов, связанная операцией И, в дополнительном поле помечается символом логического умножения. Группа входов, связанная операцией логического сложения ИЛИ, дополнительных символов в условном обозначении не имеет (рис. 12.6, г).

12.4. RS-ТРИГЕРЫ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

RS-триггеры на логических элементах не содержат навесных деталей и обладают лучшими параметрами по сравнению с транзисторными триггерами на дискретных элементах.

Асинхронные RS-триггеры являются простейшими и выполняются на двух двухвходовых логических элементах типа И — НЕ либо ИЛИ — НЕ.

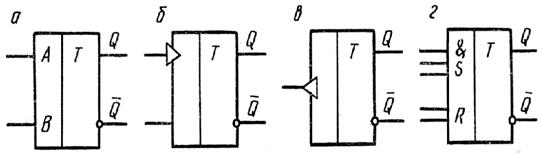

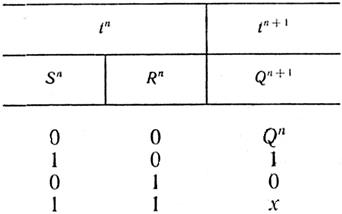

Асинхронные RS-триггеры на ЛЭ ИЛИ— НЕ.Асинхронный RS-триггер на двух логических элементах ИЛИ — НЕ (рис. 12.7, а) содержит два информационных входа R и S, на которых возможны четыре комбинации логических сигналов: Sn = Rn = 0; Sn = 1, Rn = 0; Sn = 0; Rn = 1 и Sn = Rn = 1. Этим комбинациям соответствуют

Рис. 12.7. Схема (а) и условное обозначение (б) асинхронного RS-триггера на

ЛЭ ИЛИ — НЕ с прямым управлением

определенные сигналы на выходах триггера Qи Q, что отображается так называемой таблицей состояний, триггера (табл. 12.2). В ней приняты следующие обозначения:

определенные сигналы на выходах триггера Qи Q, что отображается так называемой таблицей состояний, триггера (табл. 12.2). В ней приняты следующие обозначения:

Табл. 12.2. Состояние RS-тригера с прямым управлением

tn и tn+1 — моменты времени до и после срабатывания триггера; Sn и Rn — сигналы на информационных входах в момент tn; Qn и Qn+l — сигналы на прямом выходе в моменты времени tn и tn+1. Из таблицы состояний видно что первая комбинация входных сигналов Sn = Rn = 0 не вызывает изменения состояния триггера. Действительно, если к моменту времени tn состояние триггера характеризовалось сигналами Qn = 1, Qn = 0, то в момент tn на входах верхнего ЛЭ будут действовать нулевые сигналы, и на его выходе Qбудет логическая 1(Qn+1 = 1). В это же время на верхнем входе нижнего ЛЭ будет логическая 1, на нижнем входе S — логический 0, в результате чего на его выходе Q будет поддерживаться логический 0 (Qn+1 = 1). Аналогично можно показать, что при данной комбинации входных сигналов состояние триггера, соответствующее выходным сигналам Qn = 0 и Qn=l, также не изменится. По этой причине комбинацию входных сигналов Sn = Rn = 0 называют нейтральной или режимом памяти.

tn и tn+1 — моменты времени до и после срабатывания триггера; Sn и Rn — сигналы на информационных входах в момент tn; Qn и Qn+l — сигналы на прямом выходе в моменты времени tn и tn+1. Из таблицы состояний видно что первая комбинация входных сигналов Sn = Rn = 0 не вызывает изменения состояния триггера. Действительно, если к моменту времени tn состояние триггера характеризовалось сигналами Qn = 1, Qn = 0, то в момент tn на входах верхнего ЛЭ будут действовать нулевые сигналы, и на его выходе Qбудет логическая 1(Qn+1 = 1). В это же время на верхнем входе нижнего ЛЭ будет логическая 1, на нижнем входе S — логический 0, в результате чего на его выходе Q будет поддерживаться логический 0 (Qn+1 = 1). Аналогично можно показать, что при данной комбинации входных сигналов состояние триггера, соответствующее выходным сигналам Qn = 0 и Qn=l, также не изменится. По этой причине комбинацию входных сигналов Sn = Rn = 0 называют нейтральной или режимом памяти.

Комбинация входных сигналов Sn = 1, Rn = 0 переводит RS-триггер в единичное состояние: Qn+1 = l, Qn+1 = 0, если он перед этим находился в нулевом состоянии (Qn = 0, Qn = l). Если же RS-триггер в момент времени tn находился в единичном состоянии (Qn = 1, Qn = 0), то дадная комбинация подтверждает это состояние (Qn+1 = 1, Qn+1 =0). Поэтому вход S называют единичным входом: появление логической 1 на этом входе гарантирует наличие логической 1 на прямом выходе триггера независимо от его первоначального состояния.

Комбинация входных сигналов Sn = 1, Rn = 0 переводит RS-триггер в единичное состояние: Qn+1 = l, Qn+1 = 0, если он перед этим находился в нулевом состоянии (Qn = 0, Qn = l). Если же RS-триггер в момент времени tn находился в единичном состоянии (Qn = 1, Qn = 0), то дадная комбинация подтверждает это состояние (Qn+1 = 1, Qn+1 =0). Поэтому вход S называют единичным входом: появление логической 1 на этом входе гарантирует наличие логической 1 на прямом выходе триггера независимо от его первоначального состояния.

Комбинация входных сигналов Sn = 0, Rn = 1 обеспечивает нулевое состояние триггера. Действительно, если Qn = 1 и Qn = 0, то при поступлении сигналов Sn = 0 и Rn = 1 на одном входе верхнего ЛЭ появится логическая 1. Это вызовет появление на его выходе логического 0 (Qn+1 = 0), и на обоих входах нижнего ЛЭ будут логические нули, а на его выходе Qn+1 — логическая единица. Если же триггер находился в нулевом состоянии (Qn = 0, Qn = l), то комбинация входных сигналов Sn = 0, Rn = 1 состояние триггера не изменит, так как на обоих входах верхнего ЛЭ будут логические единицы, а нижнего ЛЭ — логические нули, подтверждающие выходные сигналы Qn+1 = 0, Qn+1 = 1. По этой причине вход R называют нулевым входом.

Комбинация входных сигналов Sn = 0, Rn = 1 обеспечивает нулевое состояние триггера. Действительно, если Qn = 1 и Qn = 0, то при поступлении сигналов Sn = 0 и Rn = 1 на одном входе верхнего ЛЭ появится логическая 1. Это вызовет появление на его выходе логического 0 (Qn+1 = 0), и на обоих входах нижнего ЛЭ будут логические нули, а на его выходе Qn+1 — логическая единица. Если же триггер находился в нулевом состоянии (Qn = 0, Qn = l), то комбинация входных сигналов Sn = 0, Rn = 1 состояние триггера не изменит, так как на обоих входах верхнего ЛЭ будут логические единицы, а нижнего ЛЭ — логические нули, подтверждающие выходные сигналы Qn+1 = 0, Qn+1 = 1. По этой причине вход R называют нулевым входом.

При комбинации входных сигналов Sn = Rn = 1 на обоих выходах триггера появятся логические нули (Qn+1 = 0, Qn+1 = 0). Если вслед за этим последует нейтральная комбинация входных сигналов (Sn = Rn = 0), то триггер с равной вероятностью примет единичное или нулевое состояние. Поэтому комбинацию входных сигналов Sn = Rn = 1 для рассматриваемого RS-триггера называют запрещенной и в таблице состояний отображают буквой x.

При комбинации входных сигналов Sn = Rn = 1 на обоих выходах триггера появятся логические нули (Qn+1 = 0, Qn+1 = 0). Если вслед за этим последует нейтральная комбинация входных сигналов (Sn = Rn = 0), то триггер с равной вероятностью примет единичное или нулевое состояние. Поэтому комбинацию входных сигналов Sn = Rn = 1 для рассматриваемого RS-триггера называют запрещенной и в таблице состояний отображают буквой x.

В рассмотренном триггере переключение состояний осуществляется единичными сигналами. Такой триггер называют триггером с прямым управлением и обозначают так, как показано на рис. 12.7, б.

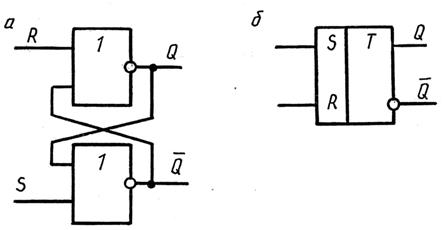

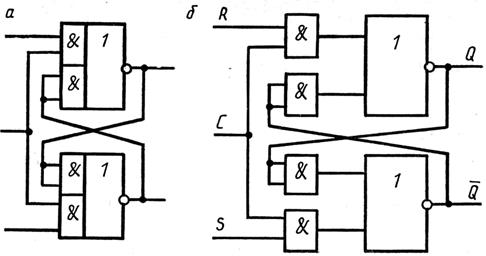

Асинхронные RS-триггеры на ЛЭ И— НЕ.Асинхронный RS-триггер можно выполнить и на двух двухвходовых ЛЭ И — НЕ (рис. 12.8, а).

В отличие от RS-триггера на ЛЭ ИЛИ — НЕ переключения данного триггера осуществляются сигналами логического 0. Такойтриггер называют триггером с инверсным управлением (RS-триггер). На функциональных схемах переключающие входы RS-триггера снабжаются индикаторами инверсии, а к буквенным обозначениям входов добавляются знаки отрицания (рис. 12.8, б).Состояния триггера в зависимости от комбинаций входных сигналов приведены в табл. 12.3.

Рис. 12.8. Схема (а) и условное обозначение (б) асинхронного RS-триггера на

логических элементах И — НЕ с инверсным управлением

Из таблицы состояний RS-триггера с инверсным управлением следует, что комбинация входных сигналов Sn = Rn = 1 является нейтральной, a Sn = Rn = 0 — запрещенной.

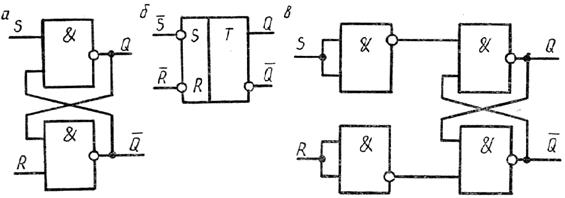

Табл. 12.3. Состояния RS-триггера с инверсным управлением

Табл. 12.3. Состояния RS-триггера с инверсным управлением

Если ко входам RS -триггера добавить два инвертора (рис. 12.8, в), то получится RS-триггер, подобный триггеру на элементах ИЛИ — НЕ. Асинхронные RS-триггеры используются в качестве ячеек памяти в оперативных запоминающих устройствах (ОЗУ) статического типа (например, ИМС К155РУ1).

Если ко входам RS -триггера добавить два инвертора (рис. 12.8, в), то получится RS-триггер, подобный триггеру на элементах ИЛИ — НЕ. Асинхронные RS-триггеры используются в качестве ячеек памяти в оперативных запоминающих устройствах (ОЗУ) статического типа (например, ИМС К155РУ1).

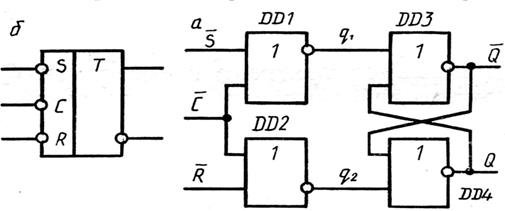

Синхронные RS-триггеры на ЛЭ И— НЕ.Асинхронные RS-триггеры легко преобразовать в синхронные, если подключить к их входам устройство управления, состоящее из логических элементов. На рис. 12.9, а приведена структурная схема синхронного RS-триггера со статическим управлением на ЛЭ И — НЕ. Собственно триггер выполнен на элементах DD3 и DD4, а элементы DD1 и DD2 образуют устройство управления. Кроме информационных входов S и R, устройство управления имеет синхронизирующий, или тактовый, вход С, связанный с входами S и R операциями И — НЕ. Поэтому информация с входов S и R передается на собственно триггер только при С = 1.

Собственно триггер управляется внутренними сигналами q1и q2. Переключения осуществляются нулевыми уровнями этих сигналов так же, как в триггере на рис. 12.8, а. Так как ЛЭ DD1 и DD2 осуществляют инверсию входных сигналов S и R,то нулевым уровням сигналов

Рис. 12.9. Схема (а) и условные обозначения (б; в) синхронного

RS-триггера на логических элементах И — НЕ

q1и q2должны соответствовать единичные уровни внешних информационных сигналов S и R.

Рассмотрим работу синхронного RS-триггера, приняв Qn = 0, Sn=1, Rn = 0. Если С = 0, то ЛЭ DD1 и DD2 закрыты и q1=q2=1. Такая комбинация внутренних сигналов q1и q2является нейтральной для собственно триггера, и он сохраняет свое состояние Qn = 0. Это состояние не изменяется при любых значениях информационных сигналов S и R. С приходом синхронизирующего импульса (С = = 1) на входах ЛЭ DD1 будет действовать логическая 1, вследствие чего q1 = 0 и Qn+1 = 1. Так как q2 = 1 (поскольку Rn = 0 и С = 1), то на входы ЛЭ DD4 поступят сигналы q2 = 1 и Qn+1 = 1 и образуют на его выходе сигнал Qn+1 = 0. Следовательно, триггер перешел в единичное состояние, которое будет сохраняться и после прекращения действия синхронизирующего импульса, так как при С = 0 для собственно триггера опять возникнет нейтральная комбинация q1 = q2 = 1.

Рассмотрим работу синхронного RS-триггера, приняв Qn = 0, Sn=1, Rn = 0. Если С = 0, то ЛЭ DD1 и DD2 закрыты и q1=q2=1. Такая комбинация внутренних сигналов q1и q2является нейтральной для собственно триггера, и он сохраняет свое состояние Qn = 0. Это состояние не изменяется при любых значениях информационных сигналов S и R. С приходом синхронизирующего импульса (С = = 1) на входах ЛЭ DD1 будет действовать логическая 1, вследствие чего q1 = 0 и Qn+1 = 1. Так как q2 = 1 (поскольку Rn = 0 и С = 1), то на входы ЛЭ DD4 поступят сигналы q2 = 1 и Qn+1 = 1 и образуют на его выходе сигнал Qn+1 = 0. Следовательно, триггер перешел в единичное состояние, которое будет сохраняться и после прекращения действия синхронизирующего импульса, так как при С = 0 для собственно триггера опять возникнет нейтральная комбинация q1 = q2 = 1.

Обратный переброс триггера в состояние Q = 0 произойдет в момент действия следующего синхронизирующего импульса при наличии на информационных входах сигналов Sn = 0 и Rn = 1. Комбинация входных сигналов Sn = Rn = 1 для рассмотренного триггера является недопустимой, так как при С=1 возникнет недопустимая комбинация q1 = q2 = 0, создающая неопределенное состояние на выходах триггера: Qn+1 = Qn+1 = 1.

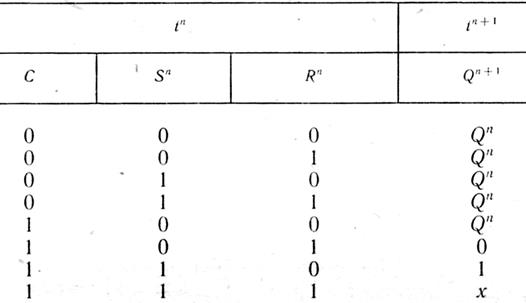

Условное обозначение рассмотренного синхронного RS-триггера с двумя информационными и одним синхронизирующим входами дано на рис. 12.9, б, а его состояния — в табл. 12.4.

Условное обозначение рассмотренного синхронного RS-триггера с двумя информационными и одним синхронизирующим входами дано на рис. 12.9, б, а его состояния — в табл. 12.4.

Если на дополнительные входы элементов DD3 и DD4 (на рис. 12.9, а они показаны пунктиром) подавать сигналы S и R,то можно осуществлять асинхронную установку триггера в состояния 0 и 1, минуя информационный и синхронизирующий входы. При этом функционирование триггера будет определяться состояниями, соответствующими состояниям триггера с инверсным управлением (см. табл. 12.3). Условное обозначение синхронного триггера с дополнительными входами, позволяющими осуществлять асинхронное управление его работой, показано на рис. 12.9, в.

Если на дополнительные входы элементов DD3 и DD4 (на рис. 12.9, а они показаны пунктиром) подавать сигналы S и R,то можно осуществлять асинхронную установку триггера в состояния 0 и 1, минуя информационный и синхронизирующий входы. При этом функционирование триггера будет определяться состояниями, соответствующими состояниям триггера с инверсным управлением (см. табл. 12.3). Условное обозначение синхронного триггера с дополнительными входами, позволяющими осуществлять асинхронное управление его работой, показано на рис. 12.9, в.

Табл. 12.4. Состояния синхронного RS-триггера с прямым управлением

При синхронной работе триггера на его дополнительных входах должна поддерживаться нейтральная комбинация S = R = 1.

При синхронной работе триггера на его дополнительных входах должна поддерживаться нейтральная комбинация S = R = 1.

Синхронные RS-триггеры на ЛЭ ИЛИ— НЕ.Синхронный RS-триггер можно построить и на ЛЭ ИЛИ — НЕ (рис. 12.10). Управление работой такого триггера осуществляется сигналами нулевого уровня Sn = 0 или Rn = 0

Синхронные RS-триггеры на ЛЭ ИЛИ— НЕ.Синхронный RS-триггер можно построить и на ЛЭ ИЛИ — НЕ (рис. 12.10). Управление работой такого триггера осуществляется сигналами нулевого уровня Sn = 0 или Rn = 0

Рис. 12.10. Схема (а) и условное обозначение (б) синхронного RS-триггера на

логических элементах ИЛИ — НЕ

при С = 0 в соответствии с табл. 12.3. Запрещенной комбинацией входных сигналов является комбинация Sn = Rn = 0 при Сn = 0. Действительно, в этом случае на обоих входах ЛЭ DD1 и DD2 действует логическая 1 (Sn = l, Сn = 1, Rn = 1) и q1 = q2 = 0. При этом на обоих выходах ЛЭ DD3 и DD4 будет логическая 1.

при С = 0 в соответствии с табл. 12.3. Запрещенной комбинацией входных сигналов является комбинация Sn = Rn = 0 при Сn = 0. Действительно, в этом случае на обоих входах ЛЭ DD1 и DD2 действует логическая 1 (Sn = l, Сn = 1, Rn = 1) и q1 = q2 = 0. При этом на обоих выходах ЛЭ DD3 и DD4 будет логическая 1.

В синхронных RS-триггерах изменения состояний при наличии разрешающего синхронизирующего импульса происходят так же, как и в асинхронных. Поэтому смена сигналов на информационных входах должна производиться только в паузах между синхронизирующими импульсами, чтобы не произошло нарушения его работы.

RS-тригтер на ЛЭ И — ИЛИ — НЕ. RS-триггер со статическим управлением можно выполнить на ЛЭ И — ИЛИ — НЕ (рис. 12.11, а).Принцип его работы не отличается от работы рассмотренных триггеров, в чем легко убедиться, представив его в виде, показанном на рис. 12.11. б.

Рис. 12.11. Структурная (а) и функциональная (б) схемы RS-триггера на

логических элементах И — ИЛИ — НЕ

Недостатком RS-триггеров является появление неопределенных состояний при образовании запрещенных комбинаций входных сигналов. Неопределенных состояний можно избежать, подключив ко входам триггера схему управления из ЛЭ. Работа схемы управления заключается в том, что при появлении на входе запрещенной комбинации сигналов состояние триггера принимает вполне определенное значение: единичное (S-триггер), нулевое (R-триггер), сохраняющее прежнее состояние (E-триггер) или меняющее состояние на противоположное (JK-триггер).

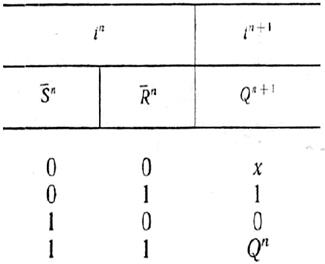

12.5. D-ТРИГТЕРЫ

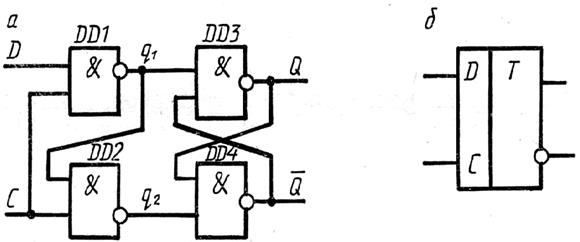

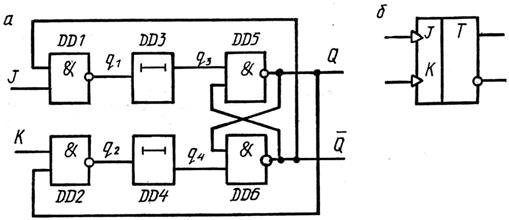

D-триггеры имеют один информационный вход D и могут быть асинхронными или синхронными. Наибольшее применение получили синхронные D-триггеры. Простейший синхронный D-триггер (рис. 12.12, а)выполнен на ЛЭ DD3 и DD4 типа И — НЕ по схеме RS-триггера и является ячейкой памяти. Логические элементы DD1 и DD2 образуют схему управления.

D-триггеры имеют один информационный вход D и могут быть асинхронными или синхронными. Наибольшее применение получили синхронные D-триггеры. Простейший синхронный D-триггер (рис. 12.12, а)выполнен на ЛЭ DD3 и DD4 типа И — НЕ по схеме RS-триггера и является ячейкой памяти. Логические элементы DD1 и DD2 образуют схему управления.

При отсутствии синхронизирующего импульса (С = 0) ЛЭ DD1 и DD2 закрыты, q1 = q2 = 1 и на выходе триггера поддерживается устойчивое состояние Qn = 1 или Qn = 0. При этом информация на входе D не изменяет состояние

Рис. 12.12. Схема (а) и условное обозначение (б) D-триггера на логических элементах И — НЕ

ЛЭ DD1 и DD2 и поэтому не влияет на состояние ячейки памяти.

Если с приходом синхронизирующего импульса С = 1, сигнал на информационном входе D отсутствует, т. е. Dn = 0, то ЛЭ DD1 закрыт и q1 = 1. На обоих входах ЛЭ DD2 будет действовать логическая 1 (С = 1, q1 = 1), он откроется (q2 = 0), что приведет к запиранию ЛЭ DD4 и отпиранию ЛЭ DD3. В результате на выходе ячейки памяти установится нулевое состояние (Qn+1 = 0, Qn+1= 1). Если же во время действия синхронизирующего импульса С = 1на вход D поступает логическая 1 (D = 1), то открывается ЛЭ DD1, на его выходе образуется логический 0 (q1= 0), а ЛЭ DD2 будет закрыт и q2 = 1. Под действием промежуточного сигнала q1= 0 ЛЭ DD3 запирается (Qn+1 = 1), а ЛЭ DD4 отпирается, так как на его входах действуют сигналы q2 = 1 и Qn+1 = l.

Если с приходом синхронизирующего импульса С = 1, сигнал на информационном входе D отсутствует, т. е. Dn = 0, то ЛЭ DD1 закрыт и q1 = 1. На обоих входах ЛЭ DD2 будет действовать логическая 1 (С = 1, q1 = 1), он откроется (q2 = 0), что приведет к запиранию ЛЭ DD4 и отпиранию ЛЭ DD3. В результате на выходе ячейки памяти установится нулевое состояние (Qn+1 = 0, Qn+1= 1). Если же во время действия синхронизирующего импульса С = 1на вход D поступает логическая 1 (D = 1), то открывается ЛЭ DD1, на его выходе образуется логический 0 (q1= 0), а ЛЭ DD2 будет закрыт и q2 = 1. Под действием промежуточного сигнала q1= 0 ЛЭ DD3 запирается (Qn+1 = 1), а ЛЭ DD4 отпирается, так как на его входах действуют сигналы q2 = 1 и Qn+1 = l.

Из вышеизложенного следует, что сигнал на выходе Q D-триггера принимает такое же значение, какое имеется на информационном входе D во время действия синхронизирующего импульса. Это значение хранится (запоминается) в триггере до прихода следующего синхронизирующего импульса, так как в паузах между синхронизирующими импульсами на входах ячейки памяти действует нейтральная комбинация сигналов q1 = q2 = 1. Следовательно, в D-триггере осуществляется задержка на один, такт сигнала, поступающего на информационный вход D. Поэтому D-триггер называют триггером задержки (от англ. delay — задержка, промедление).

В D-триггере вместо ЛЭ И — НЕ можно использовать ЛЭ ИЛИ — НЕ. В последнем случае для синхронизации потребуются импульсы нулевого уровня.

Если требуется задержка записанной информации более чем на один такт, применяют DV-триггер, отличающийся от D-триггера наличием дополнительного информационного входа V (от англ. valve — вентиль, клапан), как паказано на рис. 12.13, а. Когда V = 1, триггер работает как D-триггер. При V = 0 ЛЭ DD1 и DD2 закрыты при любых комбинациях сигналов на входах D и С,

Рис. 12..13. Схема (а), условное обозначение (б) DV-триггера и схема двухтактного триггера (в)

и в ячейке памяти хранится информация, записанная в предыдущем такте.

На рис. 12.13, в приведена схема однофазного двухтактного триггера на ЛЭ 2И — ИЛИ. Запись логической 1 в этом триггере осуществляется через ЛЭ И2 при одновременном действии сигналов на входах Т2 и D. После окончания действия сигналов Т2 и D (или одного из них) единичное состояние триггера удерживается логическим элементом И1, на входе которого действуют сигналы Q = 1 и T1 = 1 (T1=0). Установка триггера в состояние логического нуля осуществляется подачей на вход T1 логической 1 (при этом T1=0).

На рис. 12.13, в приведена схема однофазного двухтактного триггера на ЛЭ 2И — ИЛИ. Запись логической 1 в этом триггере осуществляется через ЛЭ И2 при одновременном действии сигналов на входах Т2 и D. После окончания действия сигналов Т2 и D (или одного из них) единичное состояние триггера удерживается логическим элементом И1, на входе которого действуют сигналы Q = 1 и T1 = 1 (T1=0). Установка триггера в состояние логического нуля осуществляется подачей на вход T1 логической 1 (при этом T1=0).

Как устройства запоминания двоичной информации D- и DV-триггеры применяются при построении регистров, счетчиков и других узлов цифровой техники.

12.6. JK-ТРИГГЕРЫ

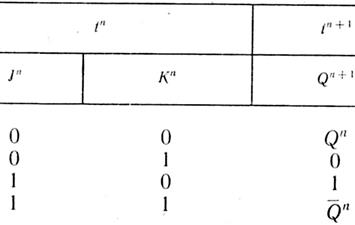

JK-триггер функционирует подобно RS-триггеру, с той лишь разницей, что не имеет запрещенной комбинации входных сигналов. Вход J выполняет роль входа S, а вход K — роль входа R. При входной комбинации Jn = Kn = 1, эквивалентной запрещенной комбинации Sn = Rn = 1 для RS-триггера, состояние JK-триггера изменяется на противоположное.

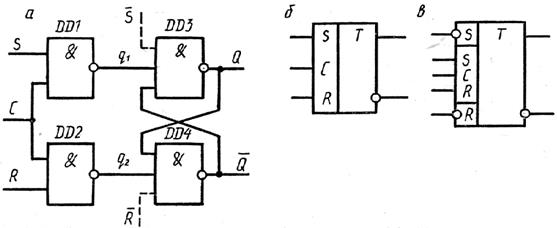

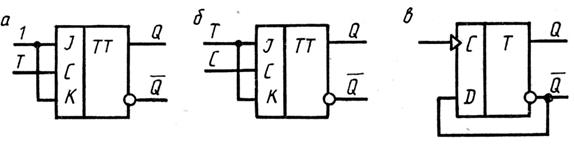

Одноступенчатый JK-триггер.Структурная схема JK-триггера показана на рис. 12.14, а. На ЛЭ DD5 и DD6 выполнена ячейка памяти,

Рис. 12.14. Схема (а) и условное обозначение (б) асинхронного JK-триггера

представляющая RS-триггер. Элементы DD1 и DD2 образуют схему управления, a DD3 и DD4 осуществляют задержку сигналов, поступающих на входы ячейки памяти. Особенностью JK-триггера является наличие цепей обратной связи с выходов на входы, поэтому его состояние зависит не только от входных сигналов J и K,но и от сигналов на выходах Qи Q.

представляющая RS-триггер. Элементы DD1 и DD2 образуют схему управления, a DD3 и DD4 осуществляют задержку сигналов, поступающих на входы ячейки памяти. Особенностью JK-триггера является наличие цепей обратной связи с выходов на входы, поэтому его состояние зависит не только от входных сигналов J и K,но и от сигналов на выходах Qи Q.

Если Jn = Kn = 0, то независимо от сигналов Qn и Qn на выходах ЛЭ DD1 и DD2 будет нейтральная комбинация q1 = q2 = 1, сохраняющая информацию в ячейке памяти. При Jn = 1 и Kn = 0по-прежнему промежуточный сигнал q2=1,а значение сигнала q1зависит от состояния ячейки памяти. Если Qn = 1 и Qn = 0, то на входе ЛЭ DD1 будут сигналы Jn=1, Qn = 0 и q1 = q3= 1. Состояние ячейки памяти не изменится. Если же Qn = 0, a Qn = 1, то q1 = q3 = 0, на выходе ЛЭ DD5 образуется сигнал Qn+l = 1, а на выходе ЛЭ DD6 — сигнал Qn+1 = 0. Аналогичным образом при Kn = 1 и Jn = 0 в ячейку памяти записывается логический нуль, если она находилась в состоянии логической единицы, или подтверждается ее нулевое состояние.

Если Jn = Kn = 0, то независимо от сигналов Qn и Qn на выходах ЛЭ DD1 и DD2 будет нейтральная комбинация q1 = q2 = 1, сохраняющая информацию в ячейке памяти. При Jn = 1 и Kn = 0по-прежнему промежуточный сигнал q2=1,а значение сигнала q1зависит от состояния ячейки памяти. Если Qn = 1 и Qn = 0, то на входе ЛЭ DD1 будут сигналы Jn=1, Qn = 0 и q1 = q3= 1. Состояние ячейки памяти не изменится. Если же Qn = 0, a Qn = 1, то q1 = q3 = 0, на выходе ЛЭ DD5 образуется сигнал Qn+l = 1, а на выходе ЛЭ DD6 — сигнал Qn+1 = 0. Аналогичным образом при Kn = 1 и Jn = 0 в ячейку памяти записывается логический нуль, если она находилась в состоянии логической единицы, или подтверждается ее нулевое состояние.

Пусть теперь Jn = Kn = 1 и Qn = l, a Qn = 0. Это приведет к установлению q2 = q4 = 0, в результате чего состояние ЛЭ DD6 изменится на значение Qn+1 = l и состояние ЛЭ DD5 — на значение Qn+1 = 0. При Jn = Kn = 1 и Qn = 0, Qn = l будет q1 = = q3 = 0, вследствие чего на выходе ЛЭ DD5 возникнет Qn+1 = 1, а на выходе ЛЭ DD6 — сигнал Qn+1 = 0. Таким образом, независимо от того, в каком состоянии находился JK-триггер при комбинации входных сигналов Jn = Kn = 1 происходит его переброс — изменение состояния на противоположное.

Пусть теперь Jn = Kn = 1 и Qn = l, a Qn = 0. Это приведет к установлению q2 = q4 = 0, в результате чего состояние ЛЭ DD6 изменится на значение Qn+1 = l и состояние ЛЭ DD5 — на значение Qn+1 = 0. При Jn = Kn = 1 и Qn = 0, Qn = l будет q1 = = q3 = 0, вследствие чего на выходе ЛЭ DD5 возникнет Qn+1 = 1, а на выходе ЛЭ DD6 — сигнал Qn+1 = 0. Таким образом, независимо от того, в каком состоянии находился JK-триггер при комбинации входных сигналов Jn = Kn = 1 происходит его переброс — изменение состояния на противоположное.

Элементы задержки DD3 и DD4 служат для задержки времени поступления сигналов ОС с выходов триггера на входы ЛЭ DD1 и DD2. Эти сигналы Qn+1 и Qn+1 поступают на ЛЭ DD1 и DD2 после окончания действия входных сигналов Jn и Kn, т. е. когда Jn+1 = Kn+1 = 0. Отсутствие элементов задержки вызвало бы многократное срабатывание триггера — генерацию. Сигналы J и K должны быть кратковременными, что достигается управлением работой ЛЭ DD1 и DD2 по фронту или срезу импульсов. Следовательно, в JK-триггере используется динамическое управление записью информации, что и подчеркивается в его условном изображении (рис. 12.14, б).

Состояния JK-триггера при различных значениях входных сигналов можно кратко отразить таблицей состояний (табл. 12.5).

Состояния JK-триггера при различных значениях входных сигналов можно кратко отразить таблицей состояний (табл. 12.5).

Табл. 12.5. Состояния JK-триггера

Рассмотренный асинхронный JK-триггер не применяется из-за сложности изготовления элементов задержки. Применяемые на практике JK-триггеры обычно выполняются по двухступенчатой схеме, или схеме MS (от анлг. master-slave, что означает ведущий-ведомый).

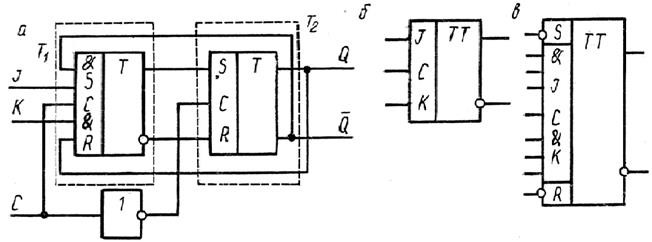

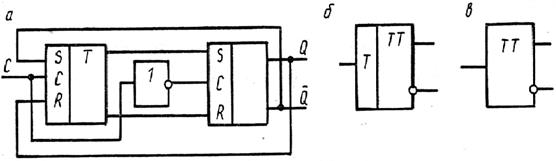

Двухступенчатый JK-триггер.В состав двухступенчатого JK-триггера (рис. 12.15, а)входят синхронный RS-триггер первой ступени T1 с логикой 2И на входе, синхронный триггер Т2 второй ступени и инвертор. Запись информации в первый триггер производится по сигналу С=1. После окончания сигнала на входе С (С = 0) информация с первого триггера переписывается во второй.

Рис. 12.15. Схема (а) и условные обозначения (б, в) двухступенчатого синхронного JK-триггера

Следовательно, задержка в перезаписи информации будет определяться в основном длительностью сигнала на входе С. В остальном работа двухступенчатого JK-триггера аналогична работе рассмотренного асинхронного / J K-триггера.

В JK-триггер можно ввести дополнительные входы S и R и с их помощью осуществлять асинхронную установку состояний триггера независимо от сигналов на входах J, K и С. Такой триггер называют комбинированным JK-триггером (рис. 12.15, в).

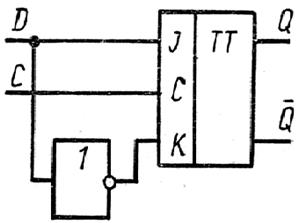

Если перед входом K JK-триггера поставить инвертор (рис. 12.16), то JK-триггер можно использовать как D-триггер. Допустим, D = 0 и С = 0, тогда J = = 0, K =1. Синхронизирующий импульс С = 1 переведет JK-триггер в состояние Q = 0, Q= 1.

Если перед входом K JK-триггера поставить инвертор (рис. 12.16), то JK-триггер можно использовать как D-триггер. Допустим, D = 0 и С = 0, тогда J = = 0, K =1. Синхронизирующий импульс С = 1 переведет JK-триггер в состояние Q = 0, Q= 1.

Рис. 12.16. Схема D-триггера, выполненного на синхронном JK-триггере

Если D = 1 (J = 1, K = 0), то после воздействия синхронизирующего импульса JK-триггер перейдет в состояние Q = 1, Q = 0.

Если D = 1 (J = 1, K = 0), то после воздействия синхронизирующего импульса JK-триггер перейдет в состояние Q = 1, Q = 0.

12.7. T-ТРИГГЕРЫ

T-триггер (от англ. toggle — кувыркаться) представляет собой триггер со счетным входом (или счетным запуском). Он изменяет свое состояние на притивопо-ложное при поступлении на вход Т каждого запускающего импульса.

Работа T-триггера на дискретных элементах рассмотрена в § 12.2 (рис. 12.3). В интегральном исполнении T-триггеры не выпускаются, так как они легко получаются из RS-, JК- или D-триггеров.

На рис. 12.17, а показано преобразование двухступенчатого RS-триггера в T-триггер. В те такты, когда

Рис. 12.17. Схема (а) и условные обозначения (б, в) T-триггера,

выполненного на синхронных RS-триггерах

Рис. 12.18. Условные обозначения T-триггеров, полученных из

JK-триггеров (а, б) и D-триггера с динамическим управлением (в)

JK-триггеров (а, б) и D-триггера с динамическим управлением (в)

Sn = Qn = 1 (при этом Rn = Qn = 0), синхронизирующий импульс С = 1 устанавливает первый триггер в единичное состояние. Это состояние переписывается во второй триггер после прекращения действия синхронизирующего импульса. На выходе триггера образуются сигналы Qn+1 = 1, Qn+1 = 0. При поступлении следующего синхронизирующего импульса первый триггер сигналом Rn+1 = Qn+1 = 1 устанавливается в нулевое состояние, которое записывается во второй триггер после окончания действия синхронизирующего импульса: Qn+2 = 0, Qn+2 = 1.

Sn = Qn = 1 (при этом Rn = Qn = 0), синхронизирующий импульс С = 1 устанавливает первый триггер в единичное состояние. Это состояние переписывается во второй триггер после прекращения действия синхронизирующего импульса. На выходе триггера образуются сигналы Qn+1 = 1, Qn+1 = 0. При поступлении следующего синхронизирующего импульса первый триггер сигналом Rn+1 = Qn+1 = 1 устанавливается в нулевое состояние, которое записывается во второй триггер после окончания действия синхронизирующего импульса: Qn+2 = 0, Qn+2 = 1.

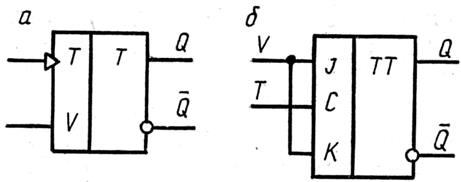

На рис. 12.18 показаны преобразования JK-триггера в асинхронный (а) и синхронный (б) T-триггеры, а также преобразование D-триггера с динамическим или двухступенчатым управлением записью в T-триггер.

Разновидностью счетного триггера является TV-триггер, который имеет дополнительный вход V (рис. 12.19, а). При V = 1 триггер работает как обычный T-триггер, а при V = 0 переключений триггера не происходит.

Рис. 12.19. Условные обозначения TV-триггеров

На рис. 12.19, б показано преобразование в TV-триггер JK-тригтера.

Асинхронные и синхронные Т- и TV-триггеры применяются в счетчиках и делителях частоты повторения импульсов.

Контрольные вопросы и задания

1.Дополните графики напряжений триггера с коллекторно-базовыми связями (рис. 12.1) графиками изменений напряжений на базах транзисторов VT1 и VT2.

2.Поясните принцип работы триггера с коллекторно-базовыми связями и одним (счетным) входом (рис. 12.3).

3. Изобразите схемы асинхронных RS-триггеров на ЛЭ ИЛИ — НЕ и И — НЕ. Каковы отличительные особенности работы этих триггеров?

4.Поясните работу синхронного RS-триггера на ЛЭ И — НЕ (рис. 12.9, а). Какая комбинация сигналов на входах R и S является запрещенной для этого триггера и почему?

5.

Почему комбинация сигналов S = R = С = 0 для синхронного RS-триггера на ЛЭ ИЛИ — НЕ (рис. 12.10) является запрещенной?

Почему комбинация сигналов S = R = С = 0 для синхронного RS-триггера на ЛЭ ИЛИ — НЕ (рис. 12.10) является запрещенной?

6.Изобразите схему простейшего синхронного D-триггера на ЛЭ И — НЕ и поясните его работу.

7.В чем особенности работы DV-триггера по сравнению с D-триггером?

8.Поясните, как работает JK-триггер, изображенный на рис.12.14, а.

9.Какую функцию выполняет ЛЭ НЕ в триггере, изображенном на рис. 12.17, а?

Глава 13. ЦИФРОВЫЕ И КОМБИНАЦИОННЫЕ

ЭЛЕКТРОННЫЕ УСТРОЙСТВА