Аппаратные методы ускорения умножения

Использование дополнительных сумматоров для распараллеливания процесса вычисления суммы частичных произведений.

С:=А*В

В=b1b2b3…bm bm+1bn

B1=(b1b2…bm)*2m

B2=(bn+1bm+2…bn)

m=n/2

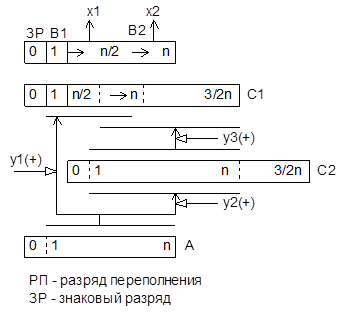

C=AB1+AB2

Произведения AB1 и AB2 представляются 3/2 n – разрядными кодами и вычисляются параллельно на сумматорах С1 иС2( например с использованием базового алгоритма умножения). После этого производится объединяющее сложение, в результате чего определяется 2n – разрядное произведение.

Пример:

А В

01101*0111

+ + +

+ + +

В1 0 11 0 11 0 01 0 01 0 00 0 00

В1 0 11 0 11 0 01 0 01 0 00 0 00

В2 11 11 01 01 00 00

С1 0 000000 0 110100 0 011010 1 001110 0 100111 0 110000

С2 0 000000 0 110100 0 011010 1 001110 0 100111 0 110111

А 0 1101 0 1101 0 1101 0 1101 0 1101 0 1101

Cч 0 0 1 1 0 0

+

100111

13/16*15/16=195/256

12/16+3/256=195/256

результат: 0 11000011

Способы управления вычисления сумм частичных произведений:

- Синхронный метод

Множитель находится в едином регистре В, управление осуществляется одним УА, умножение производится одновременно на разряды n и n/2 множителя. Такт суммирования пропускается, если только разряды множителя n и n/2 равны 0, иначе сложение выполняется хотя бы на одном сумматоре. В такте сдвига УА вырабатывает сигнал микрооперации сдвига в обоих сумматорах и регистре В (обе части регистра В сдвигаются одновременно).

tумн.ср=.n/2(3/4Тумн.+Тсдв.)+Тсум.

n n/2

0 0 - такт сложения пропускается

0 1

1 0

1 1