Интегральные запоминающие устройства

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими частями вычислительной машины (системы).

В составе ЗУ можно выделить запоминающую среду, средства для записи и считывания данных, средства управления, синхронизирующие работу ЗУ.

Емкость ЗУ определяется максимально возможным объемом хранимой им информации. Минимальный объем информации (один бит) хранится запоминающим элементом (ЗЭ). Емкость ЗУ выражают в битах или в количестве слов с указанием их разрядности.

Организация ЗУ – указывает на количество и разрядность хранимых слов. Например ЗУ: 32х8 бит означает ЗУ 256 бит (хранится 32 слова по 8 разрядов).

Быстродействие ЗУ: определяется временем считывания, записи и обращения.

Время считывания – отрезок времени, между появлением сигнала считывания и моментом появления слова на выходе.

Время записи – время от момента появления сигнала записи до ее завершения, после которого ЗУ может выполнять новую операцию.

Обращение к ЗУ – операция считывания или записи информации. Время обращения – интервал между двумя последовательными обращениями к ЗУ.

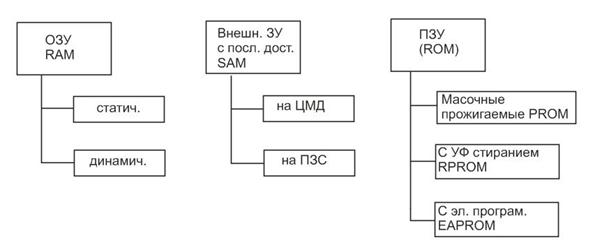

По способу записи и считывания ЗУ можно классифицировать:

Масочные и прожигаемые ЗУ.

Содержат информацию, которая не может быть изменена. Масочные ЗУ подвергаются операции записи информации на этапе изготовления ИМС с помощью специального шаблона (маски), а прожигаемые программируются после изготовления на специальной аппаратуре, что может быть выполнено и пользователем. При большой тиражности изготовляемых ЗУ предпочтительно масочное программирование, при малой – с помощью прожигания тех или иных перемычек между элементами схемы.

В обоих видах ЗУ нет ограничений на время хранения и на число считываний.

Запоминание бита информации в обоих видах ЗУ сводится к наличию или отсутствию некоторого элемента связи между выбранной адресной шиной и шиной считывания.

Элементом связи может быть диод, БТ, МОП – транзистор и так далее. Как правило, информация читается из ЗУ многоразрядными словами.

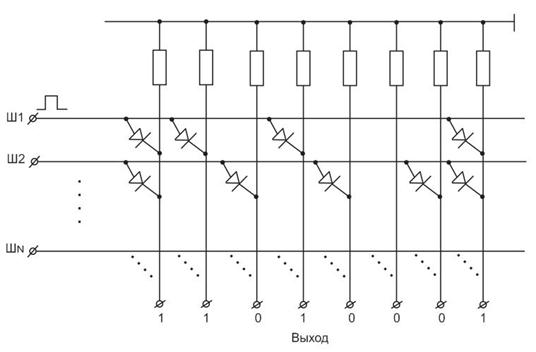

Пример фрагмента матрицы интегрального ПЗУ с диодами:

Горизонтальные шины являются шинами выборки, а вертикальные используются для считывания выходного слова.

При наличии диода высокий уровень потенциала, появляющийся на выбранной горизонтальной шине, передается на соответствующую вертикальную шину, и в данном разряде слова появляется сигнал логической единицы. При отсутствии диода потенциал вертикальной шины остается нулевым.

В показанном на рисунке фрагменте матрицы ЗУ при подаче потенциала логической “1” на шину выборки Ш1 считывается слово 11010001 (№1), а при выборке шины Ш2 – 10101011 (оно хранится в ячейке №2).

В масочных ЗУ программирование ПЗУ состоит в изготовлении или не изготовлении элемента связи в том или ином узле координатной сетки.

Чтобы удешевить производство при переходе от выпуска одного масочного (шаблонного) ЗУ к другому, варьируют только один фотошаблон из всех применяемых при изготовлении ЗУ.

Благодаря простоте устройства масочные БИС запоминающих кристаллов имеют весьма большую степень интеграции.

В прожигаемых ЗУ запись данных в матрицу запоминающих элементов выполняет пользователь. Сами запоминающие элементы могут быть резисторными, диодными или транзисторными.

Резисторные ЗЭ изготовляются в виде пленки из тугоплавкого металла или поликристаллического кремния. Такой элемент хранит логическую единицу, а логический ноль нужно записать, сжигая пленку, пропустив через нее импульс тока, намного превышающий уровень токов считывания. В режиме считывания ЗЭ опрашивают, подавая на него импульс напряжения и оценивая величину тока. При хранении нуля ток равен нулю, а при хранении единицы ток возникает.

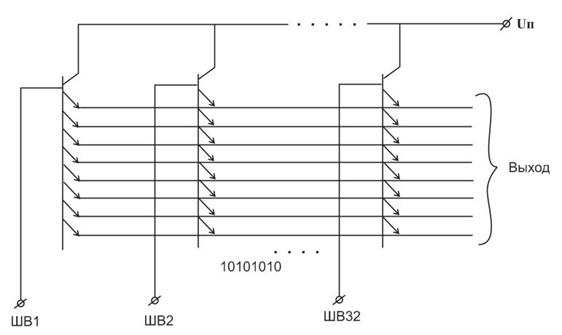

Вариант прожигаемого ЗУ, соответствующего РЕ1, РЕ3 (155 серия):

На рисунке показан накопитель ПЗУ 256 бит, 32-8 разрядных слова (формат может быть различным).

Накопитель ПЗУ на рисунке содержит 32 транзистора с 9 эмиттерами в каждом (8 рабочих и 1 технологический для режима прожигания – на рисунке не показан).

При подаче высокого потенциала логической единицы на адресную шину выборки ШВ соответствующий многоэмиттерный транзистор работает в режиме повторителя и выдает высокий потенциал на все выходные шины.

До записи информации такое ПЗУ по любому адресу выдает слово, состоящее из одних единиц. Для записи в ПЗУ нужных данных исключаются связи между эмиттерами транзисторов и горизонтальными выходными шинами.

В связи между каждым эмиттером и горизонтальной шиной предусмотрена плавкая перемычка, которую можно прожечь током определенной амплитуды и длительности. Отсутствие связи эмиттера с выходной шиной дает ноль в соответствующем разряде выходного слова.

Выходные шины накопителя управляют выходными усилителями – инверторами, через которые сигналы передаются на внешнюю нагрузку.

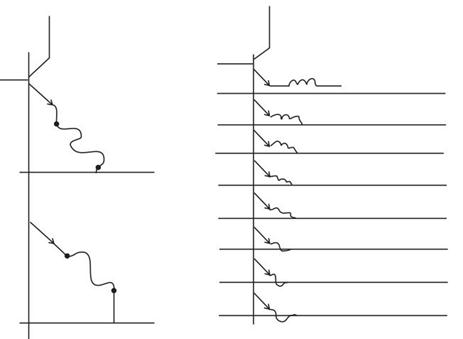

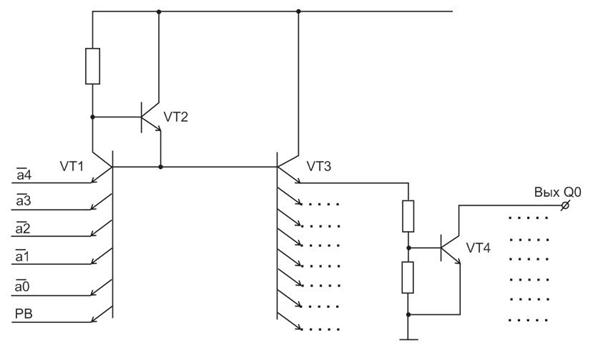

ПЗУ кроме накопителя содержит дешифратор адреса. В нашем случае на его вход подается пяти разрядный код адреса А (для адресации 32 слов). Адрес определяет номер возбужденной шины накопителя (на входе). Схемотехническая реализация одной из 32х8 цепей ПЗУ показана на рисунке:

Левый транзистор  принадлежит дешифратору. Только один из всех (в данном случае 32) наборов создает совпадение единиц по входу (на рисунке 00010).

принадлежит дешифратору. Только один из всех (в данном случае 32) наборов создает совпадение единиц по входу (на рисунке 00010).

Это запирает входной транзистор, если единичное значение сигнала  разрешает ему функционировать (нулевое значение

разрешает ему функционировать (нулевое значение  блокирует работу – входной транзистор насыщается).

блокирует работу – входной транзистор насыщается).

Если  и

и  = 1 входной транзистор запирается и высокий потенциал с его коллектора через эмиттерный повторитель на

= 1 входной транзистор запирается и высокий потенциал с его коллектора через эмиттерный повторитель на  передается на соответствующую входную шину накопителя для считывания выбранного слова.

передается на соответствующую входную шину накопителя для считывания выбранного слова.

После выходного усилителя считывается инвертированное слово, поэтому с учетом инверсии программирование ПЗУ подчинено правилу:

- где оставлена перемычка в эмиттере – формируется «0»;

- где отсутствует перемычка – «1».