Элементы эмиттерно-связанной логики

В настоящее время наиболее быстродействующими элементами, изготовляемыми на основе кремния, являются элементы транзисторной логики с эмиттерными связями (ТЛЭС элементы, либо ЭСЛ), построенные на токовых переключателях.

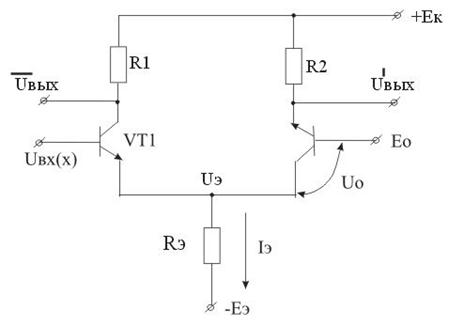

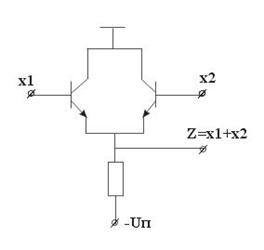

В элементах ЭСЛ используется токовый ключ (или переключатель тока):

Схема представляет собой дифференциальный усилитель, оба транзистора которого работают в режиме, близком к линейному. База транзистора VT1 является входом переключателя, база же VT2 подключена к источнику опорного напряжения Е0.

Сопротивление RЭ в цепи эмиттеров транзисторов VT1 и VT2 вместе с источником питания образуют генератор тока.

Выходные сигналы  и

и  снимаются с нагрузок, включенных в коллекторных цепях обоих транзисторов.

снимаются с нагрузок, включенных в коллекторных цепях обоих транзисторов.

Принцип действия переключателя состоит в следующем:

При подаче на вход достаточно малого (несколько десятых долей вольта) положительного относительно опорного потенциала Е0 опорного напряжения  транзистор VT1 откроется, потенциал UЭ возрастет. Напряжение U0 упадет и транзистор VT2 закроется, так что весь ток генератора IЭ будет протекать через транзистор VT1 и нагрузку R1.

транзистор VT1 откроется, потенциал UЭ возрастет. Напряжение U0 упадет и транзистор VT2 закроется, так что весь ток генератора IЭ будет протекать через транзистор VT1 и нагрузку R1.

При подаче на вход столь же малого отрицательного относительно Е0 напряжения  транзистор VT2 откроется, весь ток IЭ переключится в нагрузку R2 транзистора VT2.

транзистор VT2 откроется, весь ток IЭ переключится в нагрузку R2 транзистора VT2.

Напряжение на основном выходе (снимается с R2 ) в первом случае близко к ЕК, что соответствует логической единице (  ) , а во втором – несколько превышает величину Е0 (

) , а во втором – несколько превышает величину Е0 (  ). Таким образом, логические значения на основном выходе равны входным; ясно, что с R1снимаются инверсные значения выходных сигналов.

). Таким образом, логические значения на основном выходе равны входным; ясно, что с R1снимаются инверсные значения выходных сигналов.

Быстродействие токового ключа весьма велико, так как транзисторы в нем работают в режимах, позволяющих максимально использовать их частотные возможности: отсутствует режим насыщения, перепады напряжений при изменении логического состояния цепи малы, поэтому могут быть малыми и сопротивления RК (что уменьшает постоянную времени перезаряда нагрузочных емкостей).

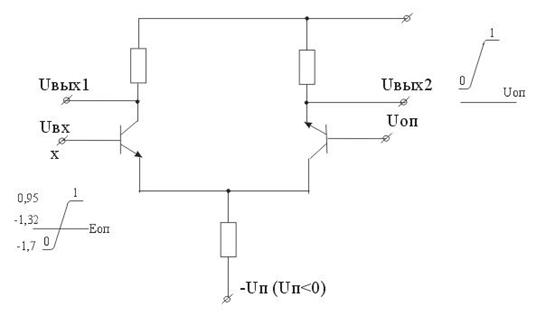

Обычно питание схем ЭСЛ осуществляют, как показано на рисунке:

Так, схемы ЭСЛ на n-p-n транзисторах питаются, как показано на рисунке от источника отрицательного напряжения. По абсолютным значениям уровни выходных сигналов, как уже указывалось, отличаются смещением в сторону «плюса» (без этого нельзя осуществить ненасыщенный режим работы транзисторов).

Для нормальной работы последовательно соединенных схем необходимо, чтобы уровни выходных сигналов предыдущего каскада были согласованы с уровнями входных сигналов последующих каскадов. Следовательно, невозможно последовательное каскадирование рассмотренных схем – входной сигнал следующего за первым токового ключа уже не будет симметричным относительного опорного.

Одним из способов согласования уровней является чередование каскадов на n-p-n и p-n-p транзисторах, однако при интегральном исполнении это привело бы к значительному усложнению технологии их изготовления.

Более эффективным является использование дополнительных элементов, смещающих уровни сигналов.

В таком качестве используются эмиттерные повторители, напряжение на выходе которых повторяет входное, но смещено относительно него на относительно постоянное напряжение база-эмиттер (UБЭ составляет около 0,7В).

Одновременно с этим ЭП обеспечивает малые выходные сопротивления, позволяющие быстро перезаряжать нагрузочные элементы.

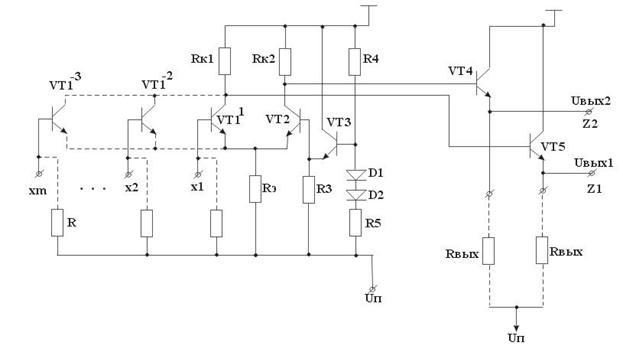

Базовый логический элемент ЭСЛ образуется при замене входного транзистора токового ключа группой параллельно включенных транзисторов. Схема такого элемента (с особенностями серии 500).

Источником опорного напряжения  служит схема, представляющая собой эмиттерный повторитель на транзисторе VT3. Напряжение с R3 подается на базу VT2. напряжение на базу ЭП (VT3) подается с делителя напряжения R4-R5, причем последовательно с R5 включены диоды D1, D2. Диоды обеспечивают температурную компенсацию уходов параметров схемы.

служит схема, представляющая собой эмиттерный повторитель на транзисторе VT3. Напряжение с R3 подается на базу VT2. напряжение на базу ЭП (VT3) подается с делителя напряжения R4-R5, причем последовательно с R5 включены диоды D1, D2. Диоды обеспечивают температурную компенсацию уходов параметров схемы.

В сложных ИМС источник  может питать несколько аналогичных схем, выполненных на одном кристалле.

может питать несколько аналогичных схем, выполненных на одном кристалле.

Транзисторы выходных ЭП (VT4, VT5) также работают только на линейном участке, что обеспечивает повышенное быстродействие элемента.

Сопротивления, входящие в схемы выходных ЭП (VT4, VT5) сделаны внешними. Это выполняется с целью уменьшения мощности, рассеиваемой в корпусе микросхемы и с другой стороны, чтобы иметь разные варианты реализации выходных цепей. При обычной нагрузке сопротивление  включается между эмиттером выходного транзистора и стандартным источником питания (примерно –5В (-5,2В)), а при передаче сигнала по согласованным по волновому сопротивлению линиям, когда требуется малое выходное сопротивление схемы, сопротивление берется

включается между эмиттером выходного транзистора и стандартным источником питания (примерно –5В (-5,2В)), а при передаче сигнала по согласованным по волновому сопротивлению линиям, когда требуется малое выходное сопротивление схемы, сопротивление берется  , а чтобы не создавался недопустимо большой ток выходного повторителя, это сопротивление подключается к пониженному напряжению.

, а чтобы не создавался недопустимо большой ток выходного повторителя, это сопротивление подключается к пониженному напряжению.

Цепи общей точки для логической схемы и выходных ЭП выполняются раздельными (чтобы избежать помех из цепей питания последних).

Входы схемы соединяют высокоомными (  )резисторами с источником питания, что позволяет не подключать неиспользуемые входы элемента к каким-либо внешним потенциалам. На элементы ИЛИ-НЕ и ИЛИ на используемые входы нужно подавать логические нули, их роль и играет соединение источника питания с отрицательным потенциалом. Если данный вход используется, то влияние на его режим резистора R очень мало из-за высокоомности резистора.

)резисторами с источником питания, что позволяет не подключать неиспользуемые входы элемента к каким-либо внешним потенциалам. На элементы ИЛИ-НЕ и ИЛИ на используемые входы нужно подавать логические нули, их роль и играет соединение источника питания с отрицательным потенциалом. Если данный вход используется, то влияние на его режим резистора R очень мало из-за высокоомности резистора.

Базовый элемент работает следующим образом:

Если хотя бы на одном входе имеется логическая единица, то есть высокий уровень напряжения, то соответствующий транзистор открывается и ток  замыкается через

замыкается через  снижая уровень напряжения на выходе

снижая уровень напряжения на выходе  . Если же на всех входах будут логические нули, то откроется транзистор VT2 правой ветви, что одновременно приведет к запиранию всех транзисторов левой ветви и повышению напряжения

. Если же на всех входах будут логические нули, то откроется транзистор VT2 правой ветви, что одновременно приведет к запиранию всех транзисторов левой ветви и повышению напряжения  . Из сказанного ясно, что

. Из сказанного ясно, что

Так как сигналы на выходах  и

и  всегда противофазны:

всегда противофазны:

Поскольку выполняются одновременно операции ИЛИ-НЕ и ИЛИ, элемент обладает повышенной функциональной гибкостью.

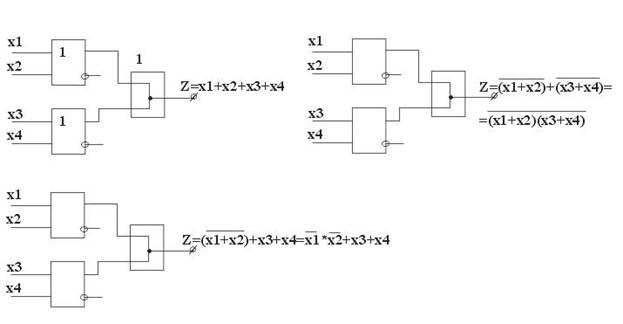

Более сложные логические операции могут выполняться либо с помощью соответствующего соединения базовых элементов, либо с использованием специальных приемов.

Один из приемов состоит в объединении нескольких выходов:

При параллельной работе нескольких ЭП (на рис. - два) на выход схемы проходит максимальный из входных сигналов, запирая одновременно те транзисторы, на базах которых действует более низкий потенциал. Для получения логической единицы достаточно одной логической единицы на входах. При подаче на входы только нулевых сигналов все транзисторы находятся в одинаковых режимах и совместно работают на общую нагрузку, создавая в ней низкий уровень логического нуля. Таким образом, объединение эмиттеров дает дополнительную монтажную реализацию операции ИЛИ.

Различные варианты объединения выходов логических элементов позволяют реализовать логические операции, показанные на рисунке:

Важным свойством элементов с переключением токов является зависимость выходного перепада напряжения от отношения  , а не от абсолютных значений сопротивлений резисторов

, а не от абсолютных значений сопротивлений резисторов  и

и  . Это свойство соответствует интегральной технологии, при которой легче обеспечить малый допуск (

. Это свойство соответствует интегральной технологии, при которой легче обеспечить малый допуск (  ) на отношение сопротивлений, чем на их абсолютные значения (погрешность

) на отношение сопротивлений, чем на их абсолютные значения (погрешность  ).

).

При выполнении логических операций в ЭСЛ – элементе происходит переключение одного и того же тока  из одной цепи переключателя в другую. Поэтому общее потребление тока в цепи питания практически не изменяется. Что определяет малый уровень помех на шине питания. Уровень помех в линиях связи так же невысок за счет низкого выходного сопротивления схемы.

из одной цепи переключателя в другую. Поэтому общее потребление тока в цепи питания практически не изменяется. Что определяет малый уровень помех на шине питания. Уровень помех в линиях связи так же невысок за счет низкого выходного сопротивления схемы.

Недостаток – относительно большая потребляемая мощность (токовая нагрузка элемента постоянна). К недостаткам относится также весьма высокая чувствительность схемы к изменению величины питающего напряжения.

Типовые характеристики элементов ЭСЛ и их модификаций: задержка распространения,  , коэффициент объединения по выходу ~5, разветвления по выходу ~

, коэффициент объединения по выходу ~5, разветвления по выходу ~  , перепад напряжения на выходе

, перепад напряжения на выходе  , помехоустойчивость

, помехоустойчивость  . Потребляемая мощность 25-100мВт.

. Потребляемая мощность 25-100мВт.