По предмету «Вычислительная техника и информационные технологии»

Лабораторные работы

По предмету «Вычислительная техника и информационные технологии»

Выполнили:

Группа АТз-11у

Проверил: Гаврилов А.В.

Пермь 2013 г.

Лабораторная работа №1

ИЗУЧЕНИЕ ЦИФРОВОЙ СХЕМОТЕХНИКИ С

ИСПОЛЬЗОВАНИЕМ САПР MAX+PLUSII

Проектирование комбинационных схем, программирование ПЛИС и

анализ размещения схемы на кристалле

Лабораторная работа №3: «Проектирование комбинационных схем, программирование ПЛИС и анализ размещения схемы на кристалле»

Цель работы: освоение проектирования комбинационных схем с привлечением платы лабораторного стенда, анализ размещения схемы устройства на кристалле с использованием ре-дактора конфигурации БИС системы MAX+plusII.

ВВЕДЕНИЕ

Комбинационными называются цифровые устройства, логическое состояние которых за-висит только от комбинации логических сигналов, поступающих на их входы в настоящиймо-мент времени. К этому классу устройств относятся такие широко распространенные функцио-нальные узлы цифровых систем, как преобразователи кодов, шифраторы и дешифраторы, муль-типлексоры и демультиплексоры, компараторы, сумматоры, арифметико-логические устройства (АЛУ), умножители и ряд других.

Функциональное описание комбинационного устройства задается в виде таблицы истин-ности, алгебраического выражения или описания на специализированном языке высокого уров-ня(VHDL, AHDL, Verilog HDL и другие).

В настоящее время для реализации комбинационных устройств используются два возможных способа.

1. Сборка устройства из набора отдельных логических элементов (И-НЕ, ИЛИ-НЕ и дру-гих). Этот способ применяется при разработке относительно несложных устройств, реализуе-мых на серийно выпускаемых микросхемах малой степени интеграции, или при проектировании комбинационных блоков в составе сложнофункциональных устройств, реализуемых в виде за-казных или полузаказных БИС, которые разрабатываются с использованием библиотек логиче-ских элементов.

2. Создание устройства на базе программируемых логических интегральных схем (ПЛИС), в которых заданная логическая функция реализуется путем соответствующего про-граммирования и соединения универсальных логических элементов и блоков, составляющих внутреннюю структуру ПЛИС.

Традиционные методы проектирования комбинационных устройств, ориентированные на первый способ их реализации, описаны в ряде учебных пособий. В данной лабораторной работе описывается методика проектирования цифровых устройств на базе ПЛИС, выпускаемых ком-паниейAltera, с помощью системы MAX+plusII.

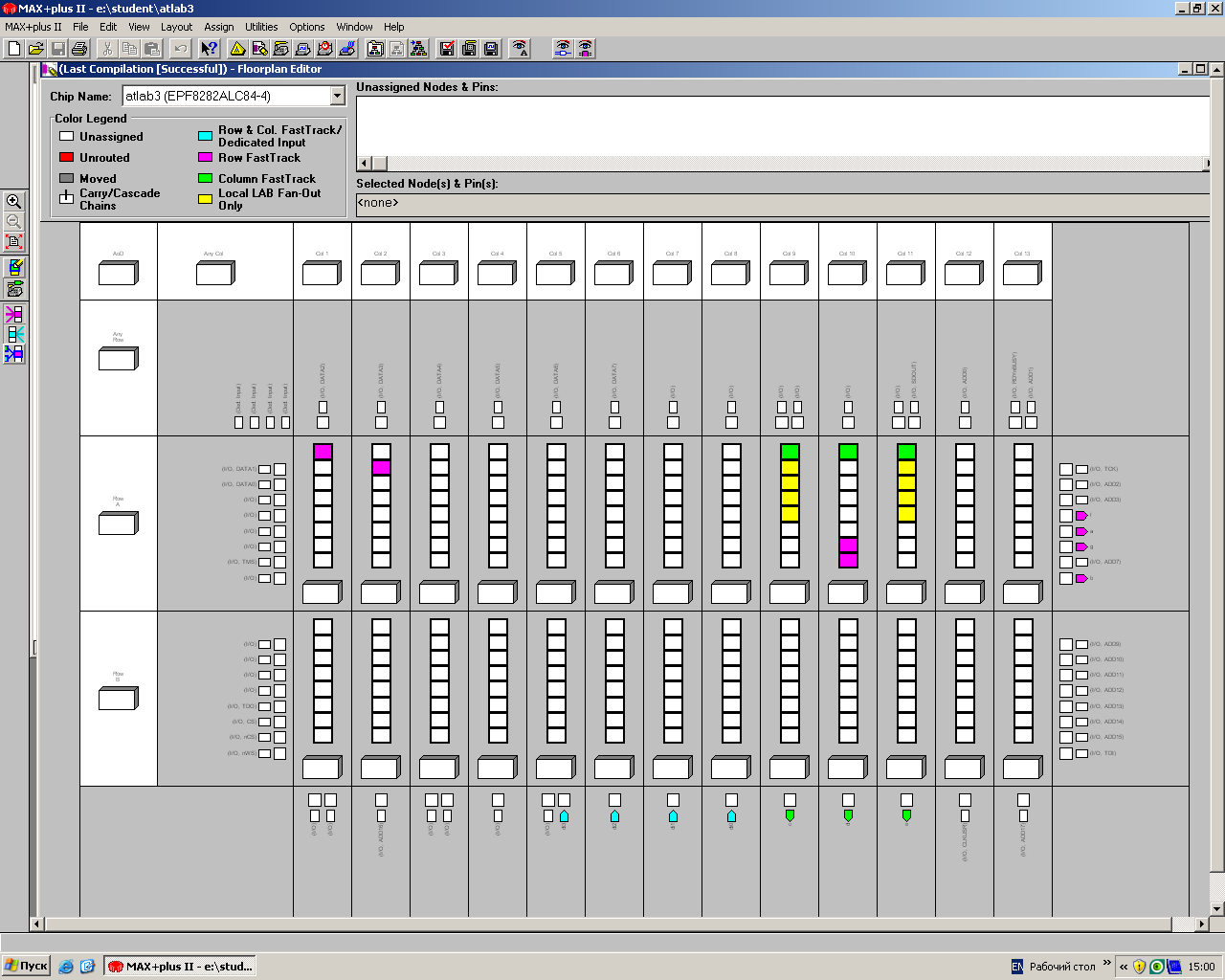

Система MAX+plusIIпредоставляет возможность анализа размещения схемы устройства на кристалле с использованием редактора конфигурации БИС. Редактор конфигурации форми-рует две разновидности изображения ПЛИС - DeviceViewи LAB View. Первое изображение представляет корпус микросхемы с указанием всех выводов, их номеров и функций. Второе представляет внутреннюю структуру ПЛИС в виде совокупности блоков ячеек (LABs- logicarrayblocks), отдельные ячейки внутри блоков, ячейки ввода-вывода. Этот тип изображения также включает информацию о выводах, поэтому можно проследить связи между ними и внутренними ячейками микросхемы.

ОПИСАНИЕ ЗАДАЧИ

В данной работе рассмотрим дешифратор для семисегментного индикатора, который, в зависимости от комбинации сигналов на 4 входных линиях, формирует код выборки сегментов на семи выходных линиях. Активным значением сигнала на выходной линии (при котором за-жигается сегмент) является уровень "1".

ПОСЛЕДОВАТЕЛЬНОСТЬ РЕШЕНИЯ ЗАДАЧИ

Рис. 1 Изображение конфигурации ПЛИС типа DeviceView

Изображение типа LAB View, приведено на Рис. 2.

Из рисунка видно, что при наведении указателя на вывод, рядом с указателем в рамке отображается имя линии проекта и номер вывода микросхемы. Редактор конфигурации позво-ляет получить информацию о связях отмеченных логических ячеек и выводов. Это делается следующим образом:

1. Выберем опцию ShowNodeFan-In("входные цепи") и/или опцию ShowNodeFan-Out("выходные цепи") в меню Option.

2. Установим режим LAB Viewи отметим одну или более логических ячеек или выво-дов.

Редактор отобразит входные и выходные цепи отмеченных элементов. На Рис. 6 отобра-жены связи третьей логической ячейки ряда А, столбца 2. Редактор конфигурации позволяет просматривать и изменять текущие назначения, которые хранятся в файле project'sAssigment&ConfigurationFile(.acf). После трансляции проекта можно вручную редактировать назначения, сделанные компилятором и хранящиеся в файле project'sFitFile(.fit). Для этого существует опция Back-AnnotateProjectв меню Assign, которая осуществляет копирование назначений из файла .fitв файл .acf.

Рис 2. Изображение конфигурации ПЛИС типа LAB View

Процесс корректировки назначений проекта с использованием редактора конфигурации следующий:

1. ВыберемкомандуменюAssign | Back-Annotate Project.

2. В открывшемся диалоговом окне включим опцию Chips, Logic Cells, Pins&DevicesразделаBack-Annotate to ACF. После ввода OK будет проведено копирование назначений из файла .fitв файл .acf.

3. ВведемкомандуменюLayout | Current Assignments Floorplan. Редактор конфигурации отобразит текущие назначения проекта.

4. Выберем опцию ShowNodeFan-In("входные цепи") и/или опцию Show Node Fan-Out ("выходныецепи") менюOption.

5. Введем команду поиска, выбрав пункт меню Utilities | FindText, в диалоговом окне выключим опцию Аllи включим опцию Pin&NodeNames. Укажем слово для поиска di0 и за-вершим ОК. В окне редактора конфигурации будет отмечен назначенный этому имени вывод и указаны его связи.

6. Введем команду меню Option | ShowMovedNodesinGray, которая отмечает серым цветом новые назначения.

7. Переведем редактор в режим просмотра текущих назначений, для чего нужно нажать на кнопку в левой вертикальной панели инструментов.

8. Наведем указатель мыши на отмеченный вывод линии di0 и при нажатой левой кнопке мыши «перетащим» назначение с вывода 45 на вывод 37. Аналогично переназначим линию di1 с вывода 44 на вывод 39, линию di2 с вывода 43 на вывод 40, линию di3 с вывода 42 на вывод 41. Новые назначения будут отмечены серым цветом.

9. Запустим перекомпиляцию проекта (Max+plusII | Compiler), убедившись, что отклю-чена опция Processing | Functional SNF Extractor, и включена опция Processing | Timing SNF Extractor.

10. После успешной перекомпиляции вернемся в окно редактора конфигурации и, вклю-чив опцию Layout | LastCompilationFloorplan, убедимся, что новые назначения выполнены. Эти назначения определяют в качестве формирователей входных векторов на плате тумблеры 5-8 (SW5-SW8) 8-разрядного переключателя, причем младший разряд (di0) задается переключателем 8, т.е. целью переназначения было установить общепринятый порядок, когда младший знача-щийбит находится справа.

11. ВведемкомандуменюAssign | Back-Annotate Project.

12. Загрузим файл проекта в ПЛИС на плате, вызвав окно программатора командой меню Max+plusII | Programmerи, переключая тумблеры 5-8 8-разрядного переключателя, проверим правильность работы дешифратора, наблюдая отображаемые на левом 7-сегментном индикаторе шестнадцатиричные цифры.

Лабораторные работы

по предмету «Вычислительная техника и информационные технологии»

Выполнили:

Группа АТз-11у

Проверил: Гаврилов А.В.

Пермь 2013 г.

Лабораторная работа №1