Синтез логических схем на мультиплексорах.

Мультиплексором называют устройства, которые позволяют реализовать логическую схему любой сложности. В отличие от интегральных схем, где имеется набор элементов, обладающих большой избыточностью, мультиплексор совмещает логические функции в модуле одного типа. Так как такой модуль выполнен в виде одного кристалла интегральной схемы (ИС), то он обладает более высоким быстродействием и надежностью, облегчает проектирование и упрощает компоновку печатной платы. При изготовлении мультиплексоров, можно использовать технологию средних интегральных схем для размещения на одном кристалле законченных функциональных логических схем (счетчики, дешифраторы, сдвиговые регистры и др.). При этом один тип модуля может обеспечить проектирование различных узлов одного изделия, а также различные изделия на одном и том же типе элементов. Мультиплексор в принципе может быть реализован на любых элементах, применяемых в схемотехнике: элементы диодно-транзисторной логики, транзисторно-транзисторной логики или любой другой. В настоящее время получили распространение два типа модулей: сдвоенные четырехвходовые (рис.2.4.а) и восьмивходовые (рис.2.4.б).

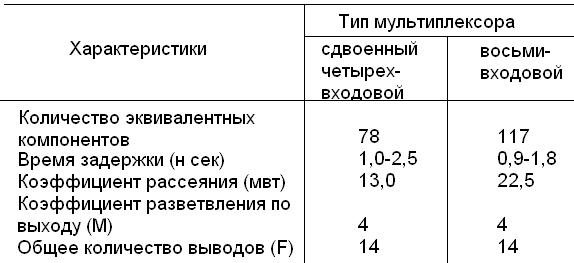

Основные характеристики рассматриваемых мультиплексоров приведены в табл.2.2.

Рис.2.4.

Таблица 2.2.

Структурная схема мультиплексора приведена на рис.2.5. Эта схема собрана из элементов «И-НЕ» и имеет М=2n-1, F=2n-1+n+1.

|

Рис.2.5.

Из основных положений построения логических схем можно показать, что для реализации любой булевой функции n переменных достаточно иметь устройство, которое содержит 2n-1 схемы, реализующие соответствующим образом подобранные 2n-1 минтермов. Если функция обращается в единицу на числе наборов больше чем 2n-1, то нетрудно показать, что в этом случае будут обязательно склеивающиеся минтермы и, следовательно, потребуется меньшее количество оборудования. Исходя из этих предпосылок можно организовать внутреннюю структуру мультиплексора. Половина четырехвходового мультиплексора может реализовать любую из 256 функций трех аргументов (рис.2.4,а). При этом на шины выборки подаются сигналы двух любых аргументов, а на входные шины соответствующие сигналы третьего аргумента.

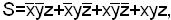

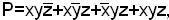

Предположим, что на мультиплексорах надо реализовать один разряд комбинационного сумматора на три входа. Так как в комбинационном сумматоре необходимо иметь значение суммы в данном разряде и значение переноса в последующий старший разряд, то целесообразно использовать сдвоенный четырехвходовой мультиплексор. Булево уравнение для функции суммы будет

для переноса

где S –сумма в данном разряде;

x, y –значения слагаемых в данном разряде;

z – перенос из предыдущего младшего разряда;

P – перенос в последующий старший разряд.

На основе булевых уравнений составляются таблицы истинности заданных функций и карты минимизации (рис.2.6,а,б).

Рис.2.6.

Карта Вейча могла быть составлена и без таблицы истинности непосредственно по формуле. Таблица истинности или карта минимизации используется для определения сигналов трех переменных к мультиплексору.

Таблица 2.3

| X | ||||||||

| Y | ||||||||

| Z | ||||||||

| S | ||||||||

| P |

Таблица истинности (табл.2.3) показывает, что когда x и y равны 0, функция выхода S совпадает с z. Это означает, что на вход J0 нужно подать аргумент z. Когда x=0 и y=1 (код на шинах выборки 01), внутренние логические схемы мультиплексора срабатывают таким образом, что к этой комбинации подключается вход J1. Для этого случая таблица истинности показывает, что выход S будет равен 1 только тогда, когда z=0. Следовательно, на вход J1 (рис.2.6,в) нужно подать дополнение z, т.е.  . Соответственно на вход J2 надо подать

. Соответственно на вход J2 надо подать  и на вход J3 - z. Это можно было определить, не прибегая к карте минимизации. Если для определения схемы подачи сигналов на входы используется карта минимизации, то требуется промежуточный этап. Карта делится на четыре двухячеечных участка, каждый из которых содержит одну ячейку для z и другую для его дополнения

и на вход J3 - z. Это можно было определить, не прибегая к карте минимизации. Если для определения схемы подачи сигналов на входы используется карта минимизации, то требуется промежуточный этап. Карта делится на четыре двухячеечных участка, каждый из которых содержит одну ячейку для z и другую для его дополнения  и соответствует одному из четырех входов модуля. Каждый участок карты будет содержать любую из четырех возможных комбинаций единиц и нулей (00, 01, 10, 11). Порядок расположения двоичных цифр определяет, какой сигнал должен быть получен на выходе мультиплексора и, следовательно, какой сигнал нужно подать на соответствующий вход. Если участок карты имеет код 11, на выходе всегда должен быть код 1. Для этого достаточно подать на соответствующий вход постоянное напражение, принимаемое за уровень, соответствующий логической единице. Если участок имеет код 00, выход всегда будет 0 и на соответствующий вход нужно подать постоянный уровень для 0 (чаще всего потенциал земли). Комбинации 1 и 0 разобраны в предыдущем примере.

и соответствует одному из четырех входов модуля. Каждый участок карты будет содержать любую из четырех возможных комбинаций единиц и нулей (00, 01, 10, 11). Порядок расположения двоичных цифр определяет, какой сигнал должен быть получен на выходе мультиплексора и, следовательно, какой сигнал нужно подать на соответствующий вход. Если участок карты имеет код 11, на выходе всегда должен быть код 1. Для этого достаточно подать на соответствующий вход постоянное напражение, принимаемое за уровень, соответствующий логической единице. Если участок имеет код 00, выход всегда будет 0 и на соответствующий вход нужно подать постоянный уровень для 0 (чаще всего потенциал земли). Комбинации 1 и 0 разобраны в предыдущем примере.

Составим логическую схему для переноса P(табл.2.3). На основании булева уравнения составим карту минимизации(рис.2.7,а). По карте минимизации составим логическую схему на половине сдвоенного четырехвходового мультиплексора (рис.2.7,б). В этой схеме на вход J0 подается потенциал, соответствующий сигналу 0(потенциал земли). На входы J1 и J2 подается входной сигнал z, так как функция обращается в единицу, когда z=1 и в нуль – когда z=0; на вход J3 подается сигнал, соответствующий единице, так как при любом значении z функция равна 1. Окончательно схема для одного разряда сумматора реализуется на одном сдвоенном четырехвходовом мультиплексоре (рис.2.8).

В целом, алгоритм определения схемы подключения сигналов ко входам мультиплексора может быть сформулирован следующим образом.

1. Составляется таблица истинности для трех переменных; определяется значение третьей переменной; берется аргумент или его отрицание или постоянные 0 или 1, которые должны быть поданы на входные шины.

2. Составляется карта минимизации; распределяются участки карты по входам Ji.

Рис.2.7. Рис.2.8

Метод использования универсальной логической схемы для функции трех переменных может быть распространен на реализацию функций четырех и более переменных. Для реализации функции четырех переменных удобнее использовать восьмивходовой мультиплексор. Покажем это на примере.

Пример. Пусть для реализации задана функция

f(ABCD)=m2+ m4+ m5+ m6+ m9+ m10+ m11+ m13.

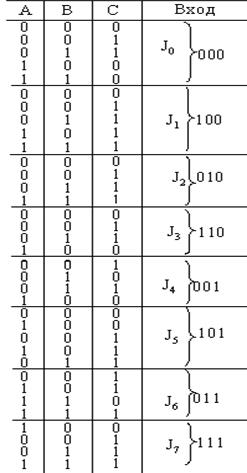

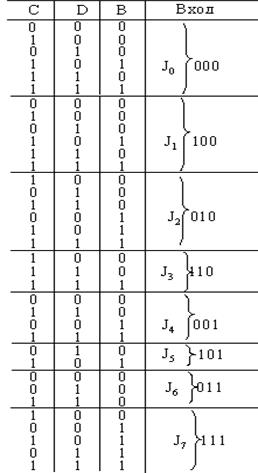

Составим таблицу истинности (табл.2.4) и карты минимизации как и в предыдущем случае (рис.2.9,а,б). Каждый участок карты приписывается каждому из восьми входов мультиплексора. Требуемая схема подачи входных сигналов определяется при рассмотрении карты в зависимости от того, какой код в них содержится – 00, 01, 10 или 11. Для данной функции схема подключения входов имеет вид (рис.2.9,в):

J0 – земля, J1 – D, J2 - U0, J3 – D, J4 -  , J5 - U0, J6 -

, J5 - U0, J6 -  , J7 – земля.

, J7 – земля.

При реализации функции от пяти и более переменных требуется более одного уровня универсальных логических схем. В этом случае один набор логических схем вырабатывает сигналы, подаваемые на другой набор схемы. Например, для реализации функций шести переменных в общем случае требуется восемь четырехвходовых мультиплексоров (4 ИС) на первом уровне и один восьмивходовой мультиплексор на втором уровне.

Таблица 2.4

| A | ||||||||||||||||

| B | ||||||||||||||||

| C | ||||||||||||||||

| D | ||||||||||||||||

| f(ABCD) |

Рис.2.9.

Чтобы создать схему, реализующую функцию шести переменных f(ABCDEF), переменные функции делят на две части A,B,C и D,E,F. В этом случае схемная реализация упрощается. Вместо задачи для шести переменных получаются две задачи при трех переменных, которые решаются следующим образом:

а) выделяют каждую их комбинаций D,E,F, получают функции остальных трех переменных fi(ABC), соответствующих каждой комбинации;

б) собирают все элементы функции fi(ABC), соответствующие каждому отдельному виду комбинации входных сигналов D,E,F;

в) реализуют каждую функцию переменных A,B,C как функцию трех переменных, получают выходные сигналы первого уровня;

г) подают эти входные сигналы первого уровня на восьмивходовой мультиплексор, который управляется комбинациями сигналов D,E,F, поступающими на шины выборки.

Покажем это на примере функции

f(ABCDEF)=∑0,2,4,5,6,9,10,11,12,13,14,15,17,

24,25,26,28,29,30,31,32,33,37,38,39,

43,44,45,48,51,58,59,60,63.

В таблице истинности (табл.2.5) покажем только те наборы, на которых функция обращается в единицу (рис.2.10).

В некоторых случаях схема может быть упрощена перестановкой аргументов, которые должны быть включены на первом уровне. Переменные должны располагаться так, чтобы для двух или более групп Ji их значения были бы или инверсны друг другу, или имели бы одинаковые значения. В этих случаях один и тот же элемент можно использовать несколько раз (если для некоторых Ji аргументов на первом уровне принимают одинаковые значения). Если аргументы на первом уровне для некоторых значений Ji –х принимает противоположные значения, то в этом случае можно использовать инверсию от Ji –го выхода. Заданную функцию f(ABCDEF) можно реализовать путем преобразования ее в функцию 1-го уровня f(CDB) (вместо f(ABC)) и комбинацию переменных второго уровня EFA. При такой группировке значения функции f(CDB) одинаковы для членов второго уровня J0 и J1, а член второго уровня J7 является дополнением J6. В результате такой группировки для реализации заданной функции требуется на два четырехвходовых мультиплексора меньше, чем в предыдущем случае (табл.2.6).

Табл. 2.5. Табл.2.6.

Так как последовательные устройства можно рассматривать в качестве обычных логический устройств с обратными связями, то это означает, что мультиплексор может быть использован и при реализации конечных автоматов.Мультиплексоры являются основным элементом для моделирования базовых ячеек ПЛИС.

Рис.2.10

Контрольные задания.

А. Минимизировать функции методом Квайна.

1.f (А,В,С)=АВ +АВС+ АВС+АВС.

2.f (А,В,С)=АВ +С+ АВС+ВС+АВ

3.f (А,В,С)=АВС+АВ+АВС+АВСД+СД

4. f (А,В,С,Д)=m4+ m5+m6+m7+m12+m14+m15

5. f (А,В,С,Д)=m1+ m5+m5+m7+m9+m11 +m13+m15

Б. Минимизировать функции методом Макс-Класки

1. f (А,В,С,Д)=m3+ m4+m5+m7+m9+m11 +m13+m15

2.f (А,В,С,Д)=АВД + АВСД+ АВСД+ АВСД+ АВСД

3.f (А,В,С,Д)=ВСД + АВСД+ АВСД+ АВСД+ АВСД+ АВСД

4. f(х1, х2 х3х4 )= х1 х2х3 х4 + х1 х2х3 х4 х5

5.f (А,В,С,Д)=АВСД + АВСД+ АВСД+ АВСД+ АВСД+ АВСД

Подсчитать количество элементов И, ИЛИ, НЕ требуемых для реализации заданных функций.

В. Минимизировать функции методом карт Вейна.

1.f (А,В,С)= АВ + АВС +АВС + АВС

2.f (А,В,С)=АВС + АВС + АВС + АВС

3.f (А,В,С)=АВС + АВС + АВС + АВС

4. f (А,В,С,Д)=m0+m1+ m4 +m5+m10+m11+m14+m15

5. f (А,В,С,Д)=m4+m5+ m6 +m7+m12+m13+m14+m15

Построить схемы, реализующие заданные функции на элементах И, ИЛИ, НЕ.

Г. Найти минимальные конъюнктивные формы функций.

1. f (А,В,С)=m5+m3+ m6 +m7

2. f(х1, х2 х3 )= х1 х2х3 + х1 х2х3 + х1 х2х3 + х1 х2х3

3. f (А,В,С,Д)=m0+m1+ m2 +m5+m9+m10+m12+m13 +m14

Подсчитать число элементов И, ИЛИ, НЕ требуемых для реализации заданных функций.

Д. Найти минимальные формы предоставления частичных функций.

1.f (А,В,С,Д)=АВС + ДВС + АСД -если минтерм избыточен

2.f (А,В,С,Д)=m1+m2+ m5 + m6 +m7 +m10 , если минтермы m0+m4+ m15 избыточны

3.f(х1, х2 х3 х4)= х1, х2 х3 х4 + х1, х2 х3 х4 , если конъюнкция ВС избыточна.

4.f (А,В,С,Д)= m7 +m11 + m13 +m14 если минтерм m15 избыточен.

5.f(х1, х2 х3 х4)= х1, х2 х3 х4 + х1, х2 х3 х4 , если х4 избыточен.

Е. Минимизировать системы функций.

1. f (А,В,С)= m0+m1+ m3

f (А,В,С)=m1+m2+ m5

f (А,В,С)=m3+m5 +m7

2. f(х1, х2 х3 )= m0+ m2 +m4+ m7

f(х1, х2 х3 )= m0+m3+m5 +m7

3. f (х1, х2 х3)=m1+m3 +m7

f (х1, х2 х3)= m2 +m4

f (х1, х2 х3)=m1+m4+ m5

Ж. Определить количество элементов И-НЕ для реализации следующих функций.

1. f (А,В)= m0+m1

2. f (А,В,С)= m0+m1 + m2 +m3 +m4+m5

3. f (А,В,С,Д)= m0+m1 + m2 +m3 +m12+m13 + m14 +m15

4. f (А,В,С,Д)= m0+m1 + m2 +m3 +m4+m5+m8 + m9

З. Построить схему на элементах И-НЕ, реализующюю функции.

1.f (А,В,С)=АВС+АВС+АВС+АВС

2.f (А,В,С,Д)=АВСД+АВСД+АВСД+АВСД+АВСД+АВСД+АВСД

3.f (х1, х2 х3)=m1+m2+m3 +m4+m5+ m6+m7+m8 + m11 +m12 + m13

И. Определить количество элементов ИЛИ-НЕ для реализации функций

1. f (А,В,С)=М0+М1+М3+М5

2.f (А,В,С,Д)=m0+ m2+m3 +m4+m5+ m6 +m9 + m12 + m13

3. f (А,В,С,Д)=m0+ m1 + m6+m7 +m8+m9 + m12 + m13 + m14 + m15

К. Построить схему на элементах ИЛИ-НЕ для реализации функций.

1. f (А,В,С,Д)=М0М3М5М7М11

2.f (А,В,С,Д)=АВ+ВСД+ВС+АВД