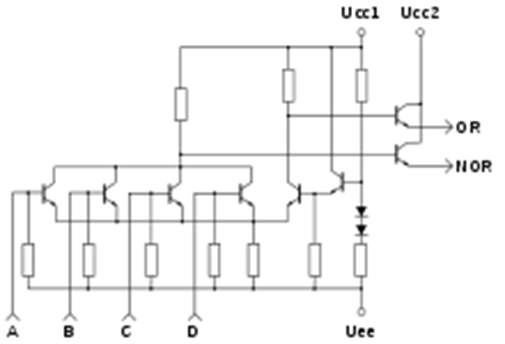

Схема эмиттерно-связанной логики

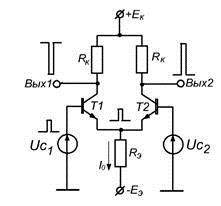

Диференциальный усилительный с генератором стабильного тока.—

Или вот еще,,

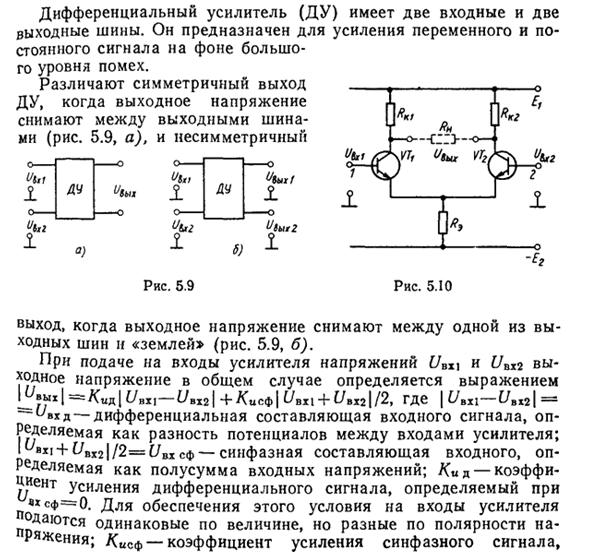

Значительно минимизировать температурный дрейф нуля можно, используя параллельно-балансные каскады усилителя, построенные на двух идентичных по своим параметрам и характеристикам транзисторах. Такие усилители называются дифференциальными.

Дифференциальные усилители (ДУ) представляют широкий класс усилителей, основным назначением которых является усиление разности между двумя сигналами. По этой причине их также называют разностными усилителями. Свойства ДУ зависят от симметрии между двумя плечами схемы. Балансная природа ДУ делает его идеальным усилителем в интегральном исполнении. Так как практически невозможно получить два абсолютно идентичных по своим параметрам и характеристикам транзистора на дискретных элементах, дифференциальные усилители изготавливают по интегральной технологии, поскольку такой технологии свойственно хорошее согласование элементов усилителя. Принципиальным достижением планарной технологии явилось создание на одной подложке пары строго согласованных по своим параметрам и характеристикам транзисторов. Степень согласования параметров определяется качеством технологического процесса. Для транзисторов, расположенных на одном кристалле, эквивалентная разность температур переходов может быть доведена до нескольких десятых долей градуса. Столь малая разность температур позволяет серийным интегральным дифференциальным структурам иметь разрешающую способность по постоянной составляющей порядка десятых долей милливольта. Температурный дрейф постоянной составляющей при этом имеет порядок единиц микровольт на  изменения окружающей температуры. Такие характеристики обусловили ключевую роль дифференциального усилителя в схемотехнике линейных интегральных схем. Принципиальная схема дифференциального усилителя приведена на рис.5.38. У дифференциального усилителя два входа и два выхода. Можно подавать разные сигналы на оба входа. Можно подавать сигнал на один из входов, второй вход при этом заземляется. Выходной усиленный сигнал можно снимать между выходами усилителя, либо с каждого из выходов относительно земли.

изменения окружающей температуры. Такие характеристики обусловили ключевую роль дифференциального усилителя в схемотехнике линейных интегральных схем. Принципиальная схема дифференциального усилителя приведена на рис.5.38. У дифференциального усилителя два входа и два выхода. Можно подавать разные сигналы на оба входа. Можно подавать сигнал на один из входов, второй вход при этом заземляется. Выходной усиленный сигнал можно снимать между выходами усилителя, либо с каждого из выходов относительно земли.

Рис.5.38. Дифференциальный усилитель

Рис.5.38. Дифференциальный усилитель

При полной симметрии схемы, когда напряжения на входах равны нулю, коллекторные токи транзисторов одинаковы, потенциалы коллекторов левого и правого транзисторов также одинаковы и выходное напряжение между коллекторами транзисторов равно нулю. Любые изменения температуры окружающей среды или флуктуации напряжения питания вызовут одинаковые изменения коллекторных токов и коллекторных напряжений транзисторов. Выходное напряжение между коллекторами при этом останется равным нулю.

Дифференциальный усилитель усиливает разность входных сигналов. У высококачественных дифференциальных усилителей сопротивление резистора  Должно быть неограниченно велико. Совместно с источником питания

Должно быть неограниченно велико. Совместно с источником питания  этот резистор образует генератор стабильного тока

этот резистор образует генератор стабильного тока  . Поэтому необходимо обеспечить высокую стабильность источника питания усилителя, так как качество усилителя зависит от стабильности тока

. Поэтому необходимо обеспечить высокую стабильность источника питания усилителя, так как качество усилителя зависит от стабильности тока  . У дифференциального усилителя ток

. У дифференциального усилителя ток  практически не зависит от наличия сигналов на входах.

практически не зависит от наличия сигналов на входах.

Схема эмиттерно-связанной логики.

Эми́ттерно-свя́занная ло́гика (ЭСЛ, ECL) — способ построения логических элементов на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен. Низкие значения логических перепадов в ЭСЛ-логике способствуют снижению влияния на быстродействие паразитных ёмкостей[1].

Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ), а на транзисторах. Схема представляет собой транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор, у которого напряжение на базе выше, пропускает через себя основной ток. Как правило, один транзистор в схеме сравнения подключен к опорному уровню, равному напряжению логического порога, а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители.