Система команд мк семейства mcs-51

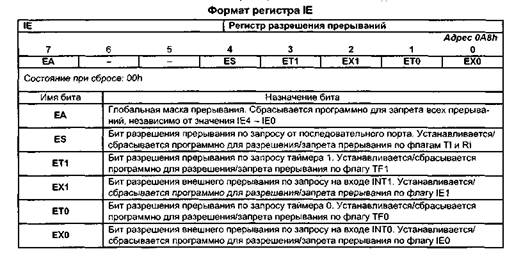

Система команд MCS-51 включает 111 инструкций. Команды процессорного ядра MCS-51 имеют однобайтовый, двухбайтовый и трехбайтовый формат. Большинство команд (94) имеют формат один или два байта и выполняются за один или два машинных цикла. При тактовой частоте 12 МГц длительность машинного цикла составляет 1 мкс. Множество команд делится на 5 традиционных групп, каждая из которых рассмотрена ниже. Распределение команд по группам приведено в табл. 4.6.

Таблица 4.6

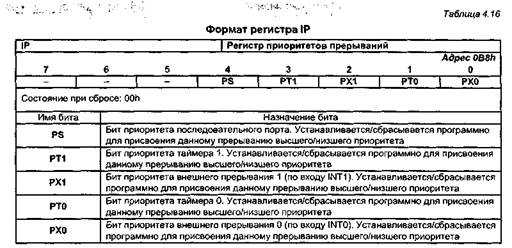

Главная отличительная особенность системы команд ядра MCS-51 - наличие большого числа двухадресных команд передачи данных. Операнды под управлением одной команды могут перемещаться не только между одним из регистров центрального процессора и ячейкой памяти, но и между двумя ячейками памяти, которые адресуются различными способами. Множество сочетаний возможных способов адресации операндов в двухадресных командах обусловливает наличие 13 различных форматов команд (рис. 4.36). Первый байт команды всегда содержит код операции (КОП). Второй и третий байты содержат либо адреса операндов, либо сам операнд.

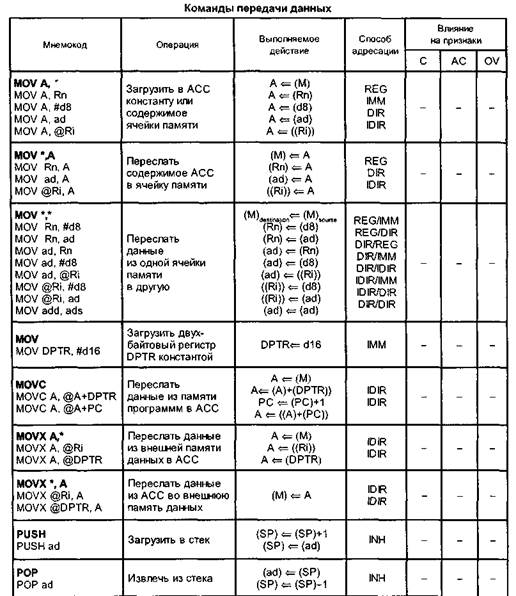

Команды передачи данных.Команды этой группы осуществляют перемещение данных между ячейками памяти и регистрами центрального процессора, а также между двумя ячейками памяти, минуя регистры центрального процессора (табл. 4.7). Все команды данной группы не модифицируют флаги результата, за исключением команд загрузки регистра признаков PSW и аккумулятора (изменяется признак четности Р).

Таблица 4.7

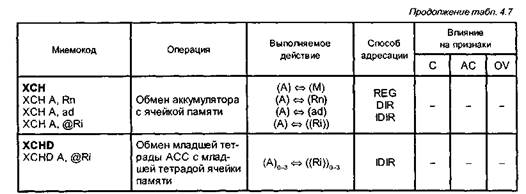

1 В зависимости от способа адресации и места расположения операнда можно выделить девять типов операндов, между которыми возможен обмен. Граф возможных операций передачи данных показан на рис. 4.37. Аккумулятор АСС представлен на этом графе отдельной вершиной, поскольку многие команды используют неявную адресацию аккумулятора (символ А присутствует в мнемонике команды, в то время как поле адреса аккумулятора отсутствует). Команды передачи данных допускают также прямую адресацию аккумулятора. Для этого его абсолютный адрес 0E0h должен быть указан во втором или третьем байтах команды. Косвенная адресация по указателям @R0 и @R1 распространяется только на адресное пространство 00h.. .7Fh внутреннего ОЗУ. Регистры специальных функций и регистры центрального процессора (диапазон адресов 8Fh - 0FFh) не могут быть адресованы косвенно.

Следует обратить внимание, что команды обращения к ячейкам внешней памяти (MOVX) и команды чтения из памяти программ (MOVC) отличаются от команд обмена с внутренним ОЗУ. Такое положение дел полностью соответствует теории: для обращения к ячейкам с одинаковыми адресами, но в разных массивах памяти должны быть сгенерированы разные сигналы управления. Следовательно, должны использоваться разные команды.

Арифметические команды.Данную группу образуют 24 команды (табл. 4.8), которые выполняют операции сложения (ADD и ADDC), вычитания (SUBB), инкремента и декремента (INC и DEC), умножения (MUL), деления (DIV) и десятичной коррекции (DAA). Команды сложения, вычитания, инкремента и декремента могут быть использованы с четырьмя различными способами адресации внутренней памяти. Команда инкремента выполняется также над двухбайтовым регистром DPTR. Арифметические действия с операндами из внешней памяти данных и памяти программ не производятся.

Команда умножения MUL выполняет операцию целочисленного беззнакового умножения. Сомножители расположены в регистрах АСС и В, двухбайтовое произведение в В:АСС. Время выполнения операции составляет 4 машинных цикла. Команда деления DIV выполняет целочисленное беззнаковое деление однобайтового делимого (АСС) на однобайтовый делитель (В). Целое частное расположено в АСС, остаток - в В. Время выполнения операции - 4 цикла.

Таблица 4.8

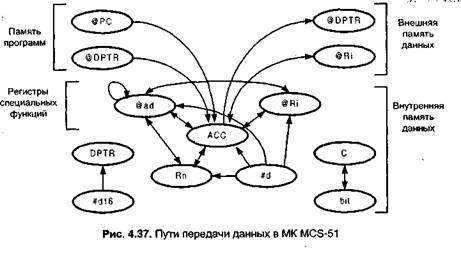

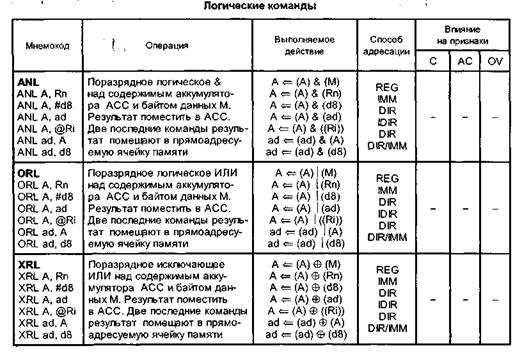

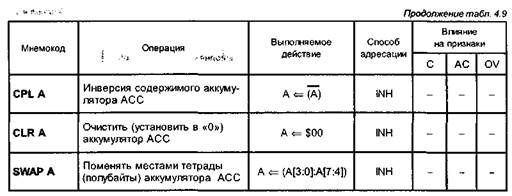

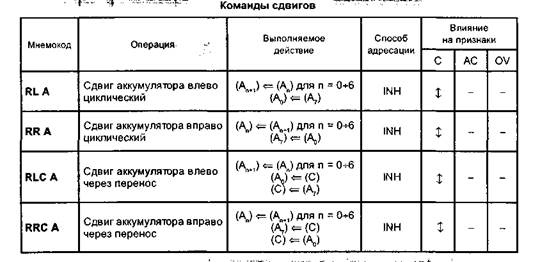

Логические команды и операции сдвига.Данную группу образует 25 команд. Выполняются операции логического И, ИЛИ, Исключающего ИЛИ, операции очистки и инверсии аккумулятора, различные операции сдвига. Логические команды модифицируют только флаг7, команды сдвига -флаги С и Z. Типы инструкций данной группы приведены в табл. 4.9 и 4.10.

Таблица 4.9

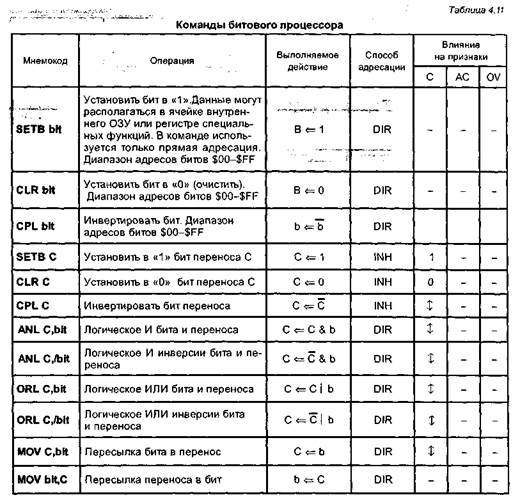

Команды битового процессора.Данную группу образуют 12 команд (табл. 4.11). Совокупность этих команд называют битовым процессором. Наличие команд битового процессора позволяет существенно сократить управляющие программы по объему кода и времени выполнения. Обратите внимание, что прямоадресуемые биты находятся только в части ячеек внутреннего ОЗУ и в регистрах специальных функций. Аккумулятор АСС, регистр В и регистор признков PSW также имеют побитный доступ (см. рис. 4.34).

Команды условного перехода по значениям отдельных битов JB и JNB могут быть отнесены как к группе команд битового процессора, так и к группе команд управления. Поэтому последние приведены в следующем разделе.

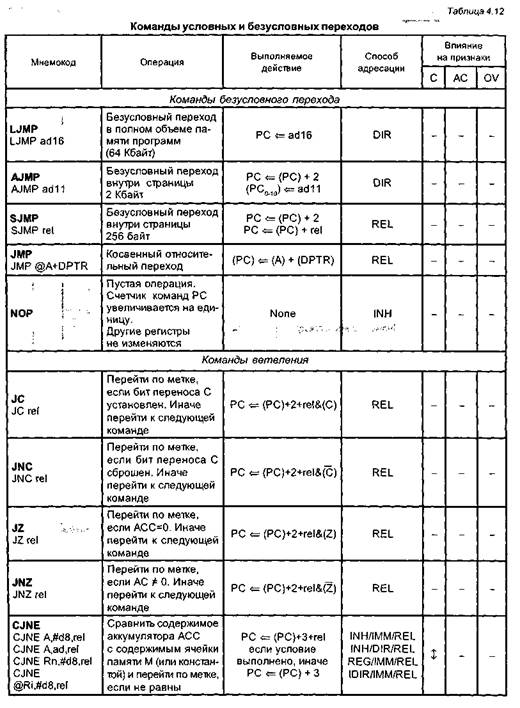

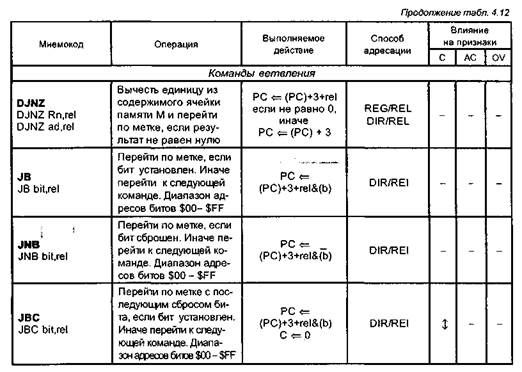

Команды передачи управления.Группа команд передачи управления является самой многочисленной группой. Она содержит 40 инструкций, которые делятся на две подгруппы:

1)команды условных и безусловных переходов (табл. 4.12);

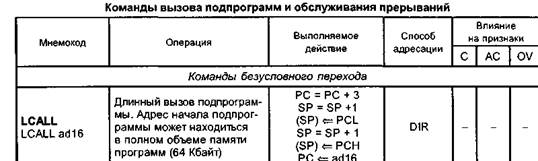

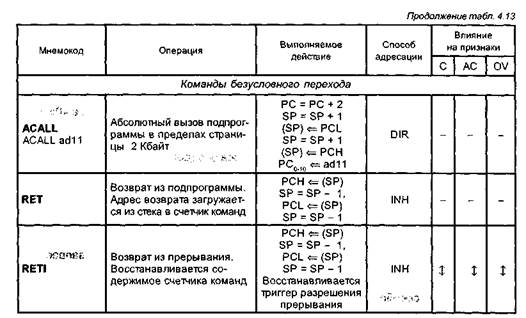

2)команды вызова подпрограмм и обслуживания прерываний (табл. 4.13).

Таблица 4.10

Центральный процессор MCS-51 может использовать три команды условного перехода: традиционную трехбайтовую команду (длинный переход - LongJMP) и две двухбайтовые команды - AJMP и SJMP. При написании программ на языке Ассемблера допускается употребление мнемоники JMP. Транслятор с языка Ассемблера выберет вариант с меньшим временем реализации.

Группа команд ветвления позволяет выполнить переходы по значениям бита переноса С и флага нулевого результата в аккумуляторе Z, а также по значению прямоадресуемого бита. Особое внимание следует обратить на команды CJNZ и DJNZ. Первая (CJNZ) позволяет сравнить два операнда и перейти по метке в случае неравенства.Вторая(DJNS) предназначена для организации циклов : содержимое счетчика циклов уменьшается на единицу и осуществляется переход по метке,если результат не равен нулю.

|

Подобно командам безусловного перехода, центральный процессор MCS-51 имеет две команды вызова подпрограмм: трехбайтовую LCALL и двухбайтовую ACALL. При составлении исходного текста прикладной программы можно использовать аббревиатуру CALL. Транслятор с языка Ассемблера подставит необходимый код в зависимости от расположения вызываемой программы в кодовом сегменте.

Особое внимание следует обратить на команду выхода из подпрограммы прерывания RTI. На первый взгляд, ее действие ничем не отличается от команды RET. Однако в дополнение к последней команда RTI восстанавливает программно недоступный триггер разрешения прерывания, который автоматически сбрасывается при входе в подпрограмму прерывания.

Таблица 4.13

СИСТЕМА ПРЕРЫВАНИЙ

Система прерываний МК 8051 АН включает пять источников -два внешних и три внутренних. Внешние запросы поступают на входы INTO/P3.2 и INT1/P3.3, внутренние запросы формируются модулями таймеров Таймер 0 и Таймер 1, а также контроллером последовательного интерфейса. В процессе формирования запроса на прерывание каждый источник запроса выставляет в «1» специальный флаг. Этот флаг вызовет генерацию запроса на прерывание, если прерывания от данного источника разрешены. В подпрограмме обслуживания прерывания флаг- источник запроса -должен быть сброшен. Если же прерывания от данного источника запрещены, то логика установки флага запроса не изменяется, но обслуживаться данный флаг должен только программно, без использования аппаратных средств подсистемы прерывания.

Для формирования внешнего запроса на прерывание необходимо установить активный уровень сигнала на одном из входов: INTO/P3.2 или INT1/P3.3 (см. рис. 4.32). Распознавание микроконтроллером активного уровня сопровождается установкой триггеров запроса внешних прерываний IEO и IE1 в регистре управления таймера TCON (см. табл. 4.19). Прерывания по входу INTO/P3.2 разрешает флаг ЕХО регистра разрешения прерываний IE, по входу 1МТ1/РЗ.З-флагЕХ1 того же регистра (см. табл. 4.15). Каждый из входов - INTO/P3.2 или INT1/P3.3 - может быть программно настроен на один из двух режимов распознавания сигнала запроса:

1) Активным является низкий уровень сигнала. Он должен удерживаться на входе до начала обслуживания микроконтроллером данного запроса. Далее сигнал должен стать пассивным до завершения процедуры обслуживания. В противном случае триггер запроса на прерывание будет установлен повторно. Описанная логика установки триггера внешнего прерывания получила название статического режима распознавания запроса.

2) Активным является перепад сигнала с «1» на «0». Для распознавания запроса высокий и низкий уровни сигнала должны быть длительностью не менее одного машинного цикла каждый. По истечении одного машинного цикла после перепада сигнала внешнего запроса с «1» на «0» устанавливается в «1» один из флагов ЕХ0 или ЕХ1. После этого уровень сигнала внешнего запроса может быть произвольным. Даже если он остался низким после завершения процедуры обслуживания прерывания, то повторной установки флагов ЕХ0 или ЕХ1 не произойдет. Следующий запрос будет воспринят МК только если сигнал на входе INTO или INT1 установится в «1», а затем опять в «0». Описанная логика установки триггера запроса на прерывание носит название динамического режима распознавания запроса.

Выбор режима распознавания внешнего запроса определяют биты IT0 и IT1 регистра TCON (см. табл. 4.19). Если выбран статический режим распознавания внешнего запроса, то установленные триггеры ЕХО и ЕХ1 должны быть сброшены в подпрограмме обслуживания соответствующего прерывания. Для этой цели наиболее удобно использовать команды битового процессора: CLR ЕХ0 и CLR EX1. Если выбран динамический режим распознавания внешнего запроса, то триггеры ЕХ0 и ЕХ1 сбрасываются автоматически при переходе на соответствующую подпрограмму прерывания.

Модули таймеров таймер 0 и таймер 1 используют для формирования запросов на прерывания триггеры переполнения TF0 иТР1 регистра TCON (см. табл. 4.19). При переходе к выполнению соответствующей подпрограммы прерывания эти флаги сбрасываются автоматически. Поэтому нет необходимости предусматривать специальные команды для сброса флагов TF0 и TF1. Прерывания по переполнению таймера 0 разрешает флаг ЕТ0 регистра разрешения прерывания IE, по переполнению таймера 1 - флаг ЕТ1 того же регистра (см. табл. 4.15).

Модуль последовательного порта выставляет два флага, которые могут генерировать запросы на прерывание. Это триггеры TI и RI регистра SCON. Первый формируется по окончании передачи байта данных, второй - по окончании приема очередного байта. Флаги генерируют один общий запрос на прерывание. В подпрограмме обслуживания прерывания следует проанализировать, какой из триггеров вызвал формирование запроса на прерывание, и сбросить его. Если к моменту перехода на подпрограмму прерывания установленными оказались сразу оба флага TI и RI, то удобно производить обслуживание последовательного порта, прерываясь дважды. В первой подпрограмме прерывания распознается один из флагов, например TI. Выполняются действия по загрузке нового байта в регистр данных последовательного передатчика и сбрасывается флагТ Ι. Первая подпрограмма прерывания завершается командой RETI. Так как флаг RI остался в «1», то генерируется новый запрос на прерывание от последовательного порта и в соответствующей подпрограмме прерывания обслуживается блок приемника данного модуля. Перед завершением подпрограммы прерывания сбрасывается флаг RI. Прерывания по запросу последовательного порта разрешает флаг ES регистра IE.

Все рассмотренные прерывания могут быть вызваны или отменены программой, поскольку перечисленные флаги запросов программно доступны и могут быть установлены/сброшены программой так же, как и аппаратными средствами МК.

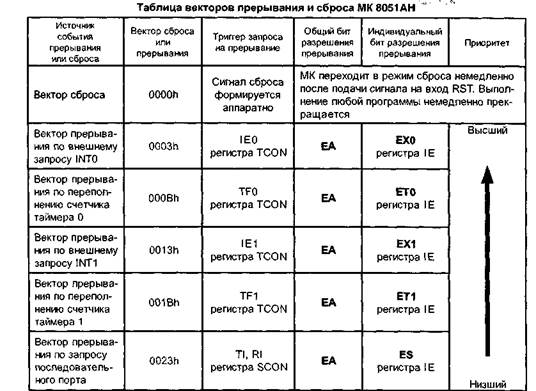

Сформированные посредством установки триггеров запросы на прерывание поступают в центральный процессор. Эти запросы могут быть приняты к обработке, если триггер ЕА регистра IE установлен в «1», или обработка запросов будет задержана до тех пор, пока триггер ЕА будет находиться в «0». Триггер ЕА устанавливается и сбрасывается только программно. Таким образом, команда SETB ЕА эквивалентна команде «разрешить прерывания», а команда CLR ЕА-команде «запретить прерывания». Если прерывания центрального процессора разрешены, то МК завершает выполнение текущей ко манды, сравнивает уровни приоритетов в случае одновременного поступления нескольких запросов и формирует внутренними аппаратными средствами код команды LCALL. Двухбайтовый адрес команды LCALL соответствует вектору прерывания с наивысшим приоритетом. МК с ядром MCS-51 имеют фиксированные векторы прерывания. Абсолютные значения векторов прерывания для каждого из источников, соответствующие им триггеры запросов и флаги битов разрешения прерывания приведены в табл. 4.14.

Таблица 4.14

Запрос на прерывание не обслуживается центральным процессором и откладывается на более позднее время в следующих случаях: ___ __ _

• текущий цикл не является последним циклом команды;

• выполняется процедура обслуживания прерывания с более высоким приоритетом;

• выполняется команда RETI, команды обращения к регистрам специальных

функций подсистемы прерывания IE и IP.

Если флаг прерывания был установлен, но не получил обслуживания, а к моменту снятия блокировки прерываний был сброшен, то запрос на прерывание теряется.

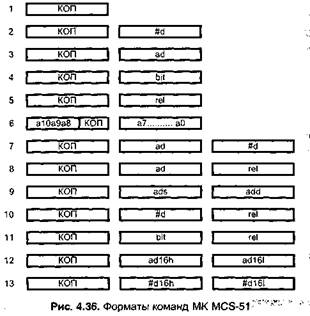

При появлении запросов от нескольких источников очередность их обслуживания определяется механизмом приоритетов. В МК с ядром MCS-51 реализована двухступенчатая система приоритетов. Все запросы подразделяются на две группы: с высоким или с низким уровнем приоритета. Принадлежность к той или иной группе определяется значением битов регистра приоритетов IP (табл. 4.16). Если бит регистра IP равен 1, то соответствующий источник запроса относится к группе с высоким приоритетом, если 0 — то с низким. Действие механизма приоритетных прерываний в MCS-51 заключается в выборе одного из источников при одновременном появлении нескольких запросов, а также в принятии решения о прерывании подпрограммы обслуживания другого прерывания при поступлении нового запроса. При одновременном появлении нескольких запросов сначала обслуживаются запросы группы с высоким приоритетом, а затем группы с низким приоритетом. Внутри каждой группы распределение приоритетов фиксировано в соответствие с табл. 4.14. Механизм приоритетных прерываний использует два программно-недоступных триггера уровня обслуживаемого прерывания. Переход к подпрограмме обслуживания запроса сопровождается установкой триггера того уровня приоритета, к которому относится запрос. При установленном триггере низшей группы запрос высшей группы вызовет прерывание подпрограммы обслуживания прерывания. Команда RETI в конце процедуры обслуживания сбрасывает триггер своего уровня. В этом отличие команды возврата из прерывания RETI от команды возврата из подпрограммы RET.

Процесс выполнения команды LCALL сопровождается загрузкой в стек содержимого счетчика команд PC (адрес следующей команды). Сохранение в стеке других регистров МК может быть выполнено в подпрограмме прерывания с использованием команды PUSH. В конце подпрограммы прерывания эти регистры должны быть восстановлены из стека командами POP. Однако следует иметь в виду, что программное сохранение в стеке регистров значительно увеличивает время реакции на прерывание. Минимальное время перехода к подпрограмме прерывания составляет 3 машинных цикла. Последней командой каждой подпрограммы прерывания должна быть команда RETI, которая восстанавливает из стека адрес следующей команды прерванной программы и очищает флаг блокировки прерываний своего уровня.

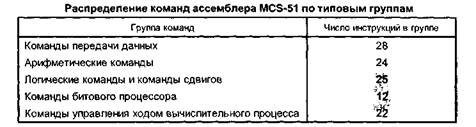

Непосредственно к подсистеме прерывания относятся два регистра специальных функций:

IE - регистр разрешения прерываний;

IP - регистр приоритетов прерываний.

Форматы этих регистров приведены в табл. 4.15 и 4.16. Кроме этого, в обслуживании прерываний используются биты регистров управления таймерами TCON и портом последовательного ввода/вывода SCON.

Таблица 4.15