Список микрооперации и логических условий, реализуемых в ОА

| Микрооперация | Действие | Логическое Условие | Действие |

| y1 | B[0]:=|B[0] | x1 | F=1 |

| y2 | A`:=|A` | x2 | F`=1 |

| y3 | B`:=|B` | x3 | A[0]=1 |

| y4 | C:=A+B | x4 | B[0]=1 |

| y5 | C:=C+1 | x5 | C[-1]=1 |

| y6 | OV:=1 | x6 | A[0]=B[0] |

| y7 | OV:=0 | x7 | B[0]=C[0] |

| y8 | C`:=|C` | x8 | C[0]=1 |

| y9 | Z:=1 | x9 | C[15]=0 |

| y10 | Z:=0 | x10 | A[15]=B[15] |

| y11 | I:=0 | x11 | I=16 |

| y12 | I:=I+1 | ||

| y13 | C:=1 | ||

| y14 | C:=0 | ||

| y15 | A=П1(A) | ||

| y16 | B=П1(B) | ||

| y17 | С=П1(С) |

Микропрограмма выполняемых в АЛУ операций.

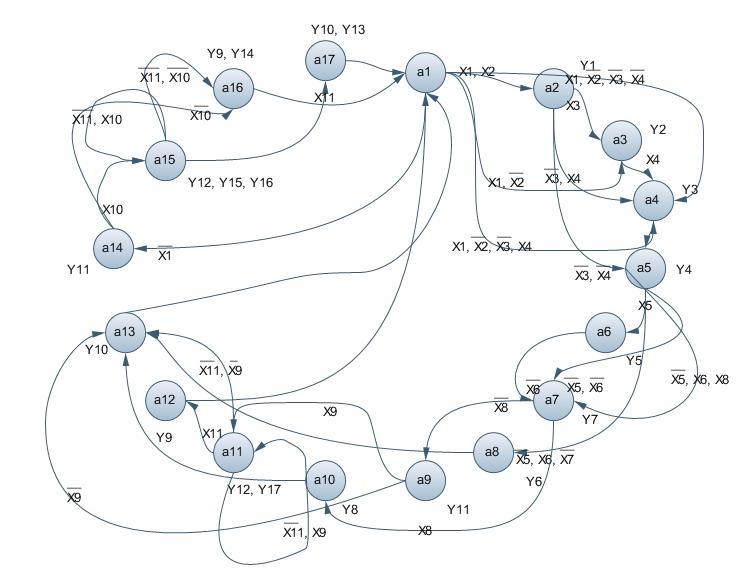

Рис 3б. Микропрограмма выполняемых в АЛУ операций в терминах микроопераций и логических условий с разметкой состояний для проектирования управляющего автомата (лист второй).

Рис 3в. Микропрограмма выполняемых в АЛУ операций в терминах микроопераций и логических условий с разметкой состояний для проектирования управляющего автомата (лист третий).

Проектирование управляющего автомата АЛУ

Для проектирования данного УА выполним соответствующую разметку микропрограммы:

| A1 | Начало, конец |

| A2 | Y1 |

| A3 | Y2 |

| A4 | Y3 |

| A5 | Y4 |

| A6 | Y5 |

| A7 | Y7 |

| A8 | Y6 |

| A9 | Y11 |

| A10 | Y8 |

| A11 | Y12, Y17 |

| A12 | Y9 |

| A13 | Y10 |

| A14 | Y11 |

| A15 | Y12, Y15, Y16 |

| A16 | Y9, Y14 |

| A17 | Y10, Y13 |

Из полученной разметки построим граф автомата:

Кодирование входных символов:

| Входной символ | Код | Входной символ | Код |

| X1 | X7 | ||

| X2 | X8 | ||

| X3 | X9 | ||

| X4 | X10 | ||

| X5 | X11 | ||

| X6 |

Кодирование состояний автомата:

| Состояние автомата | Код T1, T2, T3, T4, T5 | Состояние автомата | Код T1, T2, T3, T4, T5 |

| A1 | A10 | ||

| A2 | A11 | ||

| A3 | A12 | ||

| A4 | A13 | ||

| A5 | A14 | ||

| A6 | A15 | ||

| A7 | A16 | ||

| A8 | A17 | ||

| A9 |

При выборе элемента памяти следует учитывать простоту управления им. С этой точки зрения удобно выбирать триггеры, управляемые по единственному информационному входу – к таким относятся D- и T- триггеры. В нашем примере в качестве элемента памяти автомата выберем синхронный двухтактный D-триггер. Очевидно, для реализации нашего автомата понадобится пять D-триггеров.

Построим автоматную таблицу переходов:

| Исходное состояние | Условие перехода | Состояние перехода | Функции возбуждения | ||||

| D1 | D2 | D3 | D4 | D5 | |||

| (a1) 00001 | x1 x2 | a(2) 00010 | |||||

| |x1 | a(14) 01110 | ||||||

| x1 |x2 x3 | a(3) 00011 | ||||||

| x1 |x2 |x3 x4 | a(4) 00100 | ||||||

| x1 |x2 |x3 |x4 | a(5) 00101 | ||||||

| (a2) 00010 | x3 | a(3) 00011 | |||||

| |x3 x4 | a(4) 00100 | ||||||

| |x3 |x4 | a(5) 00101 | ||||||

| (a3) 00011 | x4 | a(4) 00100 | |||||

| |x4 | a(5) 00101 | ||||||

| (a4) 00100 | a(5) 00101 | ||||||

| (a5) 00101 | x5 | a(6) 00110 | |||||

| |x5 |x6 | a(7) 00111 | ||||||

| |x5 x6 x7 | a(7) 00111 | ||||||

| |x5 x6 |x7 | a(8) 01000 | ||||||

| (a6) 00110 | |x6 | a(7) 00111 | |||||

| x6 |x7 | a(8) 01000 | ||||||

| (a7) 00111 | x8 | a(10) 01010 | |||||

| |x8 | a(9) 01001 | ||||||

| (a8) 01000 | a(13) 01101 | ||||||

| (a9) 01001 | x9 | a(11) 01011 | |||||

| |x9 | a(13) 01101 | ||||||

| (a10) 01010 | a(13) 01101 | ||||||

| (a11) 01011 | |x11 x9 | a(11) 01011 | |||||

| x11 | a(12) 01100 | ||||||

| |x11 |x9 | a(13) 01101 | ||||||

| (a12) | a(1) 00001 | ||||||

| (a13) | a(1) 00001 | ||||||

| (a14) 01110 | x10 | a(15) 10000 | |||||

| |x10 | a(16) 10001 | ||||||

| (a15) 10000 | x11 | a(17) 10010 | |||||

| |x11 x10 | a(15) 10000 | ||||||

| |x11 |x10 | a(16) 10001 | ||||||

| (a16) 10001 | a(1) 00001 | ||||||

| (a17) 10010 | a(1) 00001 |

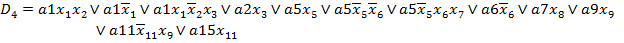

Запишем комбинационную схему, реализующую функцию переходов автомата. В моём случае эта схема реализует пять булевых функций D1, D2, D3, D4, D5.

Запишем комбинационную схему, реализующую функцию выходов автомата.

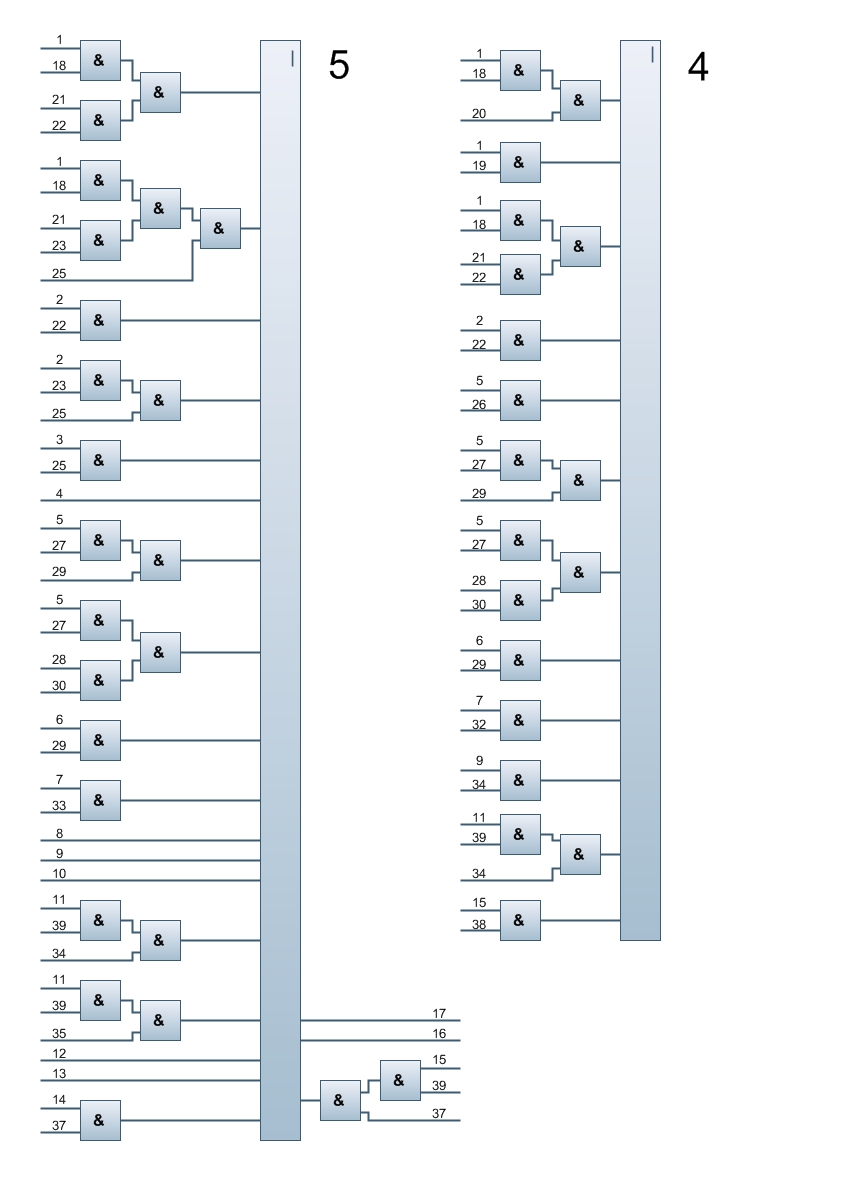

Теперь изобразим функциональную схему управляющего автомата, используя функцию переходов и функцию выходов, с учётом выбранного элемента памяти:

Структурная схема управляющего автомата

Структурная схема управляющего автомата (дополнение 1)

Структурная схема управляющего автомата (дополнение 2)

Заключение по практической части

В ходе выполнения курсовой работы мной было спроектировано арифметико-логическое устройство, выполняющее алгебраическое сложение и вычитание и проводящее конъюнкцию операндов.

Список литературы

- http://rus.625-net.ru

- http://www.epson.ru

- http://ru.wikipedia.org

- http://www.kramer.ru

- http://www.ixbt.com

- Журнал «Сервисный центр» №10 2000г.

- http://www.oki.ru

8. Архитектура ЭВМ. А.П. Жмакин

СПб.: БХВ-Петербург, 2006. – 320 с.: ил.

ISBN 5-94157-719-2

9. Требования к оформлению курсовых и дипломных работ: Методические указания для студентов специальности 071900 «Информационные системы и технологии» / Сост.: С.П. Бобков, Н.И. Терехин, О.Н. Ястребцев: Иван. Гос. Хим.-технол. ун-т. – Иваново 2003, 24 с.