Лабораторная работа №5. Исследование цифровых систем

Исследование цифровых систем

Цель работы

Целью работы является:

-исследование работы цифровых логических элементов;

-исследование работы дешифратора;

-исследование работы мультиплексора;

-исследование работы триггеров;

-исследование работы счетчиков.

Сведения необходимые для выполнения работы

Перед выполнением работы полезно ознакомиться со следующими вопросами:

-классификация, назначение и особенности

работы логических элементов ;

-принципы построения и режимы работы дешифраторов

и мультиплексоров ;

-классификация, принципы работы и способы включения триггеров ;

-виды счетчиков импульсов, принцип их

работы и особенности применения .

Логические элементы

Цифровым логическим элементом называется физическое устройство, реализующее одну из операций алгебры логики или простую логическую функцию. Схема, составленная из конечного числа логических элементов по определенным правилам, называется логической схемой.

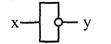

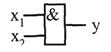

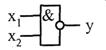

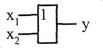

Логические функции, а именно логическое отрицание, логическое умножение (конъюнкция) и логическое сложение (дизъюнкция), на практике могут быть реализованы с помощью определенных логических элементов. В табл. 5.1 представлены логические элементы, их обозначение, схемы и выполняемые функции.

Таблица 5.1.- Логические элементы

| Элемент | Обозначение | Схема | Функция |

| НЕ | ЛН |  |  |

| И | ЛИ |  |  |

| И-НЕ | ЛА |  |  |

| ИЛИ | ЛЛ |  |  |

| ИЛИ-НЕ | ЛЕ |  |  |

| Исключающее ИЛИ | ЛП |  |  |

Примечание: в таблице использованы следующие обозначения:

х - отрицание значения х;

- логическое умножение (конъюнкция);

- логическое умножение (конъюнкция);

- логическое сложение (дизъюнкция).

- логическое сложение (дизъюнкция).

Работу логического элемента принято описывать с помощью таблицы истинности. В ней указываются все возможные значения входных переменных логического элемента и состояния на его выходе в соответствии с выполняемой элементом логической функцией. Логические переменные могут принимать только два значения - 0 или 1. Пример таблицы истинности для логического элемента И приведен в табл.5.2.

Логические схемы, реализующие однозначное соответствие между значениями входных и выходных сигналов, называются комбинационными. К ним относятся дешифраторы и мультиплексоры.

Таблица 5.2 - Таблица истинности элемента И

| Выход Х1 | Выход Х2 | Выход Y | ||

Дешифраторы

Дешифратором называют преобразователь двоичного n-разрядного кода в унитарный 2n - разрядный код, все разряды которого, за исключением одного, равны единице. Дешифраторы бывают полными и неполными. Для полного дешифратора выполняется условие:

, (5.1)

, (5.1)

где n — число входов (обычно n равно 2, 3 или 4); N — число выходов.

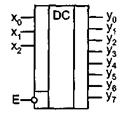

Рисунок 5.1 - Условное обозначение дешифратора 3x8

В неполных дешифраторах имеется п входов, но реализуется N< 2n выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов, будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным.

На рисунке 5.1 изображен дешифратор с n = 3.

На входы х0, х1, х2 можно подать 8 комбинаций логических уровней: 000, 001, 010, ..., 111. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал (0), а на остальных высокий (1). Номер этого единственного выхода, на котором формируется нулевой уровень, соответствует числу N, определяемому состоянием входов х0, х1, х2 следующим образом:  . В общем виде состояние выходного сигнала

. В общем виде состояние выходного сигнала  можно описать следующей системой условий:

можно описать следующей системой условий:

(5.2)

(5.2)

Помимо информационных входов х0, х1, х2, дешифраторы обычно имеют дополнительные входы управления Е. Сигналы на этих входах разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов.

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом- уровень логического нуля. Дешифратор, представленный на рисунке 5.1, имеет один инверсный вход управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

(5.3)

(5.3)

Существуют дешифраторы с несколькими входами управления. Для таких дешифраторов функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора КР555ИД7 с одним прямым входом управления Е1 и двумя инверсными Е2 и ЕЗ функция Е имеет вид:

(5.4)

(5.4)

Мультиплексоры

Мультиплексором называется комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу, определяемому комбинацией логических уровней на адресных входах. Кроме информационных и адресных входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и адресных сигналов.

В зависимости от соотношения числа информационных входов n и числа адресных входов m мультиплексоры делятся на полные и неполные. Если выполняется условие n=2m , то мультиплексор будет полным. Если это условие не выполняется, то есть n<2m, то мультиплексор будет неполным.

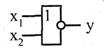

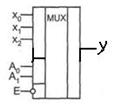

Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На рисунке 5.2 представлен мультиплексор 4 ×1 с инверсным входом разрешения Е и прямым выходом у, представляющий собой половину микросхемы мультиплексора КР555КП12.

Рисунок 5.2 - Условное обозначение мультиплексора 4×1

Выражение для выходной функции такого мультиплексора можно записать в виде:

, (5.5)

, (5.5)

где х0, х1, х2, - информационные входы мультиплексора;

- адресные входы мультиплексора.

- адресные входы мультиплексора.

В общем случае для полного мультиплексора, имеющего n управляющих (адресных) входов и 2mинформационных входов, можно реализовать n входовую логическую функцию. Поскольку каждой комбинации управляющих входов соответствует единственный информационный вход, на него следует подавать требуемое значение логической функции, которое и будет передано на выход мультиплексора.

Триггеры

Триггером называется простейшее устройство, имеющее два устойчивых состояния, переход между которыми происходит в результате процессов, обусловленных наличием в электрической цепи триггера цепей положительной обратной связи.

Два устойчивых состояния триггера обозначаются: Q=1 и Q = 0. В каком из этих состояний окажется триггер, зависит от состояния сигналов на входах триггера и от его предыдущего состояния, иными словами, триггер имеет память. Можно сказать, что триггер является элементарной ячейкой памяти.

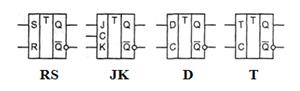

Тип триггера определяется алгоритмом его работы. В зависимости от алгоритма работы триггер может иметь установочные, информационные и управляющие входы. Установочные входы определяют состояние триггера независимо от состояния других входов. В частности, входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS,JK, D и T. Условное обозначение этих триггеров приведено на рисунке 5.3.

Рисунок 5.3 - Условное обозначение триггеров: RS-, JK-, D и T типа

RS- триггеримеет два информационных входа S и R. Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на выходе Q триггера сигнал 1. Наоборот, при сигналах S = 0 и R = 1 сигнал на выходе триггера Q = 0. Функционирование SR-триггера определяется уравнением:

(5.6)

(5.6)

где  - соответственно предыдущее и новое состояния триггера.

- соответственно предыдущее и новое состояния триггера.

Для RS-триггера комбинация S = 1 и R = 1 является запрещенной. После такой комбинации информационных сигналов состояние триггера будет неопределенным: на его выходе Q может быть 0 или 1.

Существуют разновидности RS-триггеров, называемые Е-, R- и S-триггерами, для которых сочетание S = R=1 не является запрещенным. E-триггер при S = R = 1 не изменяет своего состояния  . S -триггер при S = R = 1 устанавливается в состояние Q = 1, а R-триггер в этом случае устанавливается в состояние Q = 0.

. S -триггер при S = R = 1 устанавливается в состояние Q = 1, а R-триггер в этом случае устанавливается в состояние Q = 0.

JK-триггер имеет также два информационных входа J и К. Подобно RS-триггеру, в JK-триггере J и К - это входы установки выхода Q триггера в состояние 1 или 0. Однако в отличие от RS-триггера в JK-триггере наличие J=К=1 приводит к переходу выхода Q триггера в противоположное состояние, JK-триггеры синхронизируются только перепадом потенциала на входе С. Условие функционирования JK-триггера имеет вид:

(5.7)

(5.7)

D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования D-триггера имеет вид:  . Это уравнение показывает, что выходной сигнал

. Это уравнение показывает, что выходной сигнал  изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, то есть с задержкой на один период импульсов синхронизации (Delay - задержка).

изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, то есть с задержкой на один период импульсов синхронизации (Delay - задержка).

Синхронизация D-триггера может осуществляться импульсом или фронтом.

Т-триггер, или счетный триггер, изменяет состояние выхода по фронту импульса на входе С. Кроме входа синхронизации (С), T-триггер может иметь подготовительный вход Т. Сигнал на этом входе разрешает (при Т =1) или запрещает (при Т= 0) срабатывание триггера от фронтов импульсов на входе С. Функционирование T-триггера определяется уравнением:

(5.8)

(5.8)

Из этого уравнения следует, что при T = 1 соответствующий фронт сигнала на входе С переводит триггер в противоположное состояние. Частота изменения потенциала на выходе T-триггера в два раза меньше частоты импульсов на входе С. Это свойство T-триггера позволяет строить на их основе двоичные счетчики. Поэтому эти триггеры и называют счетными. Счетный триггер без входа T ведет себя так же, как и T-триггер при Т= 1.

Счетчики

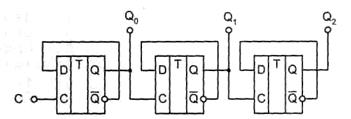

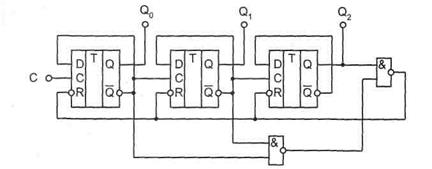

Счетчиком называется устройство для подсчета числа входных импульсов. С поступлением каждого импульса на вход С состояние счетчика изменяется на единицу. Счетчик можно реализовать на нескольких триггерах, при этом состояние счетчика будет определяться, состоянием его триггеров. В суммирующих счетчиках каждый входной импульс увеличивает число на его выходе на единицу, в вычитающих счетчиках каждый входной импульс уменьшает это число на единицу. Наиболее простые счетчики - двоичные. На рис. 5.4 представлен суммирующий двоичный счетчик.

При построении счетчика триггеры соединяют последовательно. Выход каждого триггера непосредственно действует на тактовый вход следующего. Для того чтобы реализовать суммирующий счетчик, необходимо счетный вход очередного триггера подключать к инверсному выходу предыдущего. Для того чтобы изменить направление счета (реализовать вычитающий счетчик), можно предложить следующие способы:

- считывание выходных сигналов счетчика не с прямых, а с инверсных выходов триггеров;

- изменение структуры связей в счетчике путем подачи на счетный вход триггера сигнала не с инверсного, а с прямого выхода предыдущего устройства.

Счетчики характеризуются числом состояний в течение одного периода счета (цикла). Число состояний определяется количеством триггеров k в структуре счетчика. Так, при k = 3 число состояний равно N=23=8 (от 000 до 111).

Рисунок 5.4 - Двоичный суммирующий счетчик

Число состояний счетчика принято называть коэффициентом пересчета КсчЭтот коэффициент равен отношению числа импульсов Nвхна входе к числу импульсов Nвых на выходе старшего разряда счетчика за период счета:

(5.9)

(5.9)

Если на вход счетчика подавать периодическую последовательность импульсов с частотой  , то частота

, то частота  на выходе старшего разряда счетчика будет меньше в Ксч раз:

на выходе старшего разряда счетчика будет меньше в Ксч раз:

(5.10)

(5.10)

Поэтому счетчики можно использовать в качестве делителей частоты, величина Ксч в этом случае будет коэффициентом деления. Для увеличения величины Ксч приходится увеличивать число триггеров в цепочке. Каждый дополнительный триггер удваивает число состояний счетчика и число Ксч. Для уменьшения коэффициента Ксч можно в качестве выхода счетчика рассматривать выходы триггеров промежуточных каскадов. Например, для счетчика на трех триггерах Ксч =8, если взять выход 2-го триггера, то Ксч =4. При этом Ксч всегда будет являться целой степенью числа 2, а именно: 2, 4, 8, 16 и т. д.

Можно реализовать счетчик, для которого Ксч окажется любым целым числом. Например, для счетчика на трех триггерах реализуется Ксч в пределах от 2 до 7, но при этом один или два триггера могут оказаться лишними. При использовании всех трех триггеров можно получить Ксч = 5...7, то есть 22< Ксч <23. Счетчик с Ксч =5 должен иметь 5 состояний, которые в простейшем случае образуют последовательность: {0, 1, 2, 3, 4}. Циклическое повторение этой последовательности означает, что коэффициент деления счетчика равен 5.

Для построения суммирующего счетчика с Ксч =5 надо, чтобы после формирования последнего числа из последовательности {0,1,2,3,4} счетчик переходил не к числу 5, а к числу 0. В двоичном коде это означает, что от числа 100 нужно перейти к числу 000, а не 101. Изменение естественного порядка счета возможно при введении дополнительных связей между триггерами счетчика. Можно воспользоваться следующим способом: как только счетчик попадает в нерабочее состояние (в данном случае 101), этот факт должен быть опознан и повлечь последующую выработку сигнала, который перевел бы счетчик в состояние 000.

Факт попадания счетчика в нерабочее состояние описывается логическим уравнением:

(5.11)

(5.11)

Состояния 110 и 111 также являются нерабочими и поэтому учтены при составлении уравнения. Если на выходе эквивалентной логической схемы F = 0, значит, счетчик находится в одном из рабочих состояний: 0 v l v 2 v 3 v 4. Как только он попадает в одно из нерабочих состояний 5 v 6 v 7, формируется сигнал F= 1. Появление сигнала F= 1 должно переводить счетчик в начальное состояние 000, следовательно, этот сигнал нужно использовать для воздействия на установочные входы триггеров счетчика, которые осуществляли бы сброс счетчика в состояние  . Один из вариантов построения счетчика с Ксч =5 представлен на рисунке 5.5.

. Один из вариантов построения счетчика с Ксч =5 представлен на рисунке 5.5.

Рисунок 5.5 - Схема счетчика с коэффициентом пересчета 5

Рабочее задание

Загрузить программу Work Bench. Схемы включения элементов НЕ, И и ИЛИ приведены на рисунках 5.6-5.10.

2. Включить схему в работу и, изменяя входное напряжение на логическом элементе НЕ, а также напряжение источника Uвх (рис. 6), наблюдать изменение выходного состояния. Напряжение на входе изменять от 1 В до 2 В с шагом 0.5 В, в диапазоне от 2 В до 3 В с шагом 0.2 В, далее до 3 В с шагом 0.5 В. Результаты измерений занести в табл. 5.3, по результатам измерений построить передаточную характеристику логического элемента НЕ (Uвых – f(Uвх)).

Таблица 5.3 - Передаточная характеристика элемента НЕ

| Параметр | Измерено | |||||||||

| Uвх, В | 1.0 | 1.5 | 2.0 | 2.2 | 2.4 | 2.6 | 2.8 | 3.0 | 3.5 | 4.0 |

| Uвых, В | ||||||||||

| Лог. состояние выхода |

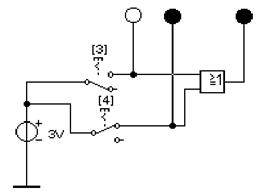

3. Изменяя входные сигналы на входах логических элементов И и ИЛИ при помощи управляемых ключей 1, 2, 3 и 4 (см. рис. 7, 8), наблюдать за изменениями выходных состояний элементов. Результаты наблюдений занести в табл. 5.4.

Таблица 5.4 - Работа элементов И и ИЛИ

| Элемент И | Элемент ИЛИ | ||||||||

| ключ 1 | ключ 3 | ||||||||

| ключ 2 | ключ 4 | ||||||||

| выход | выход |

4. Изменяя входные состояния RS триггера (при помощи ключей R и S), наблюдать изменение выходного состояния. Схема включения RS триггера приведена на рис. 5.9. Результаты наблюдения занести в табл. 5.5.

Таблица 5 Изменение состояния RS триггера

| Сигнал | Состояние | ||||||

| R | |||||||

| S | |||||||

| Выход |

5. Изменяя входные состояния счётного устройства на D триггерах (при помощи ключей R, S и C, см. рис. 5.10), наблюдать за изменениями выходного состояния. Результаты наблюдения занести в табл. 6.

Таблица 6 - Работа счётного устройства

| Сигнал | Состояние | ||||||||

| R | |||||||||

| S | |||||||||

| C | |||||||||

| Q1 | |||||||||

| Q2 | |||||||||

| счёт | |||||||||

|  | ||||||||

| Рисунок 5.6 - Схема включения логического элемента НЕ | Рисунок 5.7 - Схема включения логического элемента И | ||||||||

|  | ||||||||

| Рисунок 5.8 - Схема включения логического элемента ИЛИ | Рисунок 5.9 - Схема включения RS триггера | ||||||||

Рисунок 5.10 Схема счетного устройства на D триггерах

4. Контрольные вопросы

• Что такое логическая переменная и логический сигнал? Какие значения

они могут принимать?

• Что такое таблица истинности? Приведите пример.

• Какие логические элементы составляют базовый набор?

• Какие логические функции выполняет дешифратор?

• Каково назначение входов управления в дешифраторе? Как влияет сигнал

управления на выходные функции дешифратора?

• Функцию какого электрического устройства выполняет мультиплексор для

логических сигналов?

• Каким логическим уравнением описывается работа мультиплексора 2x1 с

управляющим входом?

• Опишите принцип работы RS-, JK-, D- и Т-триггеров.

• Как с помощью JK- и D-триггеров реализовать счетный триггер?

• Почему Т-триггер называют счетным?

• На основе каких триггеров и как можно реализовать двоичный счетчик?

• Что следует для этого сделать?

• Как преобразовать суммирующий счетчик в вычитающий?

• Что такое коэффициент пересчета счетчика?

• Какими способами можно изменить коэффициент пересчета счетчика?

• Каковы основные параметры цифровых микросхем серий ТТЛ и ТТЛШ?

• От чего может зависеть качество полученных результатов?

Номер варианта V выбирается студентом на пересечении строки и столбца таблицы по двум последним номерам своей зачетной книжки, С1 - номер предпоследней цифры; С2 - номер последней цифры:

| С2 С1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| 0 | ||||||||||

| 1 | ||||||||||

| 2 | ||||||||||

| 3 | ||||||||||

| 4 | ||||||||||

| 5 | ||||||||||

| 6 | ||||||||||

| 7 | ||||||||||

| 8 | ||||||||||

| 9 |

Задание к лабораторной работе №2

| № | ЕБ, В | Ек, В | R1, % |

| 1 вариант | |||

| 1,25 | |||

| 2,5 | |||

| 5,0 | |||

| 1,25 | |||

| 2,5 | |||

| 5,0 | |||

| 2 вариант | |||

| 1,1 | |||

| 2,2 | |||

| 4,4 | |||

| 1,1 | |||

| 2,2 | |||

| 4,4 | |||

| 3 вариант | |||

| 1,0 | |||

| 2,0 | |||

| 4,0 | |||

| 1,0 | |||

| 2,0 | |||

| 4,0 | |||

| 4 вариант | |||

| 0,65 | 2,6 | ||

| 1,3 | 2,6 | ||

| 2,6 | 2,6 | ||

| 0,65 | 5,2 | ||

| 1,3 | 5,2 | ||

| 2,6 | 5,2 | ||

| 5 вариант | |||

| 0,9 | |||

| 1,8 | |||

| 3,6 | |||

| 0,9 | |||

| 1,8 | |||

| 3,6 | |||

| 6 вариант | |||

| 0,8 | |||

| 1,6 | |||

| 3,2 | |||

| 0,8 | |||

| 1,6 | |||

| 3,2 | |||

| 7 вариант | |||

| 0,7 | |||

| 1,4 | |||

| 2,8 | |||

| 0,7 | |||

| 1,4 | |||

| 2,8 | |||

| 8 вариант | |||

| 0,6 | |||

| 1,2 | |||

| 2,4 | |||

| 0,6 | |||

| 1,2 | |||

| 2,4 | |||

| 9 вариант | |||

| 1,2 | |||

| 2,4 | |||

| 4,8 | |||

| 1,2 | |||

| 2,4 | |||

| 4,8 | |||

| 10 вариант | |||

| 1,15 | 4,6 | ||

| 2,3 | 4,6 | ||

| 4,6 | 4,6 | ||

| 1,15 | 9,2 | ||

| 2,3 | 9,2 | ||

| 4,6 | 9,2 | ||

| 11 вариант | |||

| 1,05 | 4,2 | ||

| 2,1 | 4,2 | ||

| 4,2 | 4,2 | ||

| 1,05 | 8,4 | ||

| 2,1 | 8,4 | ||

| 4,2 | 8,4 | ||

| 12 вариант | |||

| 0,95 | 3,8 | ||

| 1,9 | 3,8 | ||

| 3,8 | 3,8 | ||

| 0,95 | 7,6 | ||

| 1,9 | 7,6 | ||

| 3,8 | 7,6 | ||

| 13 вариант | |||

| 0,85 | 3,4 | ||

| 1,7 | 3,4 | ||

| 3,4 | 3,4 | ||

| 0,85 | 6,8 | ||

| 1,7 | 6,8 | ||

| 3,4 | 6,8 | ||

| 14 вариант | |||

| 0,75 | |||

| 1,5 | |||

| 3,0 | |||

| 0,75 | |||

| 1,5 | |||

| 3,0 | |||

| 15 вариант | |||

| 0,5 | |||

| 1,0 | |||

| 2,0 | |||

| 0,5 | |||

| 1,0 | |||

| 2,0 |

Задание к лабораторной работе №3

| № варианта | V1=V2, В |

| 9,5 | |

| 9,0 | |

| 8,5 | |

| 8,0 | |

| 7,5 | |

| 7,0 | |

| 6,5 | |

| 6,0 | |

| 5,5 | |

| 5,0 | |

| 4,5 | |

| 4,0 | |

| 3,5 | |

| 3,0 |

Задание к лабораторной работе №4

| № варианта | V1=V2, В | Up1,B | Up2,B | Up3,B | A, B |

| -2,5 | 1,7 | 7,0 | |||

| 9,5 | -2,4 | 1,8 | 6,5 | ||

| 9,0 | -2,3 | 1,9 | 6,0 | ||

| 8,5 | -2,2 | 2,0 | 5,5 | ||

| 8,0 | -2,1 | 2,1 | 5,0 | ||

| 7,5 | -2,0 | 2,2 | 4,5 | ||

| 7,0 | -1,9 | 2,3 | 4,0 | ||

| 6,5 | -1,8 | 2,4 | 3,5 | ||

| 6,0 | -1,7 | 2,5 | 3,0 | ||

| 5,5 | -2,45 | 1,75 | 2,5 | ||

| 5,0 | -2,35 | 1,85 | 2,0 | ||

| 4,5 | -2,25 | 1,95 | 1,5 | ||

| 4,0 | -2,15 | 2,05 | 1,0 | ||

| 3,5 | -2,05 | 2,15 | 0,5 | ||

| 3,0 | -2,0 | 2,1 | 2,0 |

Литература

1. Электротехника и электроника в экспериментах и упражнениях: Практикум по Еlectronics Workbench: В 2 т./ Под общей ред. Д.И. Панфилова – Т.1: Электротехника. – М.: ДОДЭКА, 1999. – 304 с.