Схема электрическая структурная

| Рис. 3. Буфер FIFO. Схема электрическая структурная. |

Для того чтобы разработать принципиальную схему буфера FIFO с регистровой памятью 8сл.×8р. на основе микросхемы КР1533ИР32 (4сл.×4р.), необходимо:

‑ нарастить число разрядов;

‑ нарастить число слов.

Построение блока регистровой памяти.

Увеличение числа разрядов

Задача увеличения числа разрядов заключается в следующем: из данного регистрового файла 4сл.×4р построить регистровую память 4сл.×8р. На рис.4 показан принцип увеличения числа разрядов для рассматриваемой микросхемы КР1533ИР32.

| Рис. 4. Увеличение числа разрядов регистровой памяти с 4сл.×4р. до 4сл.×8р. |

На рис.5 показана эквивалентная схема регистровой памяти 4сл.×8р.

| Рис. 5. Эквивалентная схема регистрового файла 4сл.×8р. |

Увеличение числа слов

Задача увеличения числа слов заключается в следующем: из полученного регистрового файла 4сл.×8р построить регистровый файл 8сл.×8р. На рис.6 показан принцип увеличения числа слов для исследуемого случая.

| Рис. 6. Увеличение числа слов с 4 до 8. |

На рис.6 выходы регистров Q0 …Q7 соединяются монтажным ИЛИ.

На рис.7 показана эквивалентная схема регистрового файла 8сл.×8р.

| Рис. 7. Эквивалентная схема регистрового файла 8сл.×8р. |

Функциональная схема блока регистровой памяти

Перечень используемых микросхем в блоке регистровой памяти:

КР1533ИР32 ‑ 4шт.;

DC – 2 шт.

Построение дешифратора

i 51sR8sAS935IDfeTGuJa7yEdRMNTjkZdgLq7pRPfNV3M//CyAJg6XIgAv9PGy2jqkMKJdA1NXZ5z 3J2QHkz9/i9AkfoWyfamPlyAQhJEEAb7zJC9jefQza2DvoRwx3SBdDEsay3XHWxXZBo9CZrrVybv ECe2DM+tJE17eRFusNVx/rZuerDd67YrGFm4vSjsOcT7zmLX68vZeKO6+yxatVfIj/4BAAD//wMA UEsDBBQABgAIAAAAIQBYGfz52QAAAAUBAAAPAAAAZHJzL2Rvd25yZXYueG1sTI/NTsMwEITvSLyD tUjcqA1UTZXGqRACBEfCz9mNt3FEvA6224S3Z+ECl5FWs5r5ptrOfhBHjKkPpOFyoUAgtcH21Gl4 fbm/WINI2ZA1QyDU8IUJtvXpSWVKGyZ6xmOTO8EhlEqjweU8llKm1qE3aRFGJPb2IXqT+YydtNFM HO4HeaXUSnrTEzc4M+Ktw/ajOXgNhOquGaJ8zO3b++g+193D03LS+vxsvtmAyDjnv2f4wWd0qJlp Fw5kkxg08JD8q+wti4Jn7DRcq2IFsq7kf/r6GwAA//8DAFBLAQItABQABgAIAAAAIQC2gziS/gAA AOEBAAATAAAAAAAAAAAAAAAAAAAAAABbQ29udGVudF9UeXBlc10ueG1sUEsBAi0AFAAGAAgAAAAh ADj9If/WAAAAlAEAAAsAAAAAAAAAAAAAAAAALwEAAF9yZWxzLy5yZWxzUEsBAi0AFAAGAAgAAAAh AGqcKgmOBgAAii4AAA4AAAAAAAAAAAAAAAAALgIAAGRycy9lMm9Eb2MueG1sUEsBAi0AFAAGAAgA AAAhAFgZ/PnZAAAABQEAAA8AAAAAAAAAAAAAAAAA6AgAAGRycy9kb3ducmV2LnhtbFBLBQYAAAAA BAAEAPMAAADuCQAAAAA= ">

| Рис. 8. Эквивалентная схема дешифратора 1‑2. |

При расширении по числу слов были выбраны два дешифратора с УГО (рис.8) и таблицей истинности (табл.1).

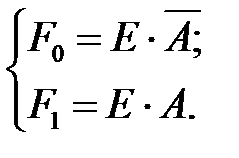

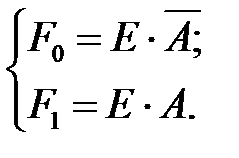

Функционирование дешифратора описывается системой переключательных функций:

Схема электрическая функциональная данного дешифратора представлена на рис.9.

| Рис. 9. Дешифратор. Схема электрическая функциональная |

Перечень используемых микросхем в DC:

КР1533ЛН1 ‑ 1шт.;

КР1533ЛИ1 – 1 шт.