Управляющие автоматы. Сравнительный анализ. АПЛ.

Типы УА.

1. УА с жесткой логикой (запаянной логикой)

2. УА с программируемой логикой (хранимой)

Автоматы с жесткой логикой реализуются на триггерах и электронных логических элементах. Для изменения алгоритма требуется изменение схемы автомата.

УА с программируемой логикой. Микрокоманды задаются с помощью запоминающего устройства, где микрокоманды – двоичные слова, это аналогично слова, хранимым в основной памяти АПЛ.

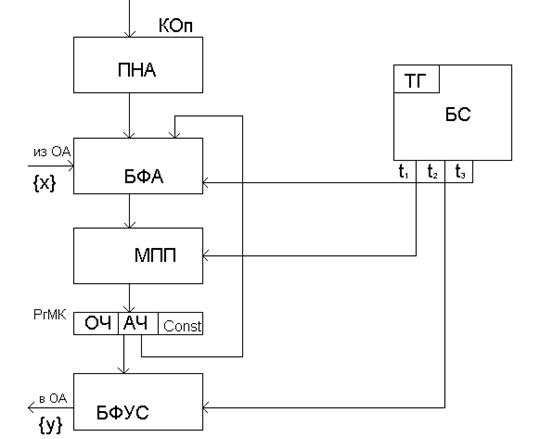

Автоматы с программируемой логикой (АПЛ).

Код операции.

Преобразование Начального Адреса

Блок Формирования Адреса

Микропрограммная Память

Блок Формирования Управляющих Сигналов

Блок Синхронизации

Тактовый Генератор

Микрокоманды описываются в Регистре МК.

Основа автомата – МПП.

ОЧ РгМК – кодируются МК, ОЧ поступает на БФУС. АЧ определяет адрес следующей команды или способ его получения.

Исходное состояние: на входе БФА адрес очередной микрокоманды. По такту t1 чтение МК в РгМК, по такту t2 срабатывает БФУС, по этим сигналам выполняются микрооперации в операционном автомате. При выполнении операции в ОА формируются осведомительные сигналы. Осведомительные сигналы играют роль логических условий. В третьем такте в зависимости от адресной части (АЧ) и значений осведомительных сигналов формируется адрес следующей микрокоманды. И все так продолжается до команды остановки.

При выполнении некоторой программы происходит выборка команд этой программы. Выбор очередной команды происходит по определенной микрокоманде. После выборки команды код операции преобразуется в начальный адрес микропрограммы с помощью ПНА.

Начинается выполнение МК. После окончания микрооперации происходит возврат к команде выборки команд.

10. Кодирование микроопераций и способы адресации в АПЛ.

Способы кодирования микрооперации в АПЛ.

|

3 способа кодирования микрооперации:

1) горизонтальное (унитарное)

2) вертикальное (не убыточное)

3) комбинированное (МК с полевой структурой).

1. Горизонтальный.

y1, y2,…,ym – микрооперации (1 бит для каждой)

m бит – длина операционной части.

Y5= {y1,y3,y8} m=9

|

|

| |

| |

|

|

Т2

2. Вертикальный.

Y1,Y2,…,Ym – набор микрокоианд.

В операционной части кодируются микрокоманды.

Длина операционной части: Lоч={log2(M=1)}.

Имеется также пустая микрокоманда, она кодируется нулями.

|

|

Y1 Y2 … Ym

|

y1 y2 … ym

Недостаток: много микрокоманд→схема шифратора очень сложная. Для упрощения схемы число микроопераций в одной микрокоманде снижается (до 1), при этом шифратор становится ненужным.

Недостаток: снижений производительности, т.к. микрооперации, которые могут выполняться параллельно-выполняются последовательно.

3. Комбинированный (горизонтальный).

Наиболее распространенный способ.

Все множество микроопераций разбивается на подмножества, причем из микроопераций одного подмножества одновременно выполняется не более одной (подмножества несовместимых микроопераций).

Чаще всего разбиение на подмножества происходит по функциональному признаку. Для каждого операционного автомата применяется своя операция.

ALU (сложение, вычитание, и, или,…) одновременно только 1.

Сдвигатель (логический, арифметический, вправо, влево) только 1.

Для каждого подмножества в ОЧ МК выделяется свое поле (поле управления памятью, АЛУ, сдвигатель).

|

T2

T2

|  |  |

{y1} {y2} ……. {yk}

Длина операционной части: Lоч=∑Li

Li={log2(mi+1)}

1) mi=1, mi=2 дешифратор не нужен.

2) Прямое кодовое управление узлами операционного автомата.

Управление узлом осуществляется не узлами операций, а двоичным кодом.

Прямое кодовое управление осуществляется двоичным кодом, поступающим на управляющий вход функционального узла,например, АЛУ, сдвигателя, мультиплексора и т.д. В этом случае дешифраторы в АПЛ не требуется, прямо из регистра команд подается управляющий код.

Способы адресации АПЛ.

1. Принудительная адресация МК.

2. Естественная адресация.

3. Функциональная адресация.

4. Программируемая адресация.

1. Принудительная адресация МК.

Адрес следующей МК задается принудительно (указывается текущая МК), чаще всего используется 2 адреса.

|

В поле Х указывается индекс проверяемого логического условия.

Если условие не проверяется, но не выполняется, переход происходит по адресу А0.

Если условие проверяется и выполняется, то переход происходит по адресу А1.

В случае отсутствия условия поле Х=0.

хх – условие, если хх=0, то А0

если хх=1, то А1

Р2МК

|

|  |  | |||

|

Т3

Т3

хx

хx

|

{х} – сигналы логических условий, из них один хх идет на мультиплексор адреса, синхронизируется работа тактом Т3

МКУ:

МКУ:

х

|

1 2 ……. L

1 2 ……. L

|

|

|

|

|

хх

Возможно использование принудительной адресации:

если х=0, то переход по адресу А

если х=1, то переход по адресу А+1.

2. Естественная адресация.

|

Если условие не проверяется или проверяется, но не выполняется, то следующая микрокоманда выбирается в естественном порядке (прибавляется 1 к адресу текущей МК).

Если условие проверяется и выполняется, то переход происходит по адресу А.

При естественной адресации кроме условных переходов возможен и безусловный. Безусловный переход может кодироваться специальным блоком или некоторым специальным значением поля х.

|

|

| |||

| |||

+1

+1

| |||

| |||

После выборки очередной МК К счетчику прибавляется 1. Если должен быть переход, то содержимое счетчика заменяется полем адреса.

2. Функциональная адресация.

При сакой адресации адрес очередной МК или его часть определяется некоторым внешним источником.

Функциональная адресация применяется также для сокращения числа МК, связанных с условными переходами. Рассмотренные способы адресации позволяют разветвление МК в одной МК не более, чем по двум направлениям, а иногда необходимо большее число направлений.

|

0 0

0 0

1 1

1 1

|

0

0

|

|  |

Первая МК охватывает оператор Y1 и условие х1, но затем должны анализировать условие х2 в двух ветвях, которое охватывает две МК. Тем самым увеличилось число МК, а следовательно и время.

Как можно уменьшить:

|

|

|

Хх1

Хх1

адрес след.МК

Усложнив структуру МК, мы можем получить разветвление на 4 направления. Увеличивается длина МК, занимается память, но не всегда ведь все 4 адреса нужны. Такой подход приводит к чрезмерному увеличению длины МК и не эффективно используется микропрограммной памятью. Поэтому был Придуман другой подход.

|

|

|

Хх2

Хх2

z1

z1

|

| |||||||

|  | ||||||

| |||||||

Xx1 z1 Xx2 z2

ЛС – логическая схема.

Выделяется 2 младших бита адреса a1, a2. Старшая часть адреса А передается в Р2АМК без изменений. Значение младших битов адреса определяются логической схемой.

а1, если условие первое не проверяется (х1=0)

а1, если условие первое не проверяется (х1=0)

α1=

Хх1, если х1≠1

а2 ,если х2=0 (z2=1)

а2 ,если х2=0 (z2=1)

α2=

Xx2, если х2≠0

Основная идея: вместо битов адреса используются значения проверяемых логических условий.

Хх1 Хх2 Адрес МК МК

Хх1 Хх2 Адрес МК МК

|

0 0 А . 00 МКd

0 1 А . 01 MKc

1 0 А . 10 MKb

1 1 А . 11 MKa

Недостатком этого способа является ограничение на размещение МК в памяти и следовательно усложнение программирования и, возможно, направление дублирующих МК (размножение одинаковыхМК).

Пример:

|

0 0

0 0

| |||

| |||

1 1

|

11. Процессоры, характеристики, порядок работы, структура команд и порядок их выполнения.

Процессор:

1. Арифметико-логическое устройство

2. Устройство управления

3. Регистровая (локальная) память

В состав АЛУ входят еще дополнительные регистры (регистры частного, делителя и т. д.), комбинационные схемы (сумматоры и т. д.). В общем случае АЛУ рассматривается как комбинационная часть.

УУ осуществляет адресацию и выборку команд, определение порядка выборки команд и выработку управляющих сигналов для других устройств компьютера (для АЛУ, для себя, для работы с памятью, для обмена с периферийными устройствами).

Регистровая память (РЗУ). Регистры программно доступны, их может использовать программист для написания программ.

Количество их может быть разным. Может быть только один доступный регистр – аккумулятор. В общем случае РЗУ – это группа регистров: регистры общего назначения (РОНы или GPR – General purpose register) и регистры с плавающей точкой (РПТ – FPR – Float Point Register)

Характеристики процессора

1) Производительность (быстродействие). Измеряет количество операций в единицу времени. Среднее время выполнения операций или берётся одна стандартная команда и сколько таких операций за единицу времени выполнится.

2) Объём памяти (и регистровая и основная)

3) Операционные ресурсы (типы обрабатываемых данных, состав операций, способы адресации, система команд).

4) Надежность и достоверность вычислений

Порядок работы процессора при выполнении команд

1. Выборка команды из основной памяти

· Cчетчик команд СК (программный счетчик – PC – Program Counter, указатель команды IP – Instruction Pointer)

· Регистр команд. B него помещается выбранная команда.

· засылка адреса команды в память (в Рг А или на шину адреса)

· чтение из памяти по этому адресу (на шину данных или в регистр данных)

· засылка в Рг К

· инкремент РС (IP) – указание адреса команды, следующей по порядку.

2. Декодирование команды.

Осуществляется с помощью дешифратора или в случае микропрограммируемого устройства осуществляется с помощью преобразователя начального адреса (ПНА).

3. Выборка операндов из основной памяти и/или из РЗУ.

Сначала формируется адрес операндов.

4. Исполнение операции.

5. Запись результата в РЗУ или ОП.

6. Формирование признаков результата (флажков)

Исполнение операции при передаче управления (переходы)

· проверка условия перехода

· вычисление адреса перехода

· загрузка адреса в РС

Структура команд и порядок их выполнения

1-адресная команда:

| КОП | А |

2-адресная команда

| КОП | А1 | А2 |

3-адресная

| КОП | А1 | А2 | А3 |

3-адресная команда:

1) Выборка команды (Instruction Feteh)

2) Выборка операнда по адресу А1

3) Выборка операнда по адресу А2

4) Исполнение операции

5) Запись результата по адресу А3

Двухадресная команда:

А1, А2 – адреса операнда. Один из этих адресов является также адресом результата.

Одноадресная команда:

В случае одноадресных команд предполагается использование в составе процессора регистра-аккумулятора. Кроме арифметических команд должны быть предусмотрены команды загрузки в аккумулятор и запись из аккумулятора в память.

Операция выполняется над операндом аккумулятора и словом из памяти

Загрузка LD (Load)

1) Выборка команды

2) Выборка по адресу А

3) Заись в АС

Арифметическая операция

1) Выборка команды

2) Выборка по адресу А

3) Исполнение операции, например Act[a]

4) Запись в АС

Запись в память St (сохранение)

[A]:=Ac

В Современных системах адреса могут относиться как к регистровой памяти, так и оперативной.

| КОП | R1 | R2 |

| КОП | R1 | А2 |

12. Форматы команд ЭВМ общего назначения

Форматы команд и способы адресации

Форматы команд и способы адресации IBM-370

Регистровая память (РП) – 16 регистров общего назначения по 32 бита и 4 регистра с ПТ по 64 бита

Форматы:

1) RR (регистр регистр)

| КОП | R1 | R2 |

0 7 8 11 12 15

РОН[R1]:=РОН[R1]+РОН[R2]

2) RX (регистро-индексируемая )

| КОП | R1 | X2 | B2 | D2 |

0 7 8 11 12 15 16 19 20 31

адрес 2-го операнда (EA)

адрес 2-го операнда (EA)

EA=РОН[X2]+РОН[B2]+D2

индекс база смещение

Базовый адрес – адрес какой-то области памяти. Индекс – адрес элемента массива относительно некоторого базового адреса.

Такая обработка адреса с использованием базы называется базированием. С использованием индекса – индексированием.

Не всегда нужно использовать базирование и индексирование, тогда, если X2 = 0 - адрес не индексируется, В2 = 0 – не базируется. Если X2 = 0, B2 = 0, то адрес будет равен смещению.

Можно расширить формулу для ЕА:

(X2)+ (B2)+ D2, если X2≠0, B2≠0

(X2)+ (B2)+ D2, если X2≠0, B2≠0

(X2) + D2, если X2≠0, B2=0

ЕА = (B2)+ D2, если B2≠0, X2=0

D2, если B2=0, X2=0

3) RS (регистро-неиндексируемая память)

| КОП | R1 | R3 | B2 | D2 |

|

|

EA =

EA = Поле R3 используется в групповых операциях:

· групповая загрузка

· групповая запись в память

Если, например, R1 = 3, R3 = 5

РОН(R1), РОН(R1+1)… - будут загружены

РОН(3), РОН4, РОН5 - в нашем случае

Если R1=14, R3=2, то будут загружены

РОН14, РОН15, РОН0, РОН1, РОН2

4) SI (память – непосредственный операнд)

Непосредственный операнд – который содержится в самой команде

Непосредственный операнд имеет формат байта, другой операнд определяется адресом EA.

5) SS (память – память)

(Длинна 1,5 слова)

(Длинна 1,5 слова)

CT (Counter) – счётчик.

Используется для передачи цепочки байтов (слов) из одной области памяти в другую.

Счетчик фиксирует количество передаваемых байтов (слов). n+1 – число передаваемых байтов (если в счетчике стоит 0, то передаваться будет 1 байт (слово)).

Форматы команд и способы адресации.

RR (условный переход)

RX

M1 – маска перехода – задает условие перехода.

В формате RR адрес перехода – в РОНе (R2). Регистр с адресом 0 не используется (перехода не будет)

Для RX адрес перехода равен (X2)+(B2)+D2.

Проверяется условие, если условие выполняется, адрес перехода загружается в программу счетчика.

PSW

Program

Status

Word

Установка условия в CC (Cod Counter):

00 результат = 0 (Z)

01 результат < 0 (N или S)

10 результат > 0 (P)

11 переполнение (V)

Маска

Если установлен бит Z, то переход по равенству нулю и т. д.

Если все единицы в маске:

M1=1111 , то переход произойдет при любом из значений (безусловный переход)

М1=0111 – переход, если результат не равен нулю.

М1=1010 – переход, если результат ≥ 0.

Вызов подпрограммы.

При вызове подпрограммы нужно запомнить адрес возврата, чтобы после выполнения подпрограммы вернуться в точку вызова. Адрес возврата запоминается в РОНе R1

Поле выборки команды PC=a+4 – адрес возврата. Последовательность действий для вызова п/п:

РОН(R1):=PC ; адрес возврата

PC:=EA ; адрес подпрограммы

Возврат из подпрограммы:

BP R1 PC:=РОН(R1)

|

- безусловный переход

13. Форматы команд специализированных ЭВМ.

14. Структура 8-разрядного МП и его регистровая модель..

15. Структура 16-разрядного МП и его регистровая модель.

Микропроцессор i80286 существенно отличается от предшествующих процессоров i8086, i8086, i8088 тем, что :

1) представляет собой 4 параллельно работающих устройства, поддерживающих архитектуру МП 16/16/24;

2) имеет раздельные шины данных и адреса;

3) тактовая частота 8, 10, 20 МГц;

4) 4 параллельно работающих устройства позволяют осуществить 4-х ступенчатый конвейер. Это дает возможность ≈ в 65 раз увеличить производительность;

5) микропроцессор i80286 программно совместим с предыдущими и поэтому работает в 2 режимах:

- в реальном режиме, при котором процессор имеет адресное пространство 1Мб

- защищенный режим, при котором адресное пространство увеличено до 16 Мб.

6) i286 работает в мультизадачном режиме;

7) система команд расширена еще на 16 команд;

8) регистровая модель i286 содержит все используемые регистры МП i80186.

Основу i286 составляют 4 устройства:

1) шинный интерфейс;

2) командное устройство;

3) операционное устройство;

4) адресное устройство.

Адресное пространство, которое предназначено для преобразования логического адреса из оперативного пространства в физический адрес, через шинный интерфейс передается на шину адреса. Основное назначение – преобразование логического адреса в физический. При этом если шинный интерфейс не занят выборкой команд, то через него можно по шине данных передавать в оперативное устройство операнды для будущих команд.

24 Адрес

24 Адрес

Данные

Физический 16 Управление

Физический 16 Управление

адрес

операнды

Логические

адреса

результаты

Рис. 5.16. Структурная схема i80286.

Поступающие операнды по шине данных хранятся во внутренних регистрах оперативного устройства. Далее требуется только использовать внутреннюю команду, поэтому большинство команд i286 выполняются за 2-3 такта, которые необходимы только для исполнения команд. Для полного исполнения команды требуется 14 тактов, которые последовательно выполняются всеми 4-мя устройствами. Только после команды передачи управления вся очередь в командном устройстве и шинном интерфейсе сбрасывается, а для выполнения команды, к которой производится обращение, все устройства будут работать последовательно, выполняя следующие операции:

1. выборка команды за 1-3 цикла шины;

2. декодирование;

3. выборка операндов за 1-2 цикла шины и исполнение;

4. вычисление адреса команды или операнды;

Параллельно идет подготовка данных для следующей команды.

Сигналы МП i286

Основные сигналы МП i286 представлены на Рис.5.17, где А23-А0 –двунаправленная тристабильная шина адреса, D15 – D0 двунаправленная тристабильная шина данных ХТ,  CLK – сигнал синхронизации от БИС генератора i82284, fCLK=fкварца (частота). Причем в реальном режиме старшие разряды А23-А20=0000.

CLK – сигнал синхронизации от БИС генератора i82284, fCLK=fкварца (частота). Причем в реальном режиме старшие разряды А23-А20=0000.

Синхронизация Адрес

Синхронизация Адрес

Готовность Данные

Сброс Выбор банка

Немаск. прерыв.

Тип цикла шины

Маск. прерыв.

Захват Состояние шины

Запрос расшир. (на контроллер шины)

Подтверждение Подтв. запроса

Вход занятости Блокировка шины

0,047 мкФ Подтверждение

расширения для i287

Рис.5.17. Сигналы I80286.

Внутри CLK производится деление частоты для формирования внутрипроцессорной тактовой частоты.

RESET, #RDY, NMI, INTR, #BHE, #LOCK – управляемые сигналы. Выполняют те же функции, что и в МПi8086, работающем в максимальном режиме.

HOLD, HLDA – аналогичны сигналам МП i8086 для минимального режима.

M/#IO, #ST1, #ST2 – сигналы состояния цикла шины. Определяют, совместно ли CODE/#INTA тип цикла шины МП.

Таблица 5.2.

| CODE/#INTA | M/#IO | #ST0 | #ST1 | Тип шины данных |

| X 0/1 0/1 X | Подтверждение прерывания Чтение ВУ Запись ВУ Цикла шины нет Останов Чтение ЗУ данные/ кодкоманды Запись ЗУданные/код команды Цикла шины нет |

CAP – для подключения фильтрующего конденсатора.

Сигналы PEREQ, #ERROR, BUSY, PEACK – используются при работе с сопроцессором i286, для расширения МП, то есть подключения сопроцессора i286.

16. Структура МП i486 и его регистровая модель.

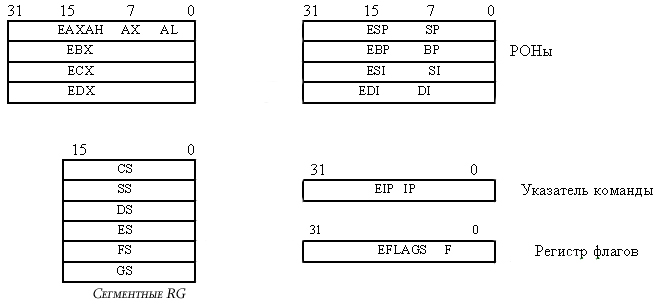

Программная (регистровая) модель процессора i486.

Это доступные программисту регистры, которыми он может пользоваться, используя команды ассемблера.

Существуют 2 подхода – все регистры универсальны;

- есть специализация (Intel)

В i486 объединено лучшее из этих двух подходов: есть специализация, но могут быть и заменены на другие регистры, но это надо дополнительно указать в команде. Если использовать специализацию регистров по умолчанию, то программа (ее объективный код) сокращается.

В программной модели i486 31 регистр (16 пользовательских и 15 системных).

1. Пользовательские RG i486

РОНы - 8шт. по 32 разр. для хранения данных или адресов (E-EXTENDET).

EAX – 32; AX – 16, AL и АН - 8. Старшие 2 байта отдельно адресовать нельзя. Эти 4 RG работают байтами, словами и двойными словами. Они универсальны, но имеют специализацию.

EAX/AX/AL - Аккумулятор. (промежуточные данные, множимое, делимое, IN,OUT, BCD). EBX/BX/BL – Base – базовый. Для указания базового (начального) адреса массива

ECX – Counter – счетчик. Циклы, сдвиги, цепочки.

ЕDX – Data – данные. Промежуточные данные, множитель, делитель, адреса портов в командах IN/OUT

ESP – Stack Pointer – указатель стека (PUSH, POP, CALL, RET, IRET) Адресует вершину стека в текущем сегменте.

EBS – Base Pointer - используется при адресации данных в стеке (при подпрограммах).

ESI – Source Index – регистр адреса текущего элемента цепочки источника.

EDI – Destination Index – регистр адреса текущего элемента приемника.

Сегментные регистры

CS, SS, DS, ES – сохранились с 8086 (1810), но теперь задают не физический адрес сегмента 64 кб, а косвенно через дескрипторную таблицу. Она для каждого сегмента задает: базовый адрес, размер(limit), права доступа(какие программы и в каких операциях могут обращаться к конкретному сегменту).

CS – сегментный регистр кода определяет текущий сегмент, где хранится программа (коды команды).

SS – сегментный регистр стека задает текущий сегмент памяти, где находится стек. Вершина стека – ESP.

DS – регистр, адресующий сегмент с данными.

ES, FS + GS – дополнительные сегменты регистра данных.

16 разрядное слово в сегментном регистре – «селектор». Машина работает с данными сегментами пока не поменяется селектор. Форматы и функции селекторов в R и P режимах разные (всего 3 режима R,P,V).

Каждый сегмент имеет базовый адрес. Для адресации внутри к нему прибавляется 32 – битное смещение(offset).

Указатель команды IP

Предназначен для адресации команд внутри текущего сегмента кода. После выборки очередной команды в IP автоматически устанавливается адрес следующей команды. При опережающей выборки (486) из ОП читается выровненный блок с 4-мя младшими нулями в адресе не учитывая границы между командами.

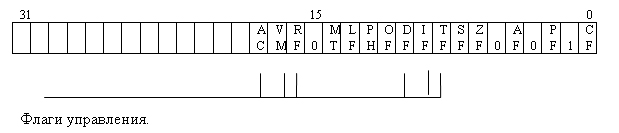

Регистр флагов. FLAGS.

8 флагов состояния + 6 флагов управления.

Флаги состояния фиксируют признаки результатов операций. (не всех - MOV)

CF (Carry) – арифметическая операция вызвала перенос (+), заем (-) из старшего бита

(31, 15, 7)→СF=1. Есть команды установки этого флага и его инверсии.

PF - паритет (четность). Если в младшем байте кол. 1 четное →=1.

AF – (Auxiliary) – вспомогательный перенос из младшей тетрадыA Для десятичной арифметики. Программно не доступен.

ZF (Zero)

SF (Sign) – копирует знак (31, 15, 7)

OF (Overfrow)

IOPL – (Input/Output Prevelege Level ) - Уровень привилегий ввода-вывода.