Модуль последовательного асинхронного интерфейса sci08

Контроллер последовательного асинхронного интерфейса SCI предназначен для обмена с устройствами управления верхнего уровня. Модуль SCI08 обладает следующими характеристиками:

•поддерживает полнодуплексный режим обмена данными:

•реализует стандартный протокол асинхронного обмена с длиной кадра в 10 или 11 бит;

•подсистема передатчика реализует режим вставки бита паритета, подсистема приемника автоматически контролирует соблюдение логики паритета в принятом байте данных;

•позволяет программно настраивать частоту обмена, причем в формировании сетки ча

стот модуль таймера TIM08 не задействован; частота обмена программируется в соот

ветствии с формулой

где NP= 1, 3,4,13; NS = 2n, n = 0 ÷7; максимальная скорость обмена составляет 131 Кбит/с;

•имеет независимые биты разрешения работы приемника и передатчика;

•генерирует запросы на прерывание с раздельными векторами по окончании передачи

байта, завершению приема очередного байта и при диагностировании ошибок приема

байта;

•генерирует 4 флага нарушения режима работы: при переполнении приемника, при возникновении шума на линии в процессе приема, при нарушении формата принимаемого кадра, при нарушении логики паритета; каждое из перечисленных событий формирует запрос на прерывание; реализуется раздельное маскирование всех указанных событий нарушения режима работы;

•имеет встроенные аппаратные средства для организации работы в локальной сети;

•позволяет реализовать «замкнутый» режим работы, при котором передаваемые данные без внешних коммутаций поступают на вход приемника;

•имеет опцию изменения полярности передаваемых данных.

Контроллер SCI08 обслуживается двумя выводами: TxD - линия передачи данных; RxD - линия приема данных. Обслуживание модуля SCI08 является альтернативной функцией линий порта РТЕ (см. рис. 4.44). Если бит разрешения работы модуля ENSCI в регистре SCC1 установлен, то независимо от значения соответствующих битов регистра, направления передачи порта ввода/вывода, его линии назначаются для работы в составе контроллера SCI08.

Принцип действия модуля SCI08 аналогичен рассмотренному принципу действия

модуля типа UART. По сравнению с рассмотренным ранее последовательным портом

МК MCS-51 модуль SCI08 отличает значительно более сложная функциональная схема,

которая реализует логику паритета, а также диагностирует пять типов ошибок приема,

позволяя существенно повысить надежность обмена данными. Соответственно увеличилось и число регистров специальных функций, которые обслуживают модуль. Однако протоколы обмена и базовые алгоритмы функционирования модуля остались неизменными. Аппаратные средства модуля SCI08 делят на две подсистемы: приемника и передатчика. Основу каждой подсистема составляют сдвиговый регистр и буферный регистр

данных (см. рис. 4.19).

Различают два состояния подсистемы передатчика:

1)активное состояние или состояние передачи данных, которое характеризуется периодическим появлением на линии TxD сигнала низкого логического уровня; даже если все биты данных передаваемого кадра равны 1, то линия TxD будет находиться в «0» в течение интервала передачи стартового бита; в состоянии передачи данных в буферном регистре или в сдвиговом регистре обязательно присутствуют еще не переданные данные;

2)состояние ожидания (IDLE), которое характеризуется наличием сигнала высокого

логического уровня на линии TxD в течение не менее 10 или 11 тактов работы передатчика (для 10- и 11-битового кадра соответственно); передатчик переходит в состояние ожидания, если в буферном регистре данных и в сдвиговом регистре новые данные для передачи отсутствуют.

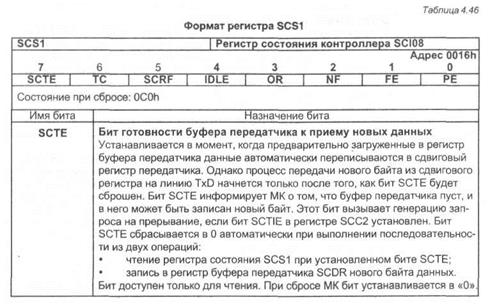

Передача данных от МК к другому устройству инициируется посредством записи байта данных в буферный регистр передатчика по адресу регистра данных SCDR. Аппаратные средства передатчика загружают содержимое буферного регистра данных в сдвиговый регистр. Одновременно устанавливается флаг SCTE (флаг очистки регистра буфера данных в регистре SCS1), который информирует МК о том, что буферный регистр передатчика пуст, и в него могут быть загружены новые данные. Если следующий байт данных для передачи будет загружен в буферный регистр SCDR до завершения передачи предыдущего байта, то нарушения в работе передатчика не произойдет. Второй байт данных будет сохраняться в буферном регистре до тех пор, пока передача предыдущего байта не будет завершена. Следует иметь в виду, что копирование содержимого буферного регистра в сдвиговый регистр под управлением аппаратных средств не сопровождается автоматическим началом передачи этого байта данных. Процесс передачи нового байта из сдвигового регистра на линию TxD начнется только после того, как бит SCTE будет сброшен. Для достижения последнего необходимо выполнить две операции:

1)прочитать регистр состояния SCS1 при установленном бите SCTE;

2)записать в регистр буфера передатчика по адресу SCDR новый байт данных.

Тогда под управлением генератора скорости передачи GT биты предыдущего байта данных начнут последовательно передаваться из сдвигового регистра на вывод TxD.

После завершения передачи пакета обмена, когда в сдвиговом и буферном регистрах не осталось данных для передачи, устанавливается в «1» бит ТС. Флаги очистки буфера данных SCTE и окончания передачи ТС имеют независимое маскирование (биты SCT1E и TCIE регистра SCC2 соответственно). Если прерывания по этим запросам разрешены, то любой из триггеров генерирует запрос на прерывание. Рассматриваемые запросы объединяются по «ИЛИ» и обслуживаются по единому вектору прерывания от передатчика модуля SCI08 (см. табл. 4.31).

Формат кадра передаваемых данных определяется значением бита М в регистре управления SCC1. Если М = 0, то обмен осуществляется с использованием 10-битового кадра . Сдвиговый регистр передатчика автоматически настраивается на 10-разрядный формат, в младшем и старшем разрядах сдвигового регистра устанавливаются логические уровни стартового и стопового битов (см. рис. 4.20). Если М = 1, то используется 11-битовый кадр обмена (см. рис. 4.21). Сдвиговый регистр настраивается на 11-разрядный формат. Недостающий бит данных D8 заполняется значением Т8 из регистра управления SCC3, которое должно быть определено программой до записи в буферный регистр восьми младших бит передаваемого слова. Значение бита М определяет формат кадра обмена как для приемника, так и для передатчика. Поэтому обмен в дуплексном режиме возможен только с одинаковым форматом кадра.

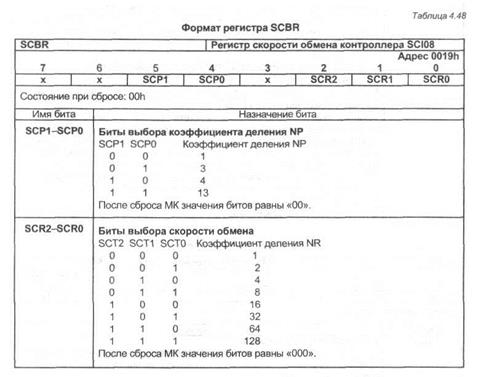

Скорость передачи данных, так же как и скорость приема, определяется собственным генератором модуля SCI08. Этот генератор состоит из двух делителей частоты тактирования межмодульных магистралей fВUS: предварительного с коэффициентом деления NP и основного с коэффициентом деления NS. Скорость обмена данными следует определить в формуле:

где NP - коэффициент деления предварительного делителя, NP = 1, 3, 4,13; NS - коэффициент деления основного делителя, NS= 1, 2, 4, 8, 16, 32, 64, 128.

Значения коэффициентов NP и NS определяются установкой соответствующих разрядов в регистре скорости передачи SCBR.

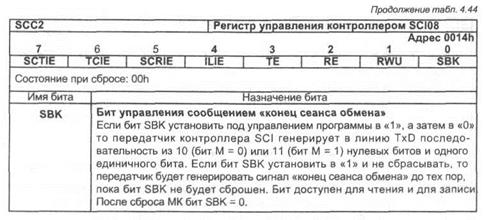

Передатчик модуля SCI08 реализует режим генерации сигнала «конец сеанса обмена» (сигнал «Break»), который состоит из 10 или 11 нулей, и в мультимикропроцессорных системах обозначает конец сеанса обмена между двумя устройствами. Для генерации сигнала «конец сеанса обмена» необходимо установить бит SBK в регистре управления SCC2.

Основные элементы приемника - сдвиговый регистр, 8-разрядный буферный регистр данных, схема мажоритарной логики для формирования значения очередного принимаемого бита, схема детектирования условия вывода приемника из режима ожидания, логический блок управления. Различают два состояния подсистемы приемника:

1)активное состояние, которое характеризуется периодическим формированием

байта данных из последовательности битов на входе RxD, копированием принятого

байта в буферный регистр данных приемника с одновременной установкой в «1» бита

завершения приема данных SCRF;

2)состояние ожидания, в котором также реализуется преобразование последовательного кода на входе RxD в параллельный код в сдвиговом регистре, но копирование принятого байта в буферный регистр данных приемника и установка бита завершения приема SCRF выполняется только тогда, когда значение принятого слова удовлетворяет одному из условий выхода из режима ожидания.

Формат кадра принимаемых данных определяется значением бита М в регистре управления SCC1. При М = 0 обмен осуществляется 10-битовыми кадрами, при М = 1 используется 11-битовый кадр обмена. В последнем случае сдвиговый регистр настраивается на 11-разрядный формат. Бит данных D8, который не помещается в разрядную сетку буферного регистра данных приемника, записывается в разряд R8 регистра управления SCC3.

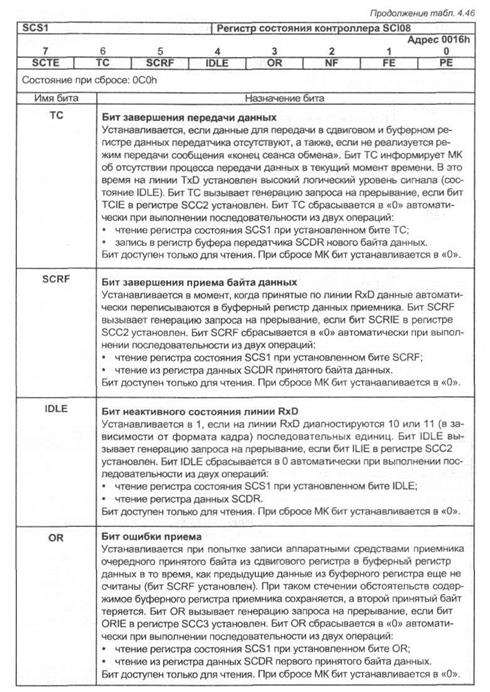

Блок логики управления подсистемы приемника детектирует наличие на входе RxD последовательности из не менее чем одного стопового бита, а затем стартового бита, и начинает формирование слова данных посредством выполнения под управлением генератора скорости передачи GR сдвиговых операций. Значение старшего бита на каждом такте работы сдвигового регистра определяет схема мажоритарной логики. Эта схема производит три выборки уровня сигнала на входе RxD в течение одного такта работы, значение старшего бита определяется по правилу «два из трех». Момент окончания формирования слова в сдвиговом регистре отмечается установкой в «1» триггера завершения приема SCRF в регистре SCS1. Одновременно принятые данные записываются в буферный регистр данных приемника, который доступен для чтения по адресу SCDR. Бит SCRF по существу является флагом готовности данных приемника, он информирует МК о том, что произошел прием очередного слова данных, и его следует переместить в память МК. Бит SCRF может быть считан программно, а если прерывания от приемника разрешены (бит SCRIE регистра управления SCC2 равен «1»), то генерируется запрос на прерывание от приемника модуля SCI08. Сброс бита готовности данных приемника осуществляется в процессе выполнения двух операций:

• чтения регистра состояния SCS1 при установленном бите SCRF;

• чтения регистр данных приемника SCDR.

Нетрудно заметить, что именно эта последовательность операций должна быть выполнена при считывании очередного принятого по линии RxD байта в память МК.

Если бит SCRF находится в «1», т. е. байт данных принят и находится в буферном регистре приемника, то подобная ситуация не препятствует процессу приема в сдвиговый регистр приемника следующего байта данных. Необходимо только, чтобы до завершения приема последующего байта данных предыдущий байт был считан из буферного регистра приемника. Если этого не произошло, то аппаратные средства блокируют запись нового байта в буферный регистр приемника, поэтому новый принятый байт будет потерян. Одновременно устанавливается бит нарушения работы OR в регистре SCS1 (Overrun - попытка перезаписи). Установленный в «1» бит OR может вызывать генерацию запроса на прерывание, если прерывания именно по этому событию разрешены (бит ORIE в регистре SCC3 равен «1»).

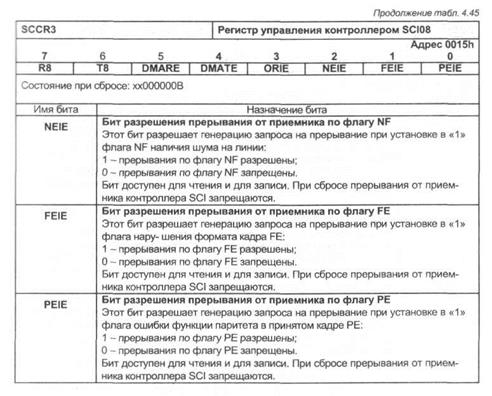

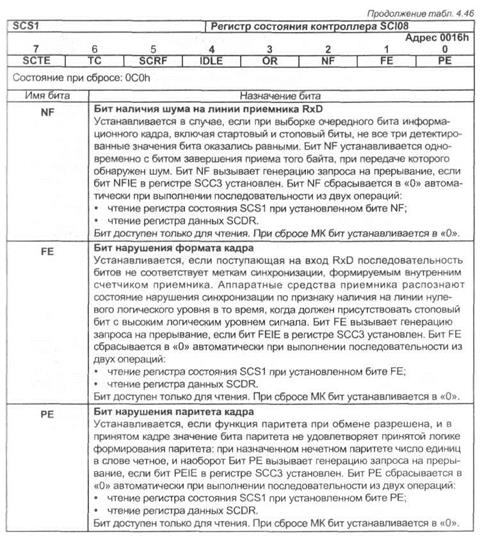

Аппаратные средства приемника сообщают пользователю о наличии шума на линии RxD при приеме каждого байта данных: бит NF регистра SCS1 устанавливается в «1», если при определении значения хотя бы одного из битов кадра обмена, включая стартовый и стоповый биты, не все три выборки сигнала были равны. Установленный в «1» бит NF может вызывать генерацию запроса на прерывание, если прерывания именно по этому событию разрешены (бит NEIE в регистре SCC3 равен «1»). Если следующий принятый байт не содержит признака шума на линии, то бит NF не сбрасывается автоматически. Условия сброса бита NF указаны в табл. 4.46.

Аппаратные средства приемника также распознают нарушение формата кадра обмена: бит FE регистра SCS1 устанавливается в «1», если на линии RxD присутствует сигнал низкого логического уровня в то время, когда должен присутствовать столовый бит с высоким логическим уровнем. Подобная ситуация может возникнуть, если скорости обмена приемника и передатчика не совпадают, или если принимается специальный сигнал «конец сеанса обмена». Бит FE может вызывать генерацию запроса на прерывание, если прерывания именно по этому событию разрешены (бит FEIE в регистре SCC3 равен «1»).

В процессе приема каждого байта информации в формате 11-битового кадра аппаратные средства приемника автоматически производят контроль бита паритета. Управление функцией паритета осуществляется с использованием битов PEN и РТУ регистра SCC1. Если функция контроля паритета разрешена, то бит РЕ в регистре SCS1 устанавливается в «1», если в принятом байте данных вычисленный бит паритета не совпадает со значением принятого бита паритета. Установленный бит РЕ может генерировать запрос на прерывание, если прерывания по событию несовпадения паритетов разрешены (бит PEIE в регистре SCC3 равен «1»).

Запросы на прерывание, сформированные признаками ошибки приема (триггеры OR, NF, FE, РЕ) объединены по «ИЛИ» и обслуживаются по одному вектору прерывания (см. табл. 4.31).

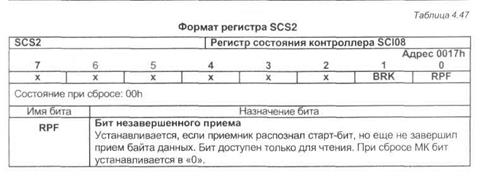

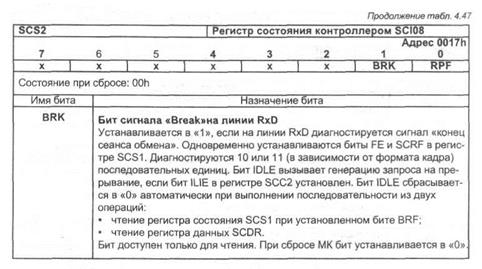

Неактивное состояние линии RxD, которое характеризуется наличием на линии 10 или 11 (в зависимости от формата кадра) последовательных единиц, отмечается установкой бита IDLE регистра состояния SCS1. Неактивное состояние линии RxD свидетельствует о том, что передатчик другого устройства, которое выставляет данные на линию RxD, находится в состоянии ожидания IDLE. Бит IDLE может быть считан программно, но может также генерировать запрос на прерывание, если эти прерывания разрешены (бит ILIE в регистре управления SCC2 равен «1»). Вектор обслуживания запроса по флагу IDLE совпадает с вектором обслуживания приемника модуля SCI08.

Бит RWU в регистре управления SCC2 переводит приемник модуля SCI08 в режим ожидания. Этот режим позволяет организовать протокол обмена локальной управляющей сети МК. В режиме ожидания приемник продолжает преобразование последовательного кода на входе RxD в параллельный код в сдвиговом регистре. Однако формирование признаков SCRF, IDLE, OR, NF, FE, PE приемник не производит, и принятые данные в буферный регистр не копируются. Определено два способа перевода приемника из режима ожидания в активный режим работы:

• поступление последовательности битов с установленным в «1» маркером адреса; в качестве маркера адреса используют старший значащий бит; поэтому, для 10-битового кадра бит D7 должен быть равен «1», чтобы приемник вышел из состояния ожидания, для 11-битового кадра - бит D8.;

• нахождение линии RxD в неактивном состоянии IDLE.

Выбор способа «пробуждения» приемника определяется предварительной установкой бита WAKE в регистре управления SCC1. При диагностировании на входе RxD одной из двух указанных последовательностей приемник выходит из состояния ожидания, устанавливает бит готовности данных SCRF и копирует принятые данные в буферный регистр SCDR. Бит RWU автоматически сбрасывается, логика формирования бита IDLE не работает. Она начнет функционировать только при поступлении следующего байта в активном режиме работы приемника. На практике при организации локальных сетей чаще используется первый способ «пробуждения». Тогда младшие 7 или 8 бит данных первого принятого в процессе «пробуждения» слова содержат в себе адрес МК, с которым будет производиться обмен. Программа обслуживания прерывания по запросу от приемника сравнивает принятый адрес с собственным и, если адреса не совпадают, снова переводит приемник в режим ожидания. В случае равенства адресов приемник остается в активном режиме работы и участвует в сеансе обмена.

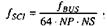

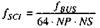

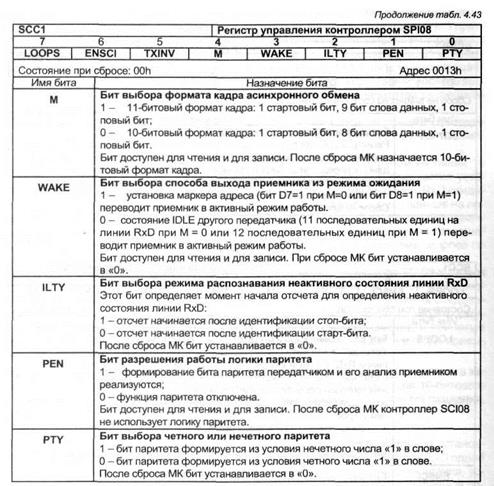

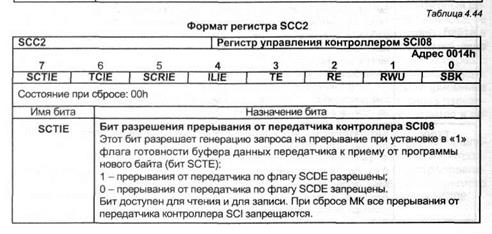

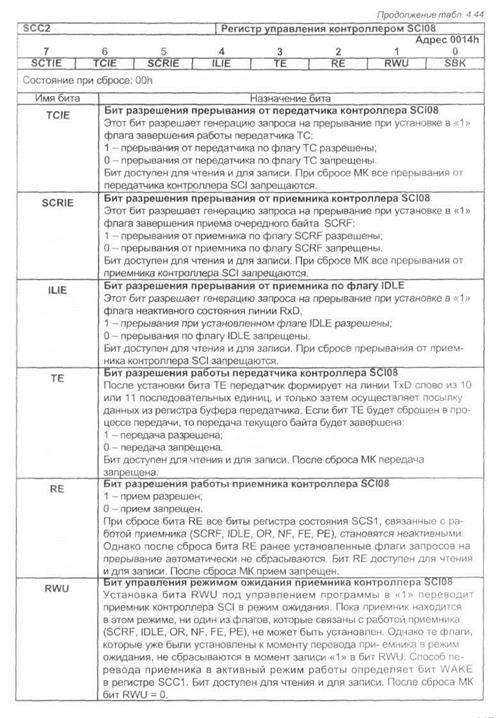

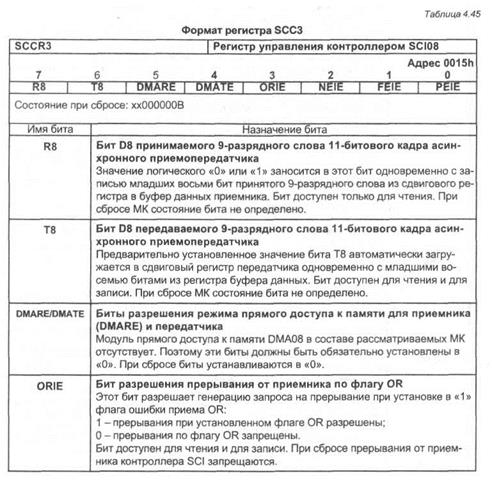

Программно-логическая модель модуля SCI08 включает семь регистров специальных функций: SCDR - регистр данных порта SCI08; SCC1 - регистр управления контроллером SCI08; SCC2 - регистр управления контроллером SCI08; SCC3 - регистр управления контроллером SCI08; SCS1 - регистр состояния контроллера SCI08; SCS2 - регистр состояния контроллера SCI08; SCBR - регистр скорости обмена контроллера SCI08.

|

Форматы этих регистров представлены в табл. 4.42 -4.48.

|

|

|

|

|

|

|

|

|

|

|

|

|

РАЗВИТИЕ СЕМЕЙСТВА НС08

Семейство 8-разрядных МК НС08 активно развивается в следующих направлениях.

•На базе уже отработанного процессорного ядра появляются различные модели МК,

которые интегрируют на кристалле ПЗУ от 1,5 до 60 Кбайт, и широкий набор периферийных модулей. Поскольку объем прикладной программы управления в большинстве случаев соотносится с необходимым набором периферийных модулей, то в составе семейства НС08 присутствуют как очень простые МК в корпусах с 16 и 20 выводами с малым объемом резидентного ПЗУ и небольшим набором периферийных модулей, так и сложные МК с большим объемом ПЗУ программ и широким набором периферийных модулей. Таким образом, на основе одного процессорного ядра пользователю предоставляется широкий ряд моделей, на основе которого могут быть решены любые прикладные задачи для 8-разрядных МК.

•Постоянно пополняется библиотека периферийных модулей семейства. Появляются

новые модули встроенного АЦП с увеличенным числом разрядов и меньшим временем преобразования, контроллеров последовательных интерфейсов USB и CAN, новые более совершенные модули FLASH ПЗУ.

•Повышается производительность центрального процессора путем увеличения частоты тактирования.

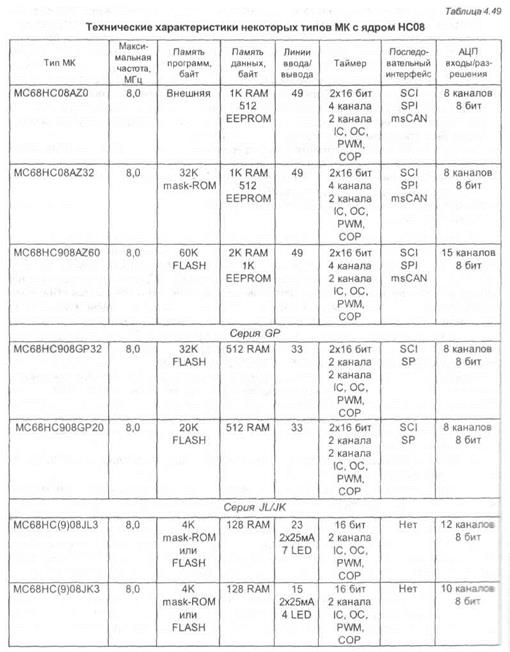

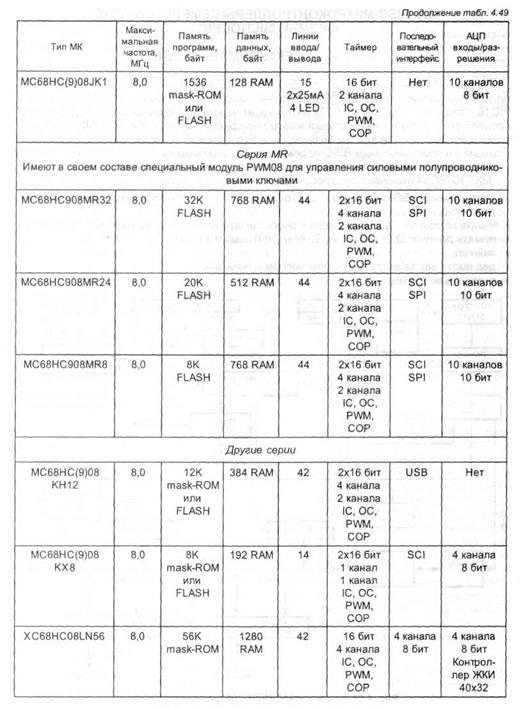

В конце 2000 г. семейство НС08 насчитывало 17 моделей МК (табл. 4.49). В настоящее время продолжают появляться новые модели. Для удобства пользователя МК семейства НС08 объединены в серии. Каждая серия имеет буквенное обозначение: HC08AZ, HC08GP и др. (МК семейства НС08, серия AZ, серия GP). МК, принадлежащие к одной серии, имеют одинаковый набор периферийных модулей, но различаются объемом и типом встроенной памяти, числом каналов в том или ином периферийном модуле, нагрузочной способностью выводов портов, параметрами модуля формирования тактовой частоты, напряжением источника питания, типом корпуса ИС. Серии МК в составе семейства НС08 только нарождаются. В настоящее время оформились шесть семейств: HC08AZ, HC08AS, HC08GP, HC08MR, HC08JK/JL и НС08КХ.

Наибольшее развитие в настоящее время получила серия AZ. Это обусловлено наличием в составе семейства контроллера локальной промышленной сети с протоколом CAN, которая приобретает все большее распространение в системах промышленной автоматики и автомобильной электроники. МК серии AZ представляют собой верхний уровень семейства НС08: предельно реализуемая для CPU08 резидентная память и широкий набор периферии.

К «среднему классу» следует отнести семейство GP с его представителем HC908GP32, рассмотренным выше, и HC908GP20.

Нижний уровень семейства НС08 представлен пока тремя маловыводными моделями - HC(9)08JL3, HC(9)08JK3 и HC(9)08JK1, которые выполнены в корпусах с 28 и 20 выводами. Эти МК имеют две линии вывода с повышенной нагрузочной способностью (25 МА), 7/4 линий предназначены для непосредственного подключения светодиодов. Спектр применения МК HC(9)08JL3/JK3/JK1 - устройства локального управления, не требующие сопряжения с управляющим устройством верхнего уровня. МК HC(9)08JL3/JK3/ JK1 выпускаются как с масочным ПЗУ (HC08JL3/JK3/JK1), так и с модулем FLASH ПЗУ (HC908JL3/JK3/JK1).

Кроме МК общего применения, в состав семейства НС08 включены специализированные микроконтроллеры: HC908MR32, HC908MR24, HC908MR16 и HC908MR8-для управления преобразователями частоты электропривода и другими типами устройств силовой электроники, HC08LN56 -для управления панелями ЖКИ индикаторов; НС(9)08КН12 и HC(9)08JB8 - для управления компьютерной периферией на основе шины USB.

|

|

4.4. RISC-МИКРОКОНТРОЛЛЕРЫ СЕМЕЙСТВА Р1С16 ФИРМЫ «MICROCHIP»

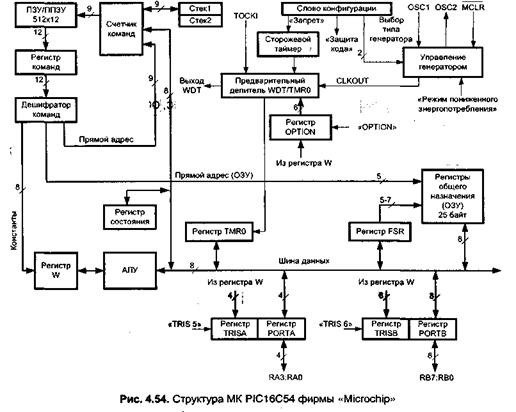

АРХИТЕКТУРА МК PIC16С54

На рис. 4.54 приведена структура МК PIC16C54. Серия Р1С16С5х («х» - номер модели, для рассматриваемого МК PIC16С54 х = 4) объединяет самые простые МК семейства PIC16. Каждый МК серии Р1С16С5х интегрирует на кристалле высокопроизводительное процессорное ядро и минимальный набор периферийных модулей. Так, МК PIC16C54 размещается в корпусе всего с 18 выводами. Его изучение позволит вам познакомиться с самым распространенным RISC-ядром в секторе 8-разрядных МК, не осложняя описание множеством регистров специальных функций периферийных модулей.

МК PIC16C54 включает следующие функциональные блоки:

•центральный RISC-процессор PIC16; разрядность обрабатываемого слова - 8 бит, число команд - 33;

•память программ: 512 12-разрядных ячеек памяти однократно программируемого ПЗУ;

•память данных: ОЗУ емкостью 25 однобайтовых ячеек памяти;

•таймер;

•два порта ввода/вывода с общим числом линий, равным 12;

•сторожевой таймер.

МК семейства Р1С16 используют гарвардскую архитектуру, основанную на концепции раздельных магистралей и областей памяти для команд и для данных. Разделение магистралей позволяет увеличить разрядность команды по сравнению с разрядностью данных. В МК Р1С16С5х формат команды составляет 12 бит, в то время как разрядность слова памяти данных равна одному байту. Все без исключения команды МК PIC16 являются однословными, т. е. длина кода любой команды равна 12 бит. Двухступенчатый конвейер обеспечивает одновременную выборку и исполнение команд. Все команды, кроме команд передачи управления, выполняются за один машинный цикл. Длительность цикла составляет 200 не при частоте тактирования fXCLK = 20 МГц (f Вus = f XCLK/4).

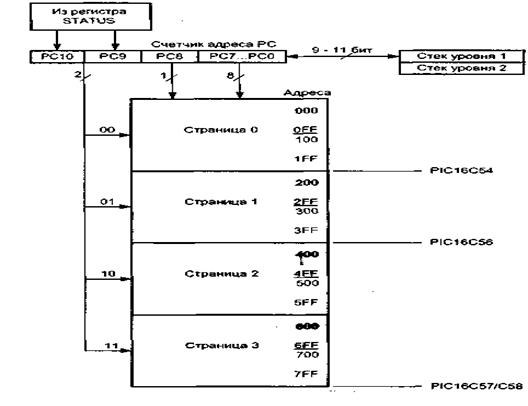

Адресное пространство памяти программ МК Р1С16С5х делится на страницы (банки) по 512 ячеек в каждой (рис. 4.55). Прямая адресация памяти программ возможна только в пределах одной страницы. Доступ к памяти свыше 512 ячеек осуществляется после переключения под управлением программы указателя страницы. В качестве указателя используются биты РА1:РАО регистра признаков центрального процессора, который в МК PIC16 носит название STATUS. Рассматриваемая модель МК PIC16C54 имеет всего 512 ячеек памяти программ, т. е. использует только нулевую страницу адресного пространства. Соответственно и разрядность счетчика адреса PC для данного МК равна 9. В других моделях серии Р1С16С5х используется до 4 страниц памяти программ, тогда разрядность счетчика адреса PC составляет 11 бит. Причем младшие 9 бит работают в режиме двоичного счетчика, адресуя 512 ячеек памяти в пределах каждой страницы. А старшие два разряда устанавливаются только по значению битов РА1 РАО регистра STATUS.

Рис. 4.55. Распределение адресного пространства ПЗУ программ для МК Р1С16С5х

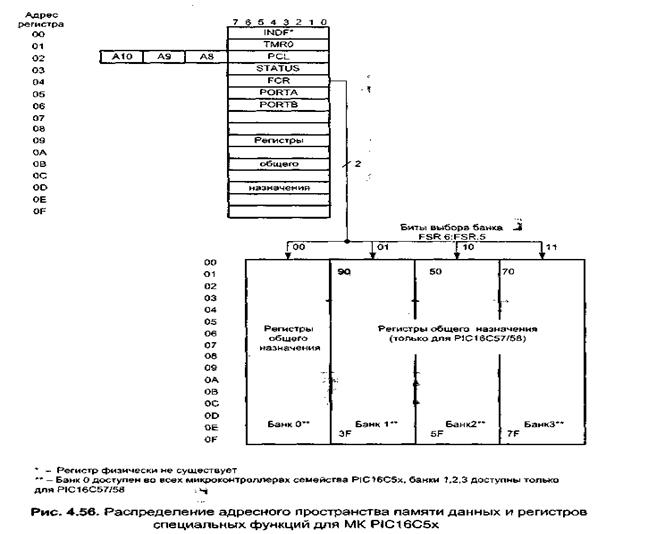

Адресное пространство оперативного запоминающего устройства объединяет регистры специальных функций и регистры общего назначения. Карта памяти данных МК Р1С16С5х представлена на рис. 4.56.

Память данных разбита на 4 банка. В нулевом банке 32 ячейки памяти, в остальных трех банках -по 16 ячеек. Номер используемого банка задают разряды FSR.6 и FSR.5 регистра косвенной адресации FSR (00 - банк 0, 01 - банк 1, 10 - банк 2,11- банк 3). Обратите внимание, что младшие 16 адресов в банках 1, 2 и 3 недоступны. При обращении по адресам, принадлежащим недоступным областям, эти адреса будут отображаться на соответствующий адрес банка 0: например, по адресам 21 п, 1 h, 61 h будет считываться одна и а же ячейка памяти с адресом 01 h.

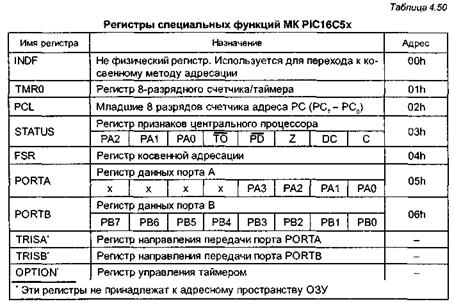

Рассматриваемый МК PIC16C54 имеет всего один банк оперативной памяти. Адресное пространство из 32 ячеек памяти делится следующим образом: диапазон адресов с 00h по 06h принадлежит адресам регистров специальных функций, адреса с 07h по 1Fh используют 25 ячеек памяти общего назначения. В описании системы команд и те и другие именуются регистрами общего назначения в противовес рабочему регистру центрального процессора W, который по функциональному назначению близок к аккумулятору. Для обращения к регистрам специальных функций и просто к ячейкам памяти используются одни и те же способы адресации: прямая адресация и косвенная с использованием регистра косвенной адресации FSR. Кроме того, каждый бит любой ячейки памяти данных доступен с использованием одной из 4 команд битового процессора. Перечень регистров специальных функций МК Р1С16С5х с указанием назначения битов для некоторых из них приведен в табл. 4.50.

Часть регистров специальных функций МК не входит в адресное пространство ОЗУ данных. Это регистры направления передачи портов ввода/вывода TRIS, регистр конфигурации МК OPTION и некоторые другие. Для обращения к этим регистрам используются специальные команды.

Рассматриваемый МК PIC16C54 имеет 12 двунаправленных линий ввода/вывода, которые объединены в два порта: 4-разрядный порт PORTA и 8-разрядный порт PORTB. Регистры данных портов располагаются в адресном пространстве памяти данных (табл. 4.50). Каждая линия может быть настроена на ввод или вывод посредством записи слова управления («0» - вывод, «1» - ввод) в соответствующий регистр направления передачи порта TRISAnnnTRISB.

Модуль таймера в составе МК PIC16C54 имеет следующие особенности:

•8-разрядный таймер-счетчик допускает внутреннее и внешнее тактирование;

•регистр таймера TMRO доступен для чтения и для записи;

•8-разрядный программируемый предварительный делитель.

Режим таймера или счетчика внешних событий, а также коэффициент предварительного делителя выбираются битами регистра OPTION.

ПРОЦЕССОРНОЕ ЯДРО PIC16

Центральный процессор CPU PIC16 включает (рис. 4.54):

•8-разрядное АЛУ с регистром признаков STATUS;

•рабочий регистр W;

•регистр косвенной адресации FSR;

•9-разрядный счетчик команд PC;

•12-разрядный регистр кода команды и дешифратор команд

Программно доступными регистрами центрального процессора являются младший байт счетчика команд PCL, регистр признаков STATUS, регистр косвенной адресации FSR и рабочий регистр W. Причем первые три расположены в адресном пространстве регистров специальных функций (табл. 4.50), следовательно, для обращения к ним может быть использована любая команда обращения к регистрам общего назначения. Рабочий регистр W не имеет собственного адреса в карте памяти, поэтому он не может быть прямо адресован. Для его загрузки и пересылки используются специальные команды:

MOVLW k ; Загрузить константу к в рабочий регистр W

MOVWF f ; Загрузить содержимое рабочего регистра W в регистр общего

; назначения f.

Рабочий регистр W по функциональному назначению близок к аккумулятору. При выполнении любой операции в АЛУ используется регистр W. В командах, имеющих два операнда, одним из операндов обязательно является рабочий регистр W. При выполнении действий над одним операндом, например операции инкремента и декремента, рабочий регистр W может не быть источником операнда, но всегда имеется возможность поместить результат операции в рабочий регистр W.

АЛУ выполняет минимально необходимый набор операций: сложение, вычитание, логические операции, сдвиг, операции над битами. В командах с двумя операндами (сложение, вычитание, логические операции) один из операндов расположен в рабочем регистре W, другой операнд может быть содержимым любой ячейки ОЗУ, в том числе и регистра специальных функций. Результат операции может иметь один из двух регистров назначения: рабочий регистр W, если суффикс d в аббревиатуре команды равен 0, или источник второго операнда регистр общего назначения f, если суффикс d равен 1. В командах с одним операндом (инкремент, декремент, сдвиги вправо и влево) источником операнда является любой регистр встроенного ОЗУ, результат операции размещается так же, как и в предыдущем случае.

По результатам арифметических и логических операций устанавливаются три признака: переноса С, нулевого результата Z и дополнительного переноса DC (см. табл. 4.50). Остальные разряды регистра признаков STATUS используются для адресации памяти программ (биты РА2 – РА0), а также для управления сторожевым таймером и режимом низкого энергопотребления (биты  и

и  ). Регистр признаков STATUS доступен для любой команды так же, как и любой другой регистр. Однако следует иметь в виду, что биты

). Регистр признаков STATUS доступен для любой команды так же, как и любой другой регистр. Однако следует иметь в виду, что биты  и

и  устанавливаются только аппаратно и не могут быть изменены посредством какой-либо команды,например, команда CLRF STATUS обнулит все биты регистра признаков, кроме

устанавливаются только аппаратно и не могут быть изменены посредством какой-либо команды,например, команда CLRF STATUS обнулит все биты регистра признаков, кроме  и

и  , а затем установит триггер Z.

, а затем установит триггер Z.

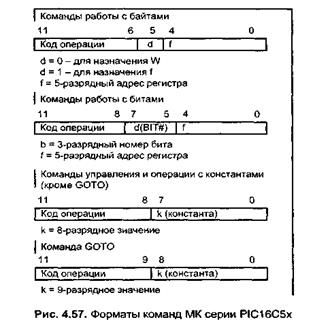

Все без исключения команды МК Р1С16С5х имеют длину 12 бит, т. е. любая команда размещается в одной ячейке памяти программ. Формат команд МКР1С16С5х представлен на рис. 4.57.

Для выборки операндов из внутренней памяти данных в CPU PIC16 используются два способа адресации: прямая (DIR) и косвенная (INDIR). Прямоадресуемыми являются все ячейки внутренней памяти данных, т. е. регистры специальных функций, расположенные в карте памяти данных, и регистры общего назначения (см. рис. 4.56). В мнемонике команд с прямой адресацией все эти регистры обозначаются общей аббревиатурой f. Например:

ADDWF f,d ; Мнемоника команды:

; Сложить содержимое рабочего регистра W с содержимым

; регистра общего назначения f. Результат поместить в W при

; d=0 или в f при d=1 (0< f < 31).

ADDWF 1Eh,1 ; Сложить содержимое рабочего регистра W с содержимым

; ячейки памяти 1Eh, результат поместить в ячейку памяти 1Eh.:

ADDWF FSR,0 ; Сложить содержимое рабочего регистра W с содержимым

; регистра косвенной адресации FSR, результат поместить в

; рабочий регистр W.

Прямая адресация используется также всеми командами работы с битами.

В качестве указателя адреса при косвенной адресации используется регистр FSR. Пять младших битов этого регистра адресуют ячейку памяти в пределах банка (адреса ячеек 0 - 1Fh). Разряды FSR6:FSR5 используются для выбора текущего банка. В МК PIC16C54 всего один банк памяти данных. Но в других моделях МК серии Р1С16С5х используется ОЗУ большей емкости. При написании программ для этих моделей следует помнить, что содержимое разрядов FSR6:FSR5 регистра косвенной адресации определяет адрес ячейки памяти не только при использовании косвенной адресации, но и при прямой адресации, так как непосредственно в коде команды с прямой адресацией указывается лишь 5-разрядный адрес ячейки.

При просмотре таблиц с перечнем команд МК Р1С16С5х Вы не увидите специальных мнемоник команд, использующих косвенную адресацию. Дело в том, что любая команда, которая использует прямую адресацию, может также использовать и косвенную. Для обозначения перехода от прямой адресации к косвенной при записи мнемоники команды используется имя регистра INDF. Этот регистр реально не существует, но при его указании в поле прямого адреса операнда центральный процессор использует содержимое регистра FSR в качестве адреса операнда. Например:

ADDWF INDF,0 ; Сложить содержимое рабочего регистра W с содержимым

; ячейки памяти, адрес которой находится в регистре косвенной

; адресации FSR, результат поместить в рабочий регистр W.

ADDWF 0,1 ; Сложить содержимое рабочего регистра W с содержимым

; ячейки памяти, адрес которой находится в регистре косвенной

; адресации FSR (0 - абсолютный адрес несуществующего

; регистра INDF), результат поместить в ту же ячейку памяти.

Чтение косвенным образом самого регистра INDF даст результат 00h (т. е. FSR = 0). Косвенная запись в регистр INDF не приведет к изменению состояния регистра FSR, хотя биты состояния могут быть изменены.

Регистры OPTION и TRIS не имеют собственных адресов в карте памяти, поэтому для работы с ними используются специальные команды с неявной адресацией (команды «OPTION» и «TRIS f»).

Для работы с константами, которые по определению могут быть расположены только в области ПЗУ, используется непосредственная адресация (IMM). Центральный процессор PIC16 может оперировать с константами двух форматов, для которых в мнемонике команды используется общая аббревиатура константы к. В командах загрузки и логических операций используются 8-разрядные константы (рис. 4.57). Это и понятно: разрядность константы должна совпадать с разрядностью второго операнда и регистра результата. Кроме того, 8-разрядный адрес вызываемой подпрограммы указывается в коде команды CALL. И лишь одна команда безусловного перехода GOTO k использует 9-разрядную константу, которая содержит абсолютный адрес следующей команды.

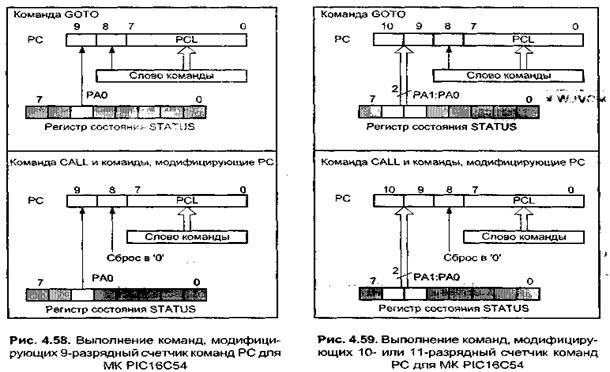

Формат счетчика адреса PC в МК серии Р1С16С5х может быть 9-разрядным, как в рассматриваемом PIC16C54, или 10- или даже 11-разрядным. Для каждой модели МК серии PIC16C5X формат счетчика адреса определяется объемом резидентного ПЗУ, которое хранит прикладную программу. Младший байт счетчика команд PCL интерпретируется как регистр специальных функций. Поэтому PCL имеет собственный адрес в карте адресного пространства внутреннего ОЗУ и, следовательно, программно доступен. Если счетчик команд является операндом в какой-либо команде (например, MOVWF PC, ADDWF PC или BSF PC,5) то результат операции в 8-разрядном формате загружается в младший байт счетчика команд PCL. Восьмой бит сбрасывается в «», а остальные загружаются из регистра состояния STATUS (см. табл. 4.50). Поэтому вычисляемые переходы и таблицы могут располагаться только в диапазоне первых 256 адресов каждой страницы памяти программ.

Если счетчик адреса 9-разрядный, т. е. объем ПЗУ составляет 512 ячеек, то формат команды «GOTO k» допускает переход в любую ячейку памяти программ (рис. 4.58).

В то же время формат команды «CALL k» предписывает использование только 8-разрядного формата адреса (рис. 4.58). Следовательно, все подпрограммы должны быть расположены только в диапазоне адресов 00h – 0FFh.

Если счетчик адреса имеет разрядность 10 или 11 бит, то команда «GOTO k» может передать управление только в пределах текущей страницы памяти программ (рис. 4.59). Команда «CALL k» производит вызов подпрограммы, начальный адрес которой должен быть расположен в первых 256 ячейках памяти текущей страницы ПЗУ.

При достижении границы страницы счетчик команд автоматически переходит на начало следующей страницы. Однако биты выбора страницы в регистре признаков STATUS не изменяются автоматически. Поэтому последующие команды GOTO, CALL, MOVWF PC возвратят управление к предыдущей странице, если биты РА1 :РАО не будут изменены программно. После сброса МК в регистре STATUS биты выбора страницы указывают на страницу 0, в то время как счетчик команд указывает на последнюю ячейку памяти последней страницы (для PIC16C54 состояние PC после сброса равно 1FFh). Поэтому, если по стартовому адресу будет расположена команда "GOTO k", управление будет передано на нулевую страницу.

МК серии Р1С16С5Х имеют двухуровневый аппаратный стек. Разрядность ячеек памяти стека совпадает с разрядностью счетчика команд PC. Команда CALL загружает в вершину стека (стек уровня 1) предварительно увеличенный на единицу счетчик команд. Одновременно предыдущее значение вершины стека копируется в стек уровня 2.

Предыдущее значение стека уровня 2 теряется. Таким образом, глубина вложения подпрограмм в МК серии Р1С16С5х равна 2.

Подсистема прерывания в рассматриваемых МК серии Р1С16С5х (но не во всех МК семейства PIC16) отсутствует. Следовательно, нет в системе команд инструкций работы со стеком.