Развитие мк с ядром mcs-51

Совершенствование МК на основе процессорного ядра MCS-51 происходило в следующих направлениях:

• увеличение частоты тактирования fXCLK, посредством перехода к другой, более совершенной технологии изготовления БИС;

• увеличение объема резидентной памяти программ и памяти данных; переход к FLASH

технологии памяти программ;

• совершенствование структуры МК посредством введения в его состав новых типов

периферийных модулей;

• кардинальная переработка архитектуры процессорного ядра с сохранением системы

команд MCS-51; полученные решения полностью совместимы с MCS-51 на уровне

исходного текста программ.

Начало столь бурной модернизации положила сама фирма «Intel», выпустив МК 80С52 с увеличенным объемом памяти программ (8 Кбайт), памяти данных (256 байт), третьим таймером на кристалле с функциями захвата/сравнения и расширенной подсистемой прерываний. Ныне аббревиатура 8052 используется для обозначения одного из стандартов в рамках архитектуры MCS-51.

Следующим шагом в развитии MCS-51 был предложенный фирмой «Intel» модуль процессора событий РСА (Program Counter Array), который входил в состав МК 8хС51 FA/ FB/FC/GB. Модуль РСА включает 16-разрядный счетчик временной базы и пять полностью идентичных каналов захвата/сравнения. Каждый из каналов может быть настроен на один из четырех режимов:

1)входного захвата по положительному/отрицательному/любому фронту входного сигнала;

2)выходного сравнения с формированием запроса на прерывание;

3)входного сравнения с формированием как «1» так и «0» на соответствующем выходе; эта функция в МК фирмы «Intel» получила название высокоскоростного выхода;

4)широтно-импульсного модулятора с дискретностью 8 разрядов и 4 фиксированными частотами сигнала.

Модуль РСА в настоящее время воспроизводится в МК фирмы «Pfilips», близкий аналог модуля присутствует в МК семейства С500 фирмы «Infineon».

Новую жизнь в популярные модификации МК с ядром MCS-51 вдохнули фирмы «Pfilips» и «Atmel», переведя резидентное ПЗУ на FLASH технологию. Более того, МК от «Atmel» стали программируемыми в системе. Дополнительный порт SPI в составе МК этой фирмы обеспечил такую возможность.

Фирма «Pfilips», выпуская самый большой ряд МК на основе стандартного ядра MCS-51, предложила новое семейство 51ХА с расширенной архитектурой. Основные отличия нового процессорного ядра:

•16-разрядное АЛУ на базе регистровой архитектуры;

• восемь 16-разрядных регистров для выполнения арифметических и логических операций;

• расширенный набор инструкций;

• аппаратная поддержка мультизадачности.

Новое процессорное ядро не совместимо по кодам инструкций со своим предшественником. Но каждой инструкции MCS-51 поставлена в соответствие инструкция нового ядра 51ХА. Специальный транслятор исходного текста конвертирует программы, написанные на языке Ассемблера MCS-51, в исходный текст для нового ядра 51ХА. Именно поэтому ядро 51 ХА относят к семейству MCS-51. По результатам тестов архитектура ХА обеспечивает увеличение производительности до 100 раз по сравнению с традиционной архитектурой MCS-51.

Фирма «Infineon» также поддерживает две линии МК, принадлежащих к семейству MCS-51. Наряду с выпуском полностью идентичных некоторым моделям стандартов 8051 и 8052 Intel, фирма разработала свое собственное ядро С500, полностью совместимое с MCS-51 на уровне кодов. И уже на базе этого ядра создала целый ряд МК со встроенными модулями CAN интерфейсов, а также специализированные МК для управления силовыми преобразователями частоты.

Еще одну оригинальную модернизацию ядра MCS-51 предложила фирма «Dallas Semiconductor». Изменение схемотехники базового ядра было проведено таким образом, что типовой цикл выборки команд сократился до 4 машинных тактов против исходных 12 тактов. В результате производительность МК при той же тактовой частоте возросла от 1,5 до 3 раз в зависимости от типа алгоритма. Эту новую линию МК назвали High Speed MCS-51 - высокоскоростные МК семейства 8051.

И, наконец, сама фирма «Intel» предложила новое процессорное ядро MCS-251, совместимое на уровне кодов с программами для 8051. Основные характеристики центрального процессора с архитектурой MCS-251:

• расширенный набор команд, включающий 16-бит арифметические и логические инструкции;

• регистровая архитектура, допускающая обращение к переменным в байтовом, двух

байтовом и четырехбайтовом форматах;

• конвейер команд;

• линейная адресация до 16 Мбайт памяти программ;

• выполнение самой быстрой инструкции в шесть раз быстрее MCS-51.

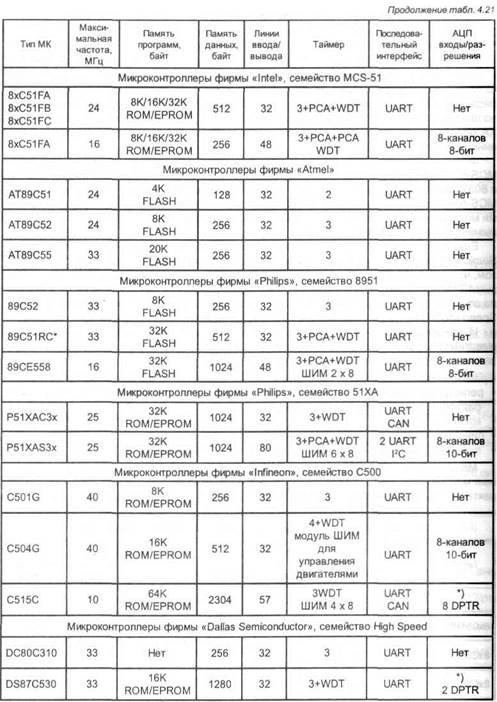

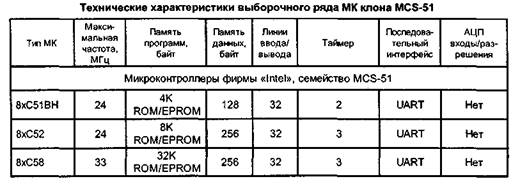

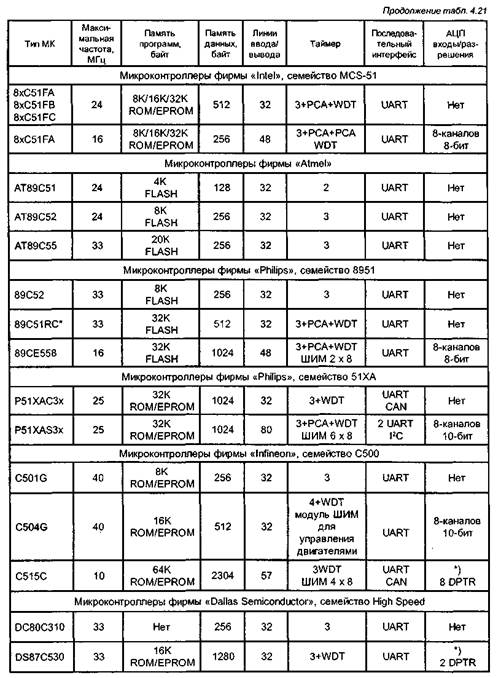

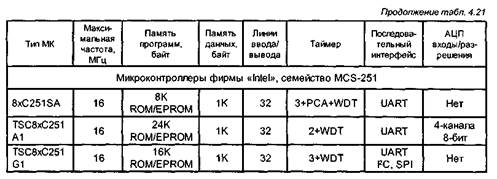

МК семейства MCS-251 содержат на кристалле три таймера, программируемый счетный массив РСА, улучшенный асинхронный порт, сторожевой таймер. Технические характеристики выборочного ряда МК клона MCS-51 приведены в табл. 4.21.

Таблица 4.21

|

|

4.3. СЕМЕЙСТВО МК НС08 ФИРМЫ «MOTOROLA»