Интерфейс шины процессоров Pentium

Теоретические основы

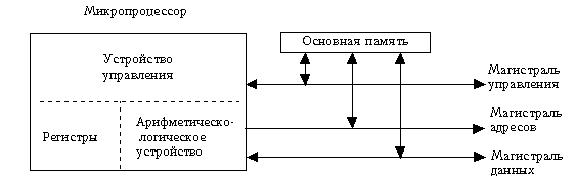

На рисунке 1 представлены важнейшие компоненты микропроцессора, а также его связь с основной памятью при помощи трех магистралей данных, адресов и управления. В состав МП входят устройство управления (УУ), арифметическо-логическое устройство (АЛУ) и набор регистров.

Устройство управления предназначено для управления работой всех компонентов микрокомпьютера и обеспечения должного взаимодействия различных компонентов друг с другом. Управление осуществляется с помощью импульсных сигналов, посылаемых УУ на соответствующие входы управляемых компонентов. Кроме того, УУ может получать ответные сигналы с управляемых компонентов.

Рисунок 1 – Микропроцессор и его связи с основной памятью

Физически УУ представляет собой цифровую электронную схему, на вход которой поступают коды подлежащих выполнению операций, а входом являются серии управляющих сигналов. Восприняв код той или иной операции, УУ формирует цепочку управляющих сигналов и подает их в нужные точки микрокомпьютера.

Арифметическо-логическое устройство предназначено для исполнения арифметических и логических операций. Основу АЛУ составляет операционный блок – цифровое электронное устройство, которое может настраиваться на различные операции и непосредственно осуществлять их. Настройка операционного блока на конкретную операцию и последовательность шагов ее выполнения обеспечиваются с помощью управляющих сигналов от УУ.

Регистры являются важными элементами микропроцессора. Регистр – это электронное цифровое устройство для временного запоминания информации в форме двоичного числа или кода. Запоминающим элементам в регистре является триггер, который может находиться в одном из двух состояний. Одно из этих состояний соответствует запоминанию двоичного нуля, а другое – запоминанию двоичной единицы. В общем случае регистр содержит несколько связанных друг с другом триггеров – по одному триггеру на каждый разряд запоминаемого двоичного числа. Число триггеров в регистре называется разрядностью регистра. Например, регистр из восьми триггеров – это 8-разряюный или 8-битовый регистр (так как каждый разряд регистра обеспечивает хранение одного бита информации).

Многие регистры специализированы по своей функции. Так, существуют регистр-аккумулятор или просто аккумулятор, программный счетчик, регистр команд, регистр адреса памяти и т.д. Аккумулятор входит в АЛУ и предназначен для хранения одного из операндов перед выполнением операции в АЛУ или для кратковременного запоминания результата операции. Операнд – это данное, используемое в текущей операции. Например, в операции суммирования операндами являются оба слагаемых.

Программныйсчетчик (счетчик команд, регистр адреса команды) служит для формирования и запоминания адреса очередной выполняемой команды. После выполнения каждой команды программный счетчик содержит адрес следующей команды, по которому эта команда хранится в памяти микрокомпьютера.

Регистр команд используется для хранения кода текущей выполняемой команды. Входящий в состав команды код операции используется, как уже говорилось, для формирования в УУ определенной серии управляющих сигналов, зависящей от конкретного кода операции. Оставшаяся часть кода команды может содержать информацию об адресах операндов, участвующих в выполнении данной команды.

Регистр адреса памяти служит для запоминания адреса кода команды, операнда или результата операции во время извлечения (чтения) команды или операнда из памяти или записи результата операций в память. Регистр адреса памяти может входить не в состав МП, а в состав элементов памяти микрокомпьютера.

Изменить роль специализированных регистров или даже узнать их содержимое программным путем нельзя, т.е. эти регистры, как говорят, программно-недоступны. Но в состав МП входят и регистры, которые программист может использовать в своей программе. Такие регистры микропроцессора называются программно-доступными. Состав и назначение их различны в разных типах микропроцессоров. Однако среди них почти всегда имеются регистр слова состояния процессора (РССП) и несколько регистров общего назначения (РОН).

Регистр слова состояния процессора хранит слово состояния процессора (ССП), отражающее информацию о состоянии МП и выполняемой им программы в каждый данный момент времени.

Регистры общего назначения обычно не имеют конкретного функционального назначения. Программист может в своей программе задействовать их так, как он считает нужным. Чтобы отличить РОНы друг от друга им присвоены уникальные имена (или номера), которые и записываются в программе.

Основная память. Микропроцессор может обрабатывать только те данные, которые находятся в основной памяти. Основная память обычно состоит из двух частей – ОЗУ и ПЗУ.

Оперативное запоминающее устройство обеспечивает чтение находящихся в нем данных и запись в него новых данных. В микрокомпьютерах ОЗУ обычно реализуется как энергозависимая память, т.е. такая память, содержимое которой разрушается (“стирается”) при выключении микрокомпьютера.

Постоянное запоминающее устройство обеспечивает только чтение данных, которые однажды были записаны в ПЗУ. Таким образом, содержимое ПЗУ не может быть изменено микропроцессором, оно постоянно (отсюда и название этого вида памяти). Это устройство создается как энергонезависимая память: ее содержимое не “стирается” при выключении питания микрокомпьютера. Запись нужных данных в ПЗУ осуществляется на специальных устройствах, вне микрокомпьютера. В ПЗУ помещают обычно некоторые особо важные или не подлежащие изменению программы и разнообразные константы.

Основная память представлена в совокупности блока ячеек памяти и регистра адреса. Процесс чтения (выборки) информации из ячейки или записи (занесения) информации в ячейку называется доступом к памяти. Для доступа к памяти предварительно по магистрали адреса в регистр адреса должен быть помещен адрес той ячейки, к которой производится доступ.

В состав МП входит генератор тактовой частоты. Он предназначен для синхронизации (т.е. согласования во времени) работы компонентов микрокомпьютера. Генератор формирует периодическую последовательность импульсов с частотой от нескольких сотен килогерц до нескольких мегагерц в зависимости от типа микропроцессора. Напомним, что герц – это единица измерения частоты колебаний, равная одному колебанию в секунду.

Регистры

Регистры процессора можно разделить на следующие группы:

· регистры общего назначения;

· сегментные регистры;

· регистр указателя команд и флаговый регистр;

· регистры дескрипторов;

· управляющие регистры;

· регистры системных адресов;

· отладочные регистры;

· тестовые регистры.

Регистры общего назначения являются 32 разрядными. При этом для сохранения совместимости с младшими моделями процессор 80386 поддерживает структуру регистровых файлов процессоров 8086 и 80286, действительны все наименования, применявшиеся для обозначения 16- и 8-разрядных регистров.

Процессоры класса Pentium

Процессоры Pentium фирмы Intel представляют пятое поколение процессоров семейства 80х86. По базовой регистровой архитектуре и системе команд они совместимы с 32-битными процессорами, но имеют 64-битную шину данных, благодаря чему их иногда ошибочно называют 64-разрядными. По сравнению с предыдущими поколениями процессоры Pentium имеют следующие качественные отличия:

· Суперскалярная архитектура: процессор имеет два параллельно работающих конвейера обработки (U-конвейер с полным набором и V-конвейеи с несколько ограниченным набором инструкций), благодаря чему он способен одновременно выполнять две инструкции. Однако преимущества этой архитектуры полностью реализуются только при специальном режиме компиляции ПО;

· Применение технологии динамического предсказания ветвлений совместно с выделенным внутренним кэшем команд объемом 8 Кбайт обеспечивает максимальную загрузку конвейеров.

· Применение технологии динамического предсказания ветвлений совместно с выделенным внутренним кэшем команд объемом 8 Кбайт обеспечивает максимальную загрузку конвейеров.

· Внутренний (Level 1) кэш данных объемом 8 Кбайт в отличие от 486 работает с отложенной (до освобождения внешней шины) записью и настраивается на режим сквозной или обратной записи, поддерживая протокол MESI.

· Внешняя шина данных ради повышения производительности имеет разрядность 64 бит, что требует соответствующей организации памяти.

· Встроенный сопроцессор за счет архитектурных улучшений (конвейеризации) в 2-10 раз превосходит FPU-486 по производительности.

· Введено несколько новых инструкций, в том числе распознавание семейства и модели CPU.

· Применено выявление ошибок внутренних устройств (внутренний контроль паритета) и внешнего интерфейса шины, контролируется паритет шины адреса.

· Введена возможность построения функционально избыточной двухпроцессорной системы.

· Реализован интерфейс построения двухпроцессорных систем с симметричной архитектурой (начиная со второго поколения Pentium).

· Введены средства управления энергопотреблением.

· Применена конвейерная адресация шинных циклов.

· Сокращено время (количество тактов) выполнения инструкций.

· Введена трассировка инструкций и мониторинг производительности.

· Расширены возможности виртуального режима — введена виртуализация флага прерываний.

· Введена возможность оперирования страницами размером 4 Мб (вместо 4 Кб) в режиме страничной переадресации (Paging).

Все Pentium-процессоры имеют средства SMM, возможности которых расширялись по мере появления новых моделей.

Средства тестирования включают возможность выполнения встроенного теста BIST (Built-in Self Test), обеспечивающего выявление ошибок микрокодов, программируемых логических матриц, тестирование командной кэш-памяти, кэш-памяти хранения данных, буфера быстрой переадресации и ROM. Все процессоры имеют стандартный тестовый порт IEEE 1149.1, позволяющий тестировать процессор с помощью интерфейса JTAG.

Процессоры Pentium MMX (P55C) — новое поколение процессоров, основанное на ММХ-технологии, которая ориентирована на мультимедийное, 2D - и SD-графическое и коммуникационное применение. В логическую архитектуру Pentium введены восемь 64-битных регистров, 4 новых типа данных и 57 дополнительных мнемоник инструкций для одновременной обработки нескольких единиц данных SIMD (Single Instruction Multiple Data). Одновременно обрабатываемое 64-битное слово может содержать как одну единицу обработки, так и 8 однобайтных, 4 двухбайтных или 2 четырехбайтных операнда. В остальных командах обеспечивается совместимость с Pentium. На самом деле, регистры MMX физически расположены в стеке регистров FPU, так что новых регистров этот процессор не предоставляет, и чередование использования программой инструкций FPU и MMX приводит к снижению эффективности работы, связанному с необходимостью пересылок данных из стека в память и обратно. Эффективность MMX вызывает некоторые сомнения, поскольку те функции, для которых они целесообразны, с успехом выполняются акселераторами графических карт, которые стали уже обыденными.

Интерфейс шины процессоров Pentium

По интерфейсу и составу сигналов шина процессора Pentium похожа на шину 486, но имеет значительные отличия. Новые особенности направлены на поддержку политики обратной записи кэша, повышение производительности и обеспечение дополнительных функциональных возможностей.

Шина данных - 64-битная, для повышения производительности обмена с памятью.

Расширения архитектуры

Процессоры Pentium (и более старшие) имеют ряд расширений относительно базовой архитектуры 32-разрядных процессоров и ее развития в процессорах четвертого поколения, появляющихся по мере совершенствования моделей. Для возможности получения сведений о них в систему команд включена инструкция CPUID, позволяющая программно в любой момент времени (а не только сразу после сигнала RESET) получить сведения о классе, модели и архитектурных особенностях конкретного процессора.

В дополнение к базовой архитектуре 32-разрядных процессоров, Pentium имеет набор регистров, специфических для модели — MSR (Model Specific Registers). В их число входит группа тестовых регистров (TR1...TR12), средства мониторинга производительности, регистры-фиксаторы адреса и данных цикла, вызвавшего срабатывание контроля машинной ошибки. Название этой группы регистров указывает на возможную их несовместимость для разных классов (Pentium и Pentium Pro) и даже моделей процессоров. Программа, их использующая, должна опираться на сведения о процессоре, полученные с помощью инструкции CPUID.

Средства мониторинга производительности включают таймер реального времени и счетчики событий. Таймер TSC (Time Stamp Counter) представляет собой 64-битный счетчик, инкрементируемый с каждым тактом ядра процессора. Для чтения его содержимого предназначена инструкция RDTSC.

Счетчики событий CTRO, CTR1 разрядностью по 40 бит программируются на подсчет событий различных классов, связанных с шинными операциями, исполнением инструкций, событиями во внутренних узлах, связанных с работой конвейеров, кэша, контролем точек останова и т. п. Шести битные поля типов событий позволяют каждому из счетчиков независимо назначить подсчет событий из обширного списка. Состояние счетчиков может быть предустановленно и считано программно.

Тестовые регистры позволяют управлять большинством функциональных узлов процессора, обеспечивая возможность весьма подробного тестирования их работоспособности. С помощью бит регистра TR12 можно запретить новые архитектурные свойства (предсказание и трассировку ветвлений, параллельное выполнение инструкций), а также работу первичного кэша:

· Бит 0 — NBP (No Branch Prediction) — запрещает заполнение буфера ВРВ. При этом прежние вхождения продолжают действовать, для полного отключения предсказания необходимо загрузить регистр CR3 (это вызовет сброс таблицы ветвлений).

· Бит 1 — TR — разрешает формирование специального цикла сообщения о ветвлении.

· Бит 2 — SE (Single Pipe Execution) — запрещает работу второго конвейера (отменяет парное исполнение инструкций).

· Бит 3 — (3 (Cache Inhibit) - запрещает заполнение строк первичного кэша.

· Бит 9 — ITR (10 Trap Restart) — разрешает поддержку рестарта инструкций ввода/вывода при прерываниях SMI.

Двухпроцессорные системы

Процессоры Pentium, начиная со второго поколения, имеют специальные интерфейсные средства для построения двухпроцессорных систем. Интерфейс позволяет на одной локальной системной шине устанавливать два процессора, пру этом почти все их одноименные выводы просто непосредственно объединяются Целью объединения является либо использование симметричной мультипроцессорной обработки SMP (Symmetric Multi-Processing), либо построение функционально избыточных систем FRC (Functional Redundancy Checking).

В системе с SMP каждый процессор выполняет свою задачу, порученную ему операционной системой. Поддержку SMP имеют такие ОС, как Novell Net Ware, Widows NT, OS/2.