Процессорное ядро семейства нс08

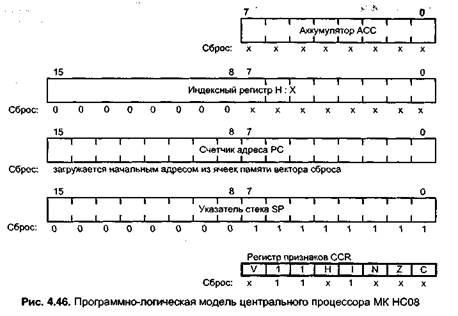

Центральный процессор МК семейства НС08 (далее CPU08) выполняет действия над 8-разрядными операндами. Программная модель CPU08 (рис. 4.46) содержит пять регистров, которые не являются частью объединенного адресного пространства, и, следовательно, для обращения к ним должны быть использованы специальные команды.

Аккумулятор (АСС) — 8-разрядный регистр, в котором хранятся операнды, результаты арифметических и логических операций. Сброс не изменяет состояние АСС.

Индексный регистр (Н:Х)- 16-разрядный регистр (Н-старший байт, Х-младший байт). Основное назначение индексного регистра - участие в формировании адреса операнда в режимах индексной адресации. Индексный регистр может также использоваться для хранения промежуточных результатов вычислений или как источник одного из операндов в операциях умножения и деления. Система команд CPU08 предусматривает загрузку данных в индексный регистр и выполнение операций над ними как в двухбайтовом, так и в однобайтовом форматах. В последнем случае обращение производится только к младшему байту регистра X. После сброса МК старший байт индексного регистра Н принудительно устанавливается в «0», что обеспечивает адекватное выполнение программ, ранее написанных для семейства НС05. Сброс не изменяет состояние младшего байта индексного регистра X.

Программный счетчик (PC)— 16-разрядный регистр, содержит адрес текущей команды либо адрес операнда, используемого в текущей команде. После сброса МК программный счетчик автоматически загружается вектором начального запуска, который записан в ячейках памяти резидентного ПЗУ с адресами $FFFE (старший байт) и $FFFF (младший байт). Вектор начального запуска является адресом начала прикладной программы управления.

Указатель стека (SP) - 16-разрядный регистр, содержит адрес верхушки стека. В отличие от CPU05, глубина стека МК семейства НС08 ограничена только объемом резидентного ОЗУ. Вызов подпрограммы использует 2 ячейки стека, прерывание - 5 ячеек. Следует отметить, что стремление разработчиков обеспечить полную программную совместимость с CPU05 привело к тому, что при переходе на подпрограмму прерывания CPU08 автоматически сохраняет в стеке программный счетчик PC, аккумулятор АСС, младший байт индексного регистра X и регистр признаков CCR, но не сохраняет старший байт индексного регистра Н. При сбросе МК указатель стека устанавливается в состояние $OOFF, назначая область стека в нулевую страницу ОЗУ МК.

Регистр признаков (CCR)- 8-разрядный регистр, содержит 6 флагов условий: переноса (С), нулевого результата (Z), отрицательного результата (N), переполнения (V), дополнительного переноса (Н), бит глобальной маски прерывания (I). Особенностью флага нулевого результата Z и флага знака N является установка их после операций пересылки (см. систему команд). Отличительная особенность ядра CPU08 и всех 8-разрядных процессорных ядер фирмы «Motorola» - расположение маски прерывания в составе регистра признаков.

Установка маски прерывания в «1» запрещает все прерывания, кроме программного по команде SWI. Если запрос на прерывание появится, когда маска I = 0, то центральный процессор сохранит в стеке содержимое программного счетчика PC, аккумулятора АСС, младшего байта индексного регистра X и регистра признаков, установит бит в«1»и перейдет на выполнение подпрограммы прерывания. Если запрос на прерывание появится, когда флаг I = 1, то запрос на прерывание будет запомнен. МК начнет обрабатывать запрос на прерывание сразу, как только бит I будет очищен. Инструкция RTI (возврат из прерывания) сбрасывает бит I в «0» автоматически. CPU08 имеет две специальные команды: CLI - очистить бит маски, SEI - установить бит маски.

В состоянии сброса бит I устанавливается в «1», что запрещает аппаратные прерывания. Разрешение аппаратных прерываний (установка I в «0») может быть выполнено только программно командой CLI.

Для выборки операндов из памяти МК семейства НС08 используют следующие способы адресации:

• неявную (INH - Inherent);

• непосредственную (IMM - Immediate);

• прямую (DIP - Direct);

• прямую расширенную (EXT - Extended);

• индексную (IX - Indexed);

• индексную со смещением в один байт (1X1 - Indexed, 8 bit offset);

• индексную со смещением в два байта (IX2 - Indexed, 16 bit offset);

• индексную с постинкрементированием (IX+ - Indexed with post incrementer);

• индексную со смещением в один байт с постинкрементированием (1X1+ - Indexed, 8 bit offset with post incrementer);

•индексную по указателю стека со смещением в один байт (SP1 - Stack pointer, 8 bit

offset);

•индексную по указателю стека со смещением в два байта (SP2 - Stack pointer, 16 bit offset);

• относительную (PEL - Relative).

Неявная адресация.К инструкциям с неявной адресацией относятся команды, которые не требуют для своего выполнения каких-либо операндов, например команда STOP или команда возврата из прерывания RTI.

Неявную адресацию имеют инструкции, которые содержат адрес операнда в коде команды, например, команда установки бита переноса SEC или команда инкремента аккумулятора INCA. Все команды с неявной адресацией имеют длину в 1 байт и состоят только из кода операции.

Непосредственная адресация.Код операции команды с непосредственной адресацией размещается в первом байте. Сразу же за кодом операции следует 1 байт данных. Эти данные не могут быть изменены в ходе выполнения программы, так как они расположены непосредственно в памяти программ, т.е. в ПЗУ. Большинство команд с непосредственной адресацией имеют длину в 2 байта. Условное обозначение операнда в мнемонике команды - #орг:

Примеры.

ADD #opr ;3апись команды ADD с непосредственной адресацией в общем виде.

ADD #3 ; Сложить содержимое аккумулятора АСС с числом 3,

; результат записать в АСС.

ORA #$0А ; Выполнить операцию поразрядного ИЛИ над содержимым АСС и

; шестнадцатеричным числом $ОА. Результат записать в АСС.

Прямая адресация.Команды с прямой адресацией имеют длину 2 байта. Первый байт предназначен для кода команды, второй байт содержит адрес ячейки памяти, где хранится операнд. Так как МК семейства НС08 имеют адресное пространство, превышающее диапазон $00 -$FF, то во втором байте команды задается только младший байт адреса, а старший автоматически устанавливается $00. Условное обозначение адреса в мнемонике команды - орг:

Примеры.

ADD opr ; Запись команды ADD с прямой адресацией в общем виде.

ADD $31 ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти

; с адресом $0031. Результат поместить в АСС.

ORA $0А ; Выполнить операцию поразрядного ИЛИ над АСС и содержимым ячейки

; памяти с адресом $0031. Результат поместить в АСС.

Прямая расширенная адресация.Команды с прямой расширенной адресацией имеют длину 3 байта. Первый байт предназначен для кода команды, второй и третий байты содержат адрес ячейки памяти, где хранится операнд. Команды с прямой расширенной адресацией позволяют работать со всем адресным пространством МК. Мнемоническое обозначения команд с прямой и прямой расширенной адресацией совпадают. При трансляции программ не следует заботиться о том, что инструкции с прямой и прямой расширенной адресацией имеют одинаковую мнемонику. Программа Ассемблер самостоятельно подставит код необходимой операции, проанализировав численное значение адреса орг.

Примеры.

ADD opr ;Запись команды ADD с прямой расширенной адресацией в общем виде.

ADD $01Е1 ;Сложить содержимое аккумулятора АСС с содержимым ячейки памяти с

;адресом $01Е1. Результат поместить в АСС.

LDX $01Е1 ;Загрузить в младший байт индексного регистра X содержимое ячейки

памяти с адресом 01Е1h

Индексная адресация.Команды с индексной адресацией имеют длину 1 байт, в котором расположен код операции. Адрес операнда находится в двухбайтовом индексном регистре Н:Х.

Примеры.

ADD ,X ; Запись команды ADD с индексной адресацией в общем виде.

ADD ,X ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти,

; адрес которой находится в индексном регистре Н:Х.

LDA ,Х ; Загрузить в аккумулятор АСС содержимое ячейки памяти, адрес которой

; находится в индексном регистре Н:Х.

Индексная адресация со смещением 1 байт.Команды с данным типом адресации имеют длину 2 байта. Первый байт содержит код операции, а второй - беззнаковую константу, которая носит название «смещение». В определении адреса операнда участвует индексный регистр Н:Х, который содержит код базового адреса. Центральный процессор вычисляет адрес операнда путем сложения содержимого индексного регистра Н:Х с кодом второго байта команды. После сложения адрес операнда представляется в двухбайтовом формате.

Примеры.

ADD opr.X ; Запись команды ADD с индексной адресацией со смещением в один байт

; в общем, виде.

ADD $80,Х ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти,

; адрес которой равен (Н:Х)+128.

LDA $1 ,Х ; Загрузить в аккумулятор АСС содержимое ячейки памяти, адрес которой

; равен (Н:Х)+1.

Индексная адресация со смещением 2 байта.Команды с данным типом адресации имеют длину 3 байта. Первый байт содержит код операции, а второй и третий байты -двухбайтовую беззнаковую константу. В определении адреса операнда участвует двухбайтовый индексный регистр Н:Х. Центральный процессор вычисляет адрес операнда путем сложения двухбайтового кода смещения с содержимым регистра Н:Х. После сложения адрес операнда представляется в двухбайтовом формате. Мнемонические обозначения команд с индексной адресацией со смещениями 1 и 2 байта совпадают. Однако не следует беспокоиться об этом при написании программы. При трансляции программа Ассемблер самостоятельно подставит код необходимой операции, проанализировав численное значение адреса орг.

Примеры

ADD opr.X ; Запись команды ADD с индексной адресацией со смещением в два байта

; в общем, виде.

ADD $0100,X ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти,

; адрес которой равен (Н:Х)+512.

LDA $01FF.X ; Загрузить в аккумулятор АСС содержимое ячейки памяти, адрес которой

; равен (Н:Х)+1023.

Индексная адресация с пост инкрементированием.Индексная адресация с пост-

инкрементированием используется только в командах MOV и CBEQ. Адрес одного из операндов этих команд находится в двухбайтовом индексном регистре Н:Х. После выполнения команды содержимое индексного регистра Н:Х увеличивается на 1.

Примеры.

MOV X+,opr ; Запись команды MOV с индексной адресацией

; с пост инкрементированием в общем виде.

MOV Х+,$68 ; Записать данные из ячейки памяти с адресом $68 в ячейку памяти, адрес

; которой находится в индексном регистре Н:Х. Увеличить на 1 адрес

; в регистре Н:Х.

CBEQ X+,rel ; Запись команды CBEQ с индексной адресацией

; с пост инкрементированием в общем виде.

CBEQ X+,m1 ; Сравнить аккумулятор АСС и содержимое ячейки памяти, адрес которой

; находится в индексном регистре Н:Х. Перейти по метке ml в случае

; равенства. Увеличить на 1 адрес в регистре Н:Х.

Индексная адресация со смещением в один байт и постинкрементированием.

Индексная адресация со смещением в один байт и пост инкрементированием используется только в команде CBEQ. В определении адреса одного из операндов команды

участвует индексный регистр Н:Х, который содержит код базового адреса. Центральный процессор вычисляет адрес операнда путем сложения содержимого индексного регистра Н:Х с байтом кода смещения, который указан во втором байте команды. После сложения адрес операнда представляется в двухбайтовом формате. После выполнения команды содержимое индексного регистра Н:Х увеличивается на 1.

Примеры.

CBEQ opr,X+,rel ; Запись команды CBEQ с индексной адресацией со смещением в один

; байт и постинкрементированием в общем виде.

CBEQ $80,X+,m1 ; Сравнить аккумулятор АСС и содержимое ячейки

; памяти, адрес которой равен (Н:Х)+128. Перейти по метке ml в случае

; равенства. Увеличить на 1 адрес в регистре Н:Х.

Индексная адресация по указателю стека со смещением в 1 байт.Команды с данным типом адресации имеют длину 3 байта. Первый и второй байты содержат код операции, а третий байт - беззнаковую константу смещения. В определении адреса операнда участвует указатель стека SP, который содержит код базового адреса. Центральный процессор вычисляет адрес операнда путем сложения содержимого указателя стека SP с кодом смещения. После сложения адрес операнда представляется в двухбайтовом формате.

Примеры

ADD opr.SP ; Запись команды ADD с адресацией по указателю стека со смещением в один

; байт в общем виде.

ADD $80,SP ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти,

; адрес которой равен (SP)+128.

LDA $1,SP ; Загрузить в аккумулятор АСС содержимое ячейки памяти, адрес которой

; равен (SP)+1.

Индексная адресация по указателю стека со смещением в 2 байта.Команды сданным типом адресации имеют длину 4 байта. Первый и второй байты содержат код операции, а третий и четвертый байты - двухбайтовую беззнаковую константу. В определении адреса операнда участвует указатель стека SP. Центральный процессор вычисляет адрес операнда путем сложения двухбайтового кода смещения с содержимым указателя стека SP. После сложения адрес операнда представляется в двухбайтовом формате. Мнемонические обозначения команд с индексной адресацией со смещениями 1 и 2 байта совпадают. Однако не следует беспокоиться об этом при написании программы. В процессе трансляции программа Ассемблер самостоятельно подставит код необходимой операции, проанализировав численное значение адреса орг.

Примеры.

ADD opr.SP ; Запись команды ADD с адресацией по указателю стека со смещением

; в один байт в общем виде.

ADD $0100,SP ; Сложить содержимое аккумулятора АСС с содержимым ячейки памяти,

; адрес которой равен (SP)+512. LDA $01 FF.SP

; Загрузить в аккумулятор АСС содержимое ячейки памяти, адрес которой

; равен (SPJ+1023.

Относительная адресация.Относительная адресация применяется только в командах условных переходов, которые используются для организации ветвления программ. Команды условных переходов имеют двухбайтовый формат. Первый байт содержит код операции, а второй - смещение адреса следующей команды относительно адреса текущей команды в целочисленном формате со знаком. Диапазон возможных кодов смещения: от -128 до +127.

Если условие, заданное типом используемой команды условного перехода, выполня

ется, то адрес следующей команды центральный процессор вычисляет путем сложения

текущего адреса с кодом смещения. Если условие не выполняется, то МК переходит к

выполнению следующей команды.

При написании программ нет необходимости вычислять абсолютные коды смещения для команд условного перехода. Достаточно указать лишь метку, численное значение кода смещения вычислит программа Ассемблер.

Примеры

JZ table1 ; Перейти по метке lablel, если результат операции равен 0.