Источники и механизм обработки прерываний

Прерывания изменяют текущую последовательность выполнения команд с целью обслуживания внешнего или внутреннего события, вызывавшего прерывание. Прерывание в отличие от сброса не останавливает выполнение текущей инструкции. При поступлении запроса на прерывание МК завершает выполнение текущей команды, а затем реализует механизм перехода к подпрограмме прерывания:

• регистры центрального процессора автоматически сохраняются в стеке в следующем порядке: регистр признаков ССР, аккумулятор АСС, младший байт индексного регистра X, старший байт счетчика адреса РСН, младший байт счетчика адреса PCL; по завершении прерывания инструкция возврата из прерывания RTI восстанавливает в обратном порядке все регистры центрального процессора для возобновления выполнения фоновой программы;

• бит глобальной маски прерывания I в регистре признаков CCR устанавливается в «1»,

запрещая обслуживание любых других запросов на прерывание до тех пор, пока не

будет завершена текущая подпрограмма прерывания;

• счетчик адреса PC загружается адресом начала подпрограммы прерывания, который называют вектором прерывания.

В МК семейства НС08 реализован традиционный для всех МК фирмы «Motorola» механизм загрузки векторов прерывания. В адресном пространстве памяти программ МК выделена специальная область, которая носит название сегмента векторов прерывания. Каждому источнику запросов на прерывание в этой области отведено по два байта памяти с фиксированными адресами. Пользователь на этапе программирования МК заносит в эти ячейки памяти адрес начала подпрограммы прерывания. При переходе к выполнению подпрограммы прерывания этот адрес автоматически загружается в счетчик адреса центрального процессора. В рассматриваемом сегменте памяти размещается также вектор сброса.

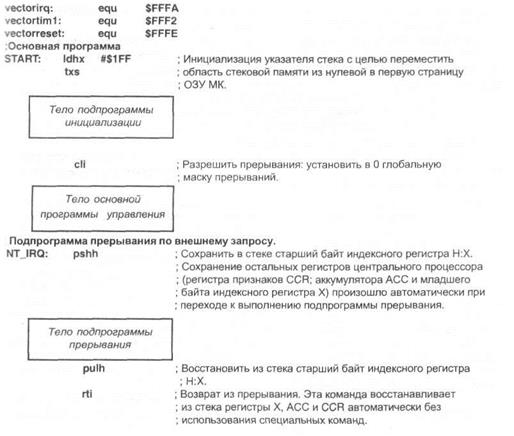

Ниже приведен пример структуры прикладной программы с двумя подпрограммами

прерывания по запросам на входе  и от процессора событий TIM1. Абсолютные адреса сегмента векторов прерывания соответствуют карте памяти МК MC68HC908GP32.

и от процессора событий TIM1. Абсолютные адреса сегмента векторов прерывания соответствуют карте памяти МК MC68HC908GP32.

Аппаратные средства прерывания МК семейства НС08 имеют следующие особенности:

• выполнение команды возврата из прерывания RTI автоматически разрешает прерывания;

• выполнение команды возврата из прерывания RTI не блокирует прерывания на период выполнения следующей команды; вход в новую подпрограмму возможен сразу

после выполнения команды RTI.

Дело в том, что при входе в подпрограмму прерывания бит глобальной маски прерывания I обязательно равен 0. Иначе прерывания были бы запрещены и говорить о подпрограмме прерывания не имело бы смысла. Содержимое регистра признаков, в котором располагается маска I, сохраняется в стеке при входе в подпрограмму прерывания. Следовательно, при восстановлении регистра признаков из стека по команде RTI бит глобальной маски прерывания установится в «0», и прерывания будут разрешены.

Все источники прерываний МК семейства НС08 можно разделить на три группы:

1)немаскируемое программное прерывание по команде SWI;

2)маскируемые внешние прерывания по входу  и по некоторому числу линий

и по некоторому числу линий

портов ввода/вывода, которые принадлежат модулю сканирования клавиатуры KBI08;

3)маскируемые прерывания от периферийных модулей.

Механизм программного прерывания позволяет обратиться к какой-либо подпрограмме прерывания по ходу выполнения прикладной программы и воспользоваться подпрограммой прерывания как обычной подпрограммой. Наличие в системе команд инструкции программного прерывания SWI предоставляет такую возможность. Эта команда автоматически загружает в стек регистры CCR, АСС, X и увеличенное на единицу содержимое счетчика команд PC, а затем осуществляет переход по адресу, который указан в ячейках памяти $FFFC и $fffd сегмента векторов прерывания. Этот адрес может быть начальным адресом подпрограммы прерывания или же находиться внутри нее. При выходе из подпрограммы прерывания команда RTI восстановит содержимое регистров центрального процессора и МК продолжит выполнение прикладной программы с команды, которая была следующей за командой SWI. Таким образом, программисту предоставляется возможность обращения в произвольный момент времени к фрагменту подпрограммы прерывания, который начинается с произвольно выбранной инструкции внутри подпрограммы прерывания, но заканчивается обязательно командой RTI.

Число линий МК MC68HC908GP32 для приема внешних запросов на прерывания варьируется от одной линии (вход  ) до 9 линий. Обслуживание запросов по входу

) до 9 линий. Обслуживание запросов по входу  осуществляет модуль внешних прерываний IRQ08. Активный уровень сигнала запроса на входе

осуществляет модуль внешних прерываний IRQ08. Активный уровень сигнала запроса на входе  - низкий логический, длительность сигнала запроса должна составлять не менее tILIH=50 нc. Дополнительные входы внешних запросов могут быть получены путем соответствующей инициализации модуля сканирования клавиатуры KBI08, который позволяет настроить некоторое число линий ввода/вывода МК для приема внешних запросов на прерывание.

- низкий логический, длительность сигнала запроса должна составлять не менее tILIH=50 нc. Дополнительные входы внешних запросов могут быть получены путем соответствующей инициализации модуля сканирования клавиатуры KBI08, который позволяет настроить некоторое число линий ввода/вывода МК для приема внешних запросов на прерывание.

Все прерывания, кроме программного по команде SWI, могут быть разрешены или запрещены сбросом или установкой глобальной маски прерывания I в регистре признаков CCR:

cll ; команда сбрасывает в «О» бит I, т. е. разрешает прерывания.

sel ; команда устанавливает бит I в «1», т. е. запрещает прерывания.

Кроме того, каждому источнику прерывания, за исключением программного, поставлена в соответствие индивидуальная маска прерываний, которая расположена в одном из регистров специальных функций соответствующего периферийного модуля.

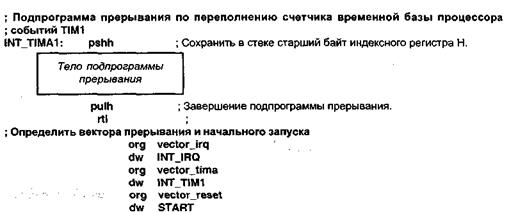

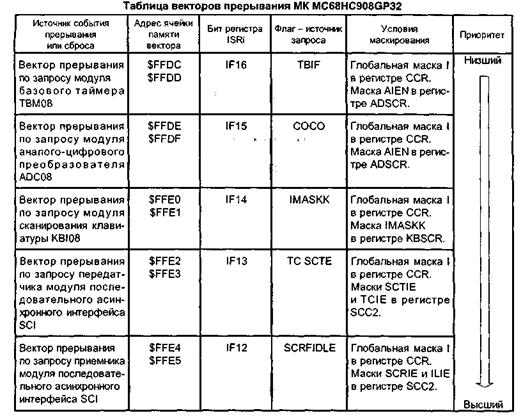

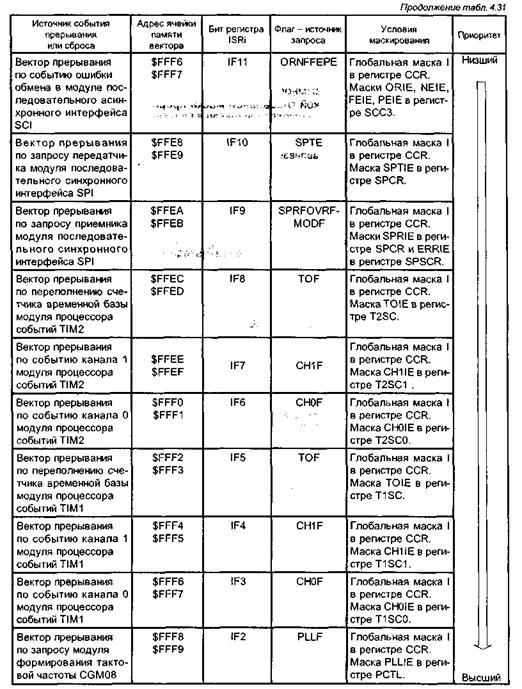

Подсистема прерываний МК семейства НС08 имеет жесткое распределение приоритетов, которое не может быть скорректировано программными настройками. Источники прерываний, уровни их приоритетов, абсолютные адреса векторов прерываний для МК MC68HC908GP32 приведены в табл. 4.31.

Таблица 4.31

|

ПОРТЫ ВВОДА/ВЫВОДА

МК MC68HC908GP32 обладает 33 линиями ввода/вывода данных. Эти линии объединены в 8-разрядные параллельные порты, которые именуют в соответствии с буквами латинского алфавита: Port A, Port В, Port С, Port D, Port H.

Все линии ввода/вывода MKMC68HC908GP32- двунаправленные, т. е. могут использоваться разработчиком как для ввода данных в МК, так и для вывода логических сигналов. Направление передачи линий ввода/вывода настраивается программно путем записи управляющих слов в регистры специальных функций. Возможно изменение направления передачи в ходе выполнения программы посредством перепрограммирования этих регистров. Сигнал сброса устанавливает все линии в режим ввода. Направление передачи каждой линии может быть выбрано разработчиком произвольно, независимо от других линий, принадлежащих к одному и тому же порту ввода/вывода.

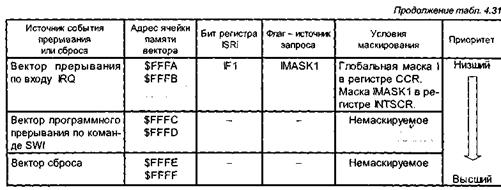

Большинство линий ввода/вывода обладают так называемой альтернативной функцией. Эти линии связаны со встроенными в МК периферийными устройствами, они обеспечивают связь периферийных модулей с «внешним миром». Так, линии порта Port В используются для подключения к встроенному АЦП измеряемых напряжений, линии других портов служат линиями ввода/вывода последовательных приемопередатчиков. Если соответствующий периферийный модуль МК не используется, то его выводы можно задействовать как обычные линии ввода/вывода. Распределение линий ввода/вывода по портам, спецификация линий альтернативных функций для МК MC68HC908GP32 приведены в табл. 4.32.

По способу схемного решения выходного драйвера различают два типа линий ввода/

вывода:

1)линии с обычной схемотехникой двунаправленной линии ввода/вывода;

2)двунаправленные линии с программно-подключаемыми в режиме ввода подтягивающими резисторами RPULLUP (см. рис. 4.5).

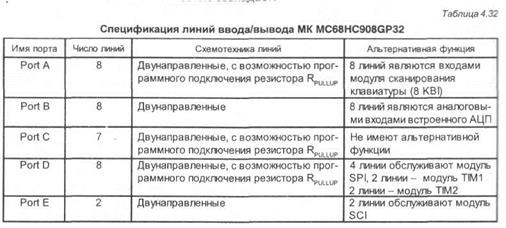

Если порт имеет «обычную» схемотехнику, то для его обслуживания предусмотрены два типа регистров:

1)РТх - регистр данных порта х, где х - имя порта ввода/вывода;

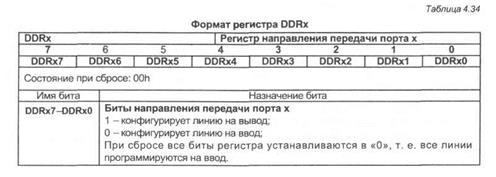

2)DDRx - регистр направления передачи порта х.

Если порт имеет схемотехнику с программно-подключаемым «подтягивающим» резистором, то для обслуживания порта предусмотрены три регистра:

1)РТх - регистр данных порта х;

2)DDRx - регистр направления передачи порта х ;

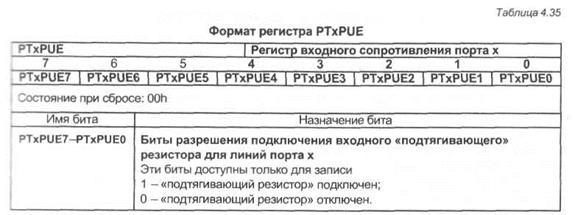

3)PTxPUE - регистр входного сопротивления порта х.

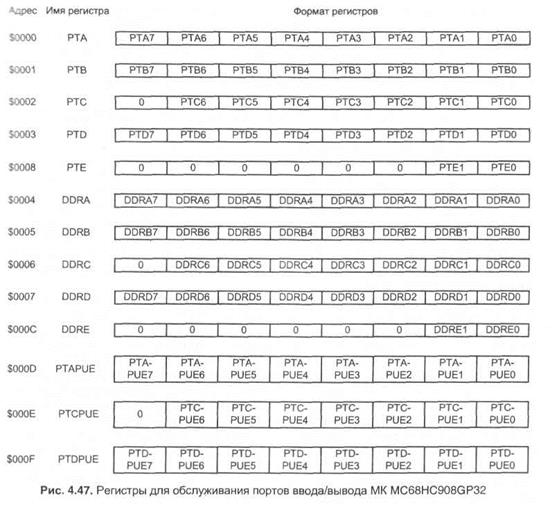

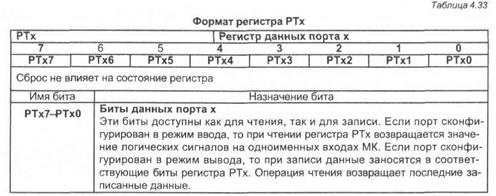

Так, порт Port А микроконтроллера MC68HC908GP32 обслуживается регистрами РТА,DDRA и PTAPUE. В табл. 4.33, 4.34, и 4.35 приведен формат регистров специальных функций РТх, DDRx и PTxPUE. Заметим, что формат регистров РТх и DDRx для портов с различной схемотехникой полностью совпадает.

|

|

|

Детальный формат всехрегистров специальных функций портов ввода/вывода приведен ниже (рис. 4.47).

|

4.3.7. ПРОЦЕССОР СОБЫТИЙ TIM08

Модуль TIM08, хотя и носит дословное название «модуль таймерного интерфейса», по сути, является одним из лучших процессоров событий в 8-разрядных МК.

Модуль TIM08 состоит из 16-разрядного таймера-счетчика и некоторого количества связанных с ним полностью идентичных каналов захвата/сравнения. Каждый из каналов в процессе инициализации может быть настроен на один из пяти режимов работы:

1)входного захвата;

2)не буферированного выходного сравнения;

3)буферированного выходного сравнения;

4)небуферированной широтно-импульсной модуляции (ШИМ);

5) буферированной ШИМ.

Каждый канал захвата/сравнения связан с одним из выводов МК. Функция входного или

выходного сигнала модуля процессора событий является альтернативной функцией линий порта Port D. МК MC68HC908GP32 имеет в своем составе два модуля процессора событий - TIM1 и TIM2. Каждый из модулей имеет по два канала захвата/сравнения.

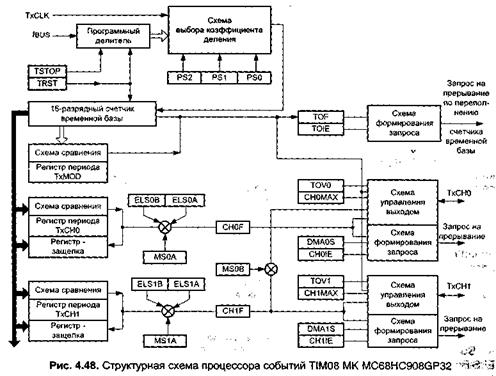

Структурная схема модуля двухканального процессора событий представлена на рис. 4.48. Шестнадцатиразрядный таймер-счетчик служит временной базой для модулей захвата/сравнения. Он подсчитывает импульсы тактовой частоты, поступающие на его вход. Все интервалы времени, которые генерируются или измеряются МК, измеряются числом периодов этой тактовой частоты.

В общем случае (модули TIM08 других МК семейства НС08) таймер-счетчик имеет два источника тактирования:

1)внутренний генератор, выполненный на основе программируемого делителя частоты ШИНЫ МК fBUS ;

2)внешний генератор, подключаемый к выводу TxCLK МК.

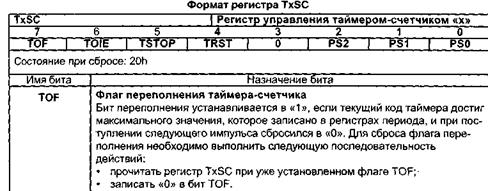

Выбор между внутренним и внешним генераторами, а также выбор коэффициента деления программируемого делителя частоты шины КTIMх определяется комбинацией битов PS2 – PSO0 регистра управления таймера-счетчика TxSC. Коэффициент деления КTIMх может принимать семь различных значений: 1, 2, 4, 8, 16, 32, 64. Максимальная частота сигнала внешнего генератора, подключаемого ко входу TxCLK, составляет 4 МГц при условии, что МК работает на предельной частоте внутренней шины fBUS= 8 МГц. Процессоры событий TIM1 и Т1М2 в составе МК MC68HC908GP32 не имеют выводов T1CLK и T2CLK в перечне выводов корпуса и, следовательно, могут использовать для тактирования только встроенный генератор.

Таймер-счетчик временной базы допускает программную установку периода работы. Если не предпринимать специальных действий при инициализации процессора событий, то коэффициент счета счетчика временной базы будет равен 216, т. е. счетчик проходит полный цикл от начального состояния кода $0000 до конечного состояния кода $FFFF. Если таймер-счетчик находится в состоянии $FFFF, то при поступлении на его вход очередного тактового импульса наступает переполнение таймера-счетчика. Счетчик переходит в состояние $0000, одновременно устанавливается флаг переполнения TOF. Переполнение счетчика не оказывает влияния на его работу: при поступлении следующих тактовых импульсов код в счетчике продолжает нарастать. Коэффициент счета таймера-счетчика может быть изменен посредством записи кода желаемого Ксч в двухбайтовый регистр периода TxMOD (TxMODH и TxMODL - старший и младший байты этого регистра, х - номер таймерного модуля, для TIM1 х = 1, для TIM2 х = 2). Вход сброса счетчика подключен к выходу цифрового компаратора (см. рис. 4.48), на один из входов которого поступает код текущего состояния таймера-счетчика, а на другой - код Ксч, за писанный в регистре TxMOD. Если эти коды равны, то при поступлении следующего тактового импульса счетчик сбрасывается в «0», и флаг переполнения ТОР устанавливается в «1». Диапазон допустимых значений Ксч составляет от 1 до (216-1). Таким образом, дискретность регулирования периода таймера-счетчика, который в режиме ШИМ образует период ШИМ-сигнала, составляет 16 бит.

Предусмотрена возможность пуска и останова таймера-счетчика под управлением

программы (бит TSTOP в регистре управления таймером-счетчиком TxSC). Кроме того,

счетчик и программируемый делитель частоты могут быть одновременно сброшены по

средством установки в «1» бита TRST в регистре TxSC. При этом все триггеры таймера-

счетчика установятся в «0», а программируемый делитель частоты будет настроен на

режим единичного коэффициента деления частоты внутренней шины МК. Заметьте, что

бит TRST не останавливает работу таймера-счетчика, с приходом очередного тактового

импульса состояние счетчика станет равным $0001. Сброс таймера-счетчика рекомендуется проводить в следующем порядке:

• остановите таймер-счетчик (бит TSOP = 1);

• выполните операцию сброса таймера-счетчика (бит TRST = 1);

• переинициализируйте биты PS2-PSO регистра TxSC, которые определяют источник и частоту тактирования;

• разрешите счет таймера-счетчика.

Таймера-счетчика в процессе счета может быть считан прикладной программой при обращении к регистрам текущего кода TxCNTH и TxCNTL. При обращении к регистру старшего байта код таймера-счетчика автоматически копируется в указанную регистровую пару. Поэтому, несмотря на то, что операции чтения старшего и младшего байтов разнесены во времени, вы прочитаете состояние таймера-счетчика в момент обращения к регистру старшего байта ТхСМТН. Такое решение предотвращает получение ложной информации в случае, если частота тактирования таймера-счетчика высока, и по этой причине в моменты обращения к регистрам TxCNTH и TxCNTL состояния счетчика различаются. Однако нельзя допускать ситуацию, при которой после прочтения старшего байта младший прочитан на будет. Повторное чтение старшего байта не сопровождается защелкиванием текущего кода таймера-счетчика в регистрах TxCNTH и TxCNTL.

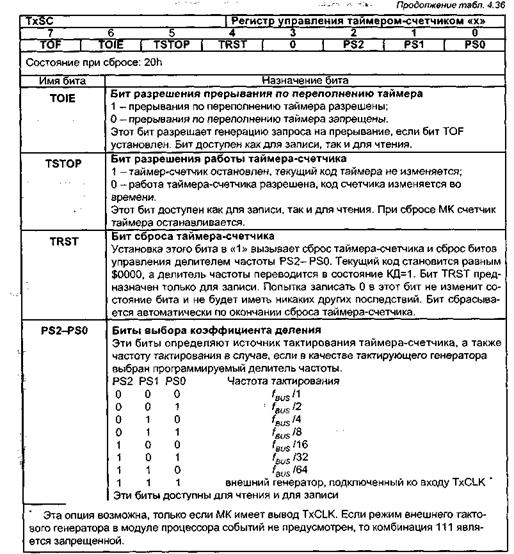

При переполнении таймера-счетчика устанавливается флаг переполнения ТОР в регистре управления TxSC (табл. 4.36) и генерируется запрос на прерывание, если бит разрешения прерывания TOIE установлен в «1», т. е. прерывания по переполнению таймера-счетчика разрешены.

Таблица 4.36

Для управления таймером-счетчиком модуля Т1М08 предусмотрены пять регистров специальных функций:

TxSC - регистр управления таймером-счетчиком «х», где «х» - имя модуля

процессора событий МК (для TIM1 х=1, для TIM2 х=2 );

TxMODH - регистр периода таймера-счетчика (старший байт);

TxMODL- регистр периода таймера-счетчика (младший байт);

TxCNTH - регистр текущего значения таймера-счетчика (старший байт);

TxCNTL - регистр текущего значения таймера-счетчика (младший байт).

Каждый канал захвата/сравнения в составе процессора событий связан с одним выводом МК (см. рис. 4.48). Вывод обозначают TxCHi, где i - порядковый номер канала захвата/ сравнения в составе процессора событий х. Например, Т1СНО - вывод канала 0 процессора событий TIM1. В режиме захвата аппаратные средства канала захвата/сравнения фиксируют моменты времени, когда логический сигнал на входе TxCHi изменяет свое состояние. В режимах выходного сравнения и широтно-импульсной модуляции (ШИМ) канал захвата/сравнения формирует импульсный сигнал с заданными временными параметрами на выходе TxCHi. Направление передачи сигнала по линии TxCHi (вход или выход) определяется инициализацией каналов захвата/сравнения на тот или иной режим. Несмотря на то, что работа линииTxCHi в составе процессора событий является альтернативной функцией линии одного из портов ввода/вывода МК, состояние регистра направления передачи порта DDRx в этом случае значения не имеет.

Программно-логическая модель каждого канала захвата/сравнения включает три регистра: 16-разрядный регистр данных канала i (TxCHiH и TxCHiL - старший и младший байты этого регистра) и регистр управления каналом i - TxSCi. Функция регистра данных определяется режимом работы канала захвата/сравнения, регистр управления TxSCi служит для выбора этого режима и для обслуживания прерываний по запросам модуля захвата/сравнения.

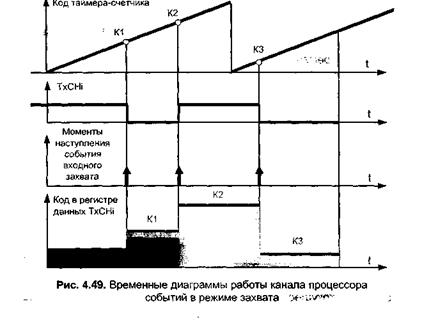

В режиме входного захвата аппаратные средства модуля следят за уровнем сигнала на входе TxCHi микроконтроллера (рис. 4.49).

При изменении уровня логического сигнала с «0» на «1» или наоборот вырабатывается строб записи, и текущее состояние таймера-счетчика временной базы копируется в 16-разрядный регистр данных TxCHi канала захвата/сравнения. Событие захвата отмечается установкой в «1» флага CHiF в регистре управления каналом с номером i. Этот флаг может быть считан программно, а если прерывания по событию канала i разрешены (флаг CHilE в регистре управления установлен), то модуль процессора событий выставляет запрос на прерывание. Предусмотрены три типа изменения сигнала на входе TxCHi MK, которые воспринимаются модулем захвата/сравнения, как событие захвата:

1)передний (нарастающий) фронт сигнала;

2)задний (падающий) фронт сигнала;

3)любое изменение логического уровня сигнала.

Выбор типа события захвата для модуля определяется битами ELSiB:ELSiA регистра

управления каналом TxSCi.

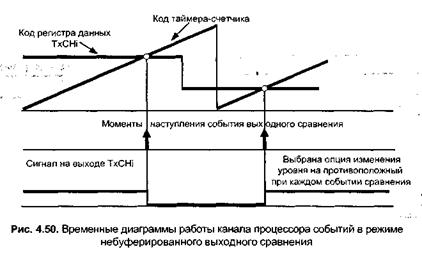

В режиме выходного сравнения аппаратные средства модуля непрерывно сравнивают изменяющийся во времени код таймера-счетчика с кодом, который записан в 16-разрядный регистр данных TxCHi модуля захвата/сравнения (рис. 4.50).

В момент равенства кодов аппаратные средства модуля устанавливают на выходе микроконтроллера TxCHi заданный уровень логического сигнала либо изменяют этот уровень на противоположный. При наступлении события выходного сравнения в регистре управления канала TxSCi устанавливается в «1» флаг CHiF, тот же, что и при наступлении события захвата. Аналогично предыдущему случаю этот флаг вызывает формирование запроса на прерывание, если прерывания от модуля i разрешены. Предусмотрены три типа изменения сигнала на выходе TxCHi MK в момент события выходного сравнения:

1)инвертирование сигнала на выходе;

2)установка низкого логического уровня

3)установка высокого уровня.

Выбор типа изменения выходного сигнала для модуля определяется битами ELSiB:ELSiA регистра управления каналом TxSCi.

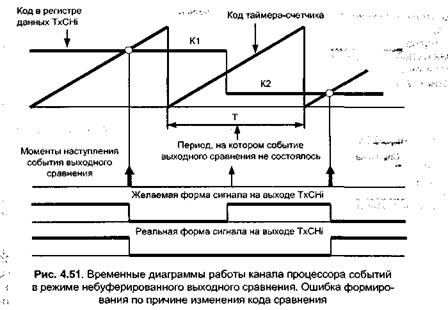

При работе в режиме выходного сравнения могут возникать нарушения алгоритма работы канала захвата/сравнения, приводящие к неправильному формированию сигнала на выходе TxCHi модуля. Причиной таких сбоев является изменение величины кода сравнения в процессе работы канала, а также конечное время выполнения программы перезагрузки кода сравнения в регистр данных канала TxCHi. Например, событие выходного сравнения еще не произошло, когда код в регистре данных TxCHi был изменен на меньшее значение (рис. 4.51). Причем это значение таково, что текущий код таймера-счетчика превышает его. В результате в текущем периоде работы таймера-счетчика события выходного сравнения уже не произойдет, так как равенство кодов наступит только в следующем периоде работы таймера-счетчика. Подобная ситуация исключается при использовании режима буферированного выходного сравнения.

В режиме буферированного выходного сравнения каналы захвата/сравнения объединяются в пары: канал 0 с каналом 1 (канал 2 с каналом 3, канал 4 с каналом 5 - в других МК семейства НС08). Канал с нечетным номером работает в режиме выходного сравнения. Канал с четным номером переводится в нерабочее состояние, и его нельзя использовать ни в каком из режимов работы. Вывод TxCHi MK, принадлежащий каналу с четным номером, автоматически конфигурируется в режим обычной линии ввода/вывода. Далее для определенности рассмотрим логику работы на примере пары 0 и 1. Сразу после инициализации в качестве источника кода сравнения модуль 0 использует регистры данных ТхСНО, принадлежащие модулю 0. После того, как событие сравнения произошло, в качестве источника кода сравнения могут использоваться как регистры данных канала 0, так и регистры данных канала 1. Выбор регистра данных осуществляется модулем автоматически: используется та пара регистров данных, в которую запись была произведена последней. По этой причине не следует новое значение кода сравнения записывать в текущий активный регистр данных канала. Эта операция в соответствии с принципом действия режима буферированного сравнения фактически переведет канал в режим не буферированного выходного сравнения. Никаких сбоев формирования сигнала на выходе TxCHi в режиме буферированного выходного сравнения не возникнет, если:

• производить запись нового кода сравнения в регистр неактивного канала;

• выполнять эту операцию в подпрограмме прерывания по событию выходного сравнения обслуживаемого канала.

Назначение режима буферированного выходного сравнения производится установкой бита MSiB в регистре управления каналом с номером 1=0. Регистр управления канала 1 в этом случае не оказывает влияния на работу канала 0 в режиме буферированного выходного сравнения. Однако для однозначного определения состояния неиспользуемой в режиме буферированного выходного сравнения линии ТхСШ канала 1 биты ELSiB:ELSiA регистра управления канала 1 должны быть установлены в «00».

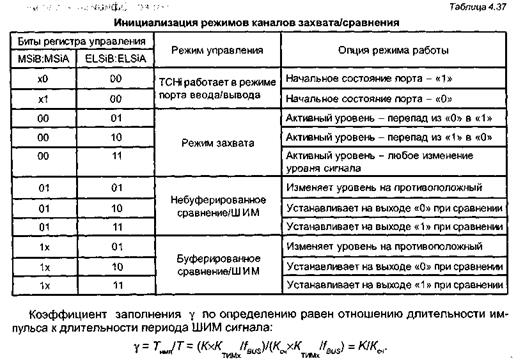

Особенности инициализации каналов захвата/сравнения поясняет табл. 4.37.

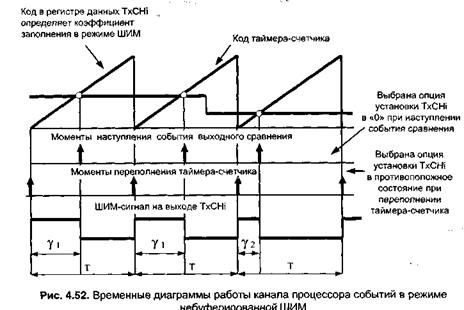

Режим не буферированного выходного сравнения может быть использован для получения на выходе модуля TxCHi широтно-модулированного импульсного сигнала. С этой целью следует запрограммировать логику изменения сигнала на выходе TxCHi следующим образом (рис. 4.52):

• при наступлении события выходного сравнения на выходе TxCHi устанавливается низкий логический уровень;

• при переполнении таймера-счетчика уровень сигнала на выводе инвертируется.

Вы получите ШИМ сигнал, у которого длительность импульса будет изменяться по закону:

Тимп =K/fтакт,

где К- код регистра данных канала, fтакт - частота тактирования таймера-счетчика.

Период широтно-модулированных импульсов определяется периодом таймера-счетчика:

Т = К сч/fтакт,

При тактированиии таймера-счетчика от внутреннего генератора период таймера-счетчика составляет:

Т = К сч  КТIМх/f BUS,

КТIМх/f BUS,

где КТIМх - коэффициент деления программируемого делителя частоты, К сч - коэффициент счета таймера-счетчика.

Из приведенного соотношения следует, что дискретизация коэффициента заполнения γ определяется выбранным коэффициентом счета К сч таймера-счетчика. Следовательно, модуль процессора событий TIM08 может реализовать ШИМ с дискретизацией коэффициента заполнения вплоть до 16 бит. При необходимости полярность импульсов ШИМ-сигнала может быть изменена. Для этого необходимо при инициализации выбрать следующие опции:

•при наступлении события выходного сравнения на выходе устанавливается высокий логический уровень;

•при переполнении таймера-счетчика уровень сигнала на выходе инвертируется.

Рассмотренный режим небуферированной ШИМ подвержен сбоям в работе так же, как и режим небуферированного выходного сравнения (рис. 4.52). Так, если вы станете менять код заполнения в течение периода, то при смене большего кода на меньший возможен пропуск момента сравнения и, как следствие, получение единичного коэффициента заполнения. Поэтому режим небуферированной ШИМ следует использовать в тех случаях, когда код коэффициента заполнения требуется изменять крайне редко. В остальных случаях следует использовать режим буферированной ШИМ.

Для получения буферированной ШИМ используют режим буферированного выходного сравнения, при котором каналы объединяются по парам, и для генерации ШИМ сигнала на одном выводе используются регистры сразу двух каналов захвата/сравнения. Вследствие этого число линий с ШИМ-сигналами для любого процессора событий TIM08 сокращается вдвое. Особенности инициализации модулей захвата/сравнения в режиме буферированной ШИМ определяются правилами инициализации канала на режим буферированного выходного сравнения.

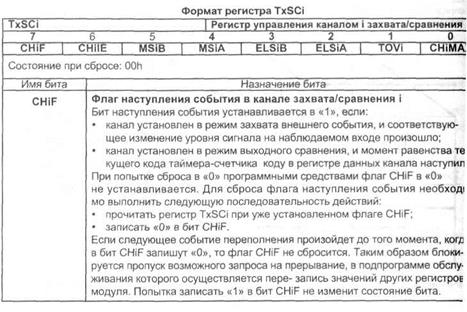

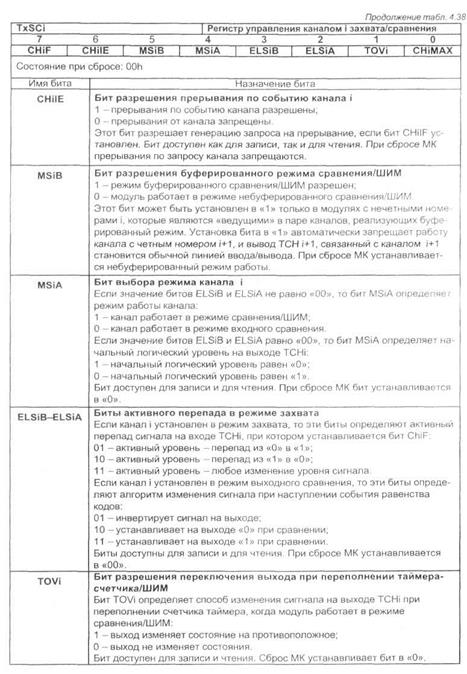

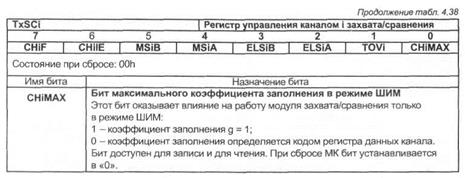

Формат регистра управления канала захвата/сравнения приведен в табл. 4.38.

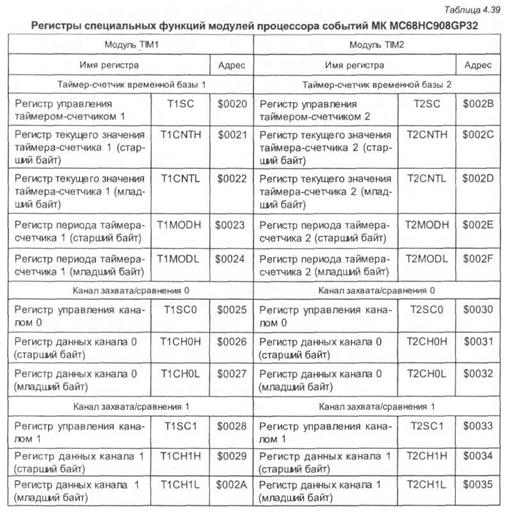

Регистры данных канала TxCHiH и TxCHiL являются 8-разрядными регистрами, которые доступны для чтения и для записи. Полный перечень регистров двух процессоров событий МК MC68HC908GP32 приведен в табл. 4.39.

|

Таблица 4.38.

|

| |

|

|

4.3.8. МОДУЛЬ ПОСЛЕДОВАТЕЛЬНОГО СИНХРОННОГО ИНТЕРФЕЙСА SPI08

Модуль последовательного периферийного интерфейса SPI08 предназначен для высокоскоростного обмена между МК и периферийными микросхемами, такими как АЦП и ЦАП, FLASH-память большой информационной емкости, часы реального времени. Модуль SPI08 обладает следующими характеристиками:

поддерживает два режима работы: ведущего (master) и ведомого (slave) приемопередатчиков; позволяет программно настраивать частоту обмена, причем в формировании сетки частот модули таймеров TIM08 и PIT08 не задействованы:

где Кт= 2, 8, 32, 128; максимальная частота обмена в режиме ведущего составляет 4,0 МГц, в режиме ведомого - 8,0 МГц;

•генерирует запросы на прерывание с раздельными векторами по завершению приема

очередного байта или по окончании передачи байта;

•генерирует два флага нарушения режима работы: при переполнении приемника и

при принудительной смене режима работы (ведущий/ведомый) в процессе незавершенного обмена;

•позволяет программно конфигурировать линии приема и передачи данных (MISO и

MOSI) как линии с открытым коллекторным выходом; объединение MISO и MOSI по

схеме «монтажное ИЛИ» делает модуль совместимым с протоколом интерфейса I 2C.

Контроллер SPI08 обслуживает стандартную шину SPI ,для чего имеет четыре линии:

MOSI-линия передачи данныхот ведущего к ведомому (Master Output Slave Input);

MISO -линия передачи данных от ведомого к ведущему (Master Input Slave Output);

SPSCK - линия сигнала синхронизации даных

SS-линия выбора ведомого.

Направление передачи каждой линии определяется выбором режима работы контроллера SPI08. Если назначен режим ведущего (бит MSTR регистра управления SPCR равен 1), то линии MOSI и SCK работают в режиме вывода, а линия МISО_в режиме ввода. Если назначен режим ведомого (MSTR = 0), то линии MOSI, SCK и  работают в режиме ввода, a MISO - в режиме вывода. В режиме ведущего линия может быть использована, как обычная линия ввода/вывода.

работают в режиме ввода, a MISO - в режиме вывода. В режиме ведущего линия может быть использована, как обычная линия ввода/вывода.

Обслуживание модуля SPI08 является альтернативной функцией для линий PTD (см. рис. 4. 44). Если бит разрешения работы контроллера модуля установлен SPE = 1, то независимо от значения соответствующих битов регистра направления передачи порта ввода/вывода его линии назначаются для работы в составе контроллера SPI08.

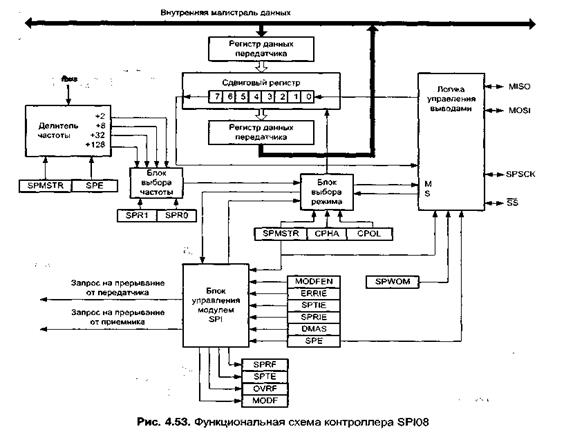

Функциональная схема контроллера SPI08 приведена на рис. 4.53. Основные элементы контроллера - 8-разрядный сдвиговый регистр (Shift Register) и два буферных регистра данных, программно доступных по одному и тому же адресу. При выполнении операции записи в регистр данных SPDR данные будут запомнены в буферном регистре передатчика. Буфер данных передатчика недоступен для чтения. Операция чтения регистра SPDR возвращает данные из буферного регистра приемника. Буфер данных приемника недоступен для записи.

Если контроллер настроен для работы в режиме ведущего, то обмен данными в любом из направлений (прием или передача) инициируется операцией записи байта в регистр данных. Этот байт сначала автоматически копируется в сдвиговый регистр, а затем

сдвигается в течение 8 тактов генератора синхронизации обмена на линию MOSI. Одновременно на линию SCK выдаются импульсы синхронизации. Каждый из импульсов синхронизации SCK, поступающих от ведущего на одноименный вход ведомого, вызывает операцию сдвига данных на один разряд в сдвиговом регистре принимающего устройства. В результате очередной бит, переданный ведущим по линии MOSI, запоминается в регистре-приемнике, но одновременно на линию MISO выдвигается очередной старший бит этого регистра. Бит с линии MISO фиксируется в сдвиговом регистре ведущего. При завершении передачи 8 бит данных от ведущего к ведомому в сдвиговом регистре ведущего окажется принятый байт данных от ведомого. Если пользователь желает реализовать передачу байта данных от ведущего к ведомому, то для осуществления обмена в программе ведущего в регистр данных контроллера SPI08 записывается передаваемый байт, а при завершении передачи бесполезные данные из регистра данных порта SPI08 просто не считываются. Если же пользователь желает реализовать прием байта данных, то для осуществления обмена в программе ведущего в регистр данных контроллера SPI08 записывается любой «ненужный» байт, а при завершении передачи принятый полезный байт данных считывается из регистра данных порта SPI08. Завершение передачи каждого байта данных отмечается установкой в «1» бита SPIF регистра состояния SPSR. Этот бит генерирует запрос на прерывание, если прерывания от модуля SPI разрешены (бит SPIE = 1). При обмене с высокими скоростями в режиме ведущего бит завершения передачи байта SPIF следует контролировать программно. Для этого после записи очередного байта в регистр данных следует прочитать регистр состояния SPSR, дождаться, пока бит SPIF не установится, а затем произвести считывание принятых данных или запись следующего передаваемого байта в регистр данных (в зависимости от направления передачи). Бит SPIF сбрасывается в «О» автоматически при выполнении последовательности из двух операций:

• чтение регистра состояния SPSR при установленном бите SPIF;

• чтение или запись в регистр данных SCDR.

Если контроллер SPI08 работает в режиме ведомого, то момент начала передачи определяет ведущий. Поэтому следует организовать прерывания по запросу от триггера SPIF, в подпрограмме обработки которого принятый байт будет прочитан из регистра данных и проанализирован, а при необходимости предоставления ведущему каких-либо данных очередной байт будет записан в регистр данных для последующей передачи при поступлении импульсов синхронизации SCK от ведущего.

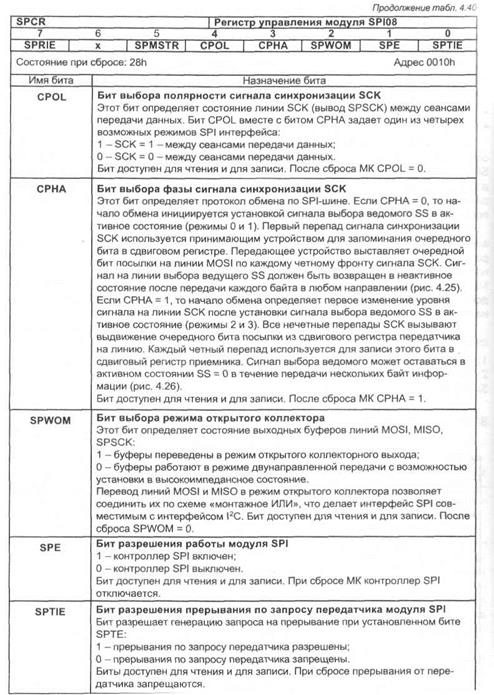

Контроллер SPI08 поддерживает 4 возможных режима SPI. Для задания детализированной временной диаграммы обмена следует использовать биты СРНА и CPOL регистра управления SPCR. Скорость обмена в режиме ведущего определяется программно настраиваемым коэффициентом делителя fBUS (биты SPR1:SPRO регистра управления). Максимальная скорость обмена составляет fBUS/2, минимальная - fвus/128. В режиме ведомого биты SPR1:SPRO не оказывают влияния на работу контроллера. Скорость обмена определяется ведущим, она может достигать fBUS.

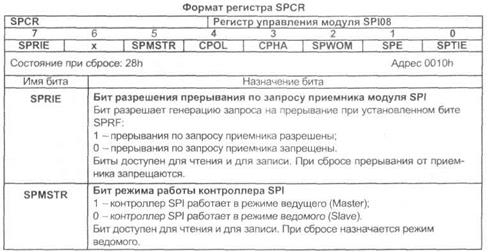

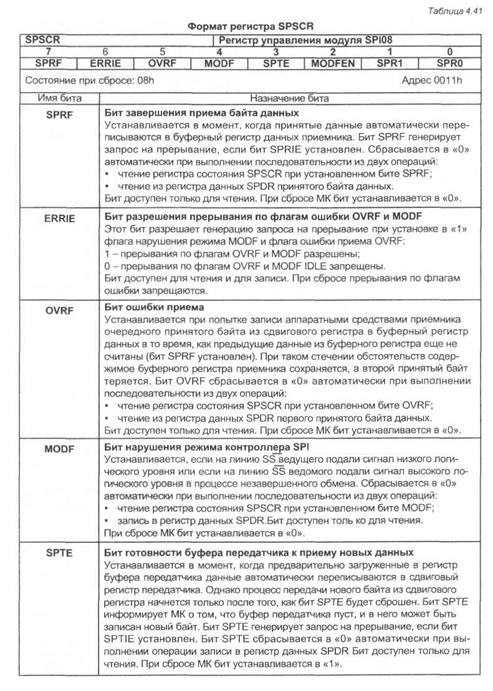

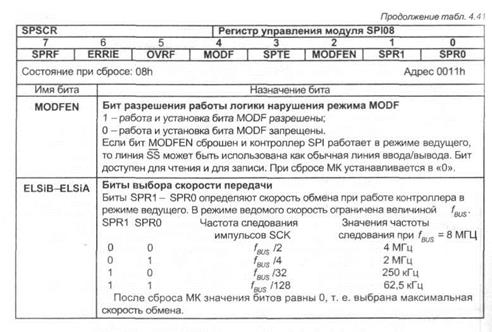

Программно-логическая модель модуля SPI08 включает три регистра специальных функций:

1)SPCR - регистр управления модуля SPI08;

2)SPSCR - регистр состояния модуля SPI08;

3)SPDR - регистр данных модуля SPI08.

Форматы регистров SPCR и SPSCR приведены в табл. 4.40 и 4.41. Регистр данных SPDR доступен по адресу 0012h.

|

Таблица 4.40

|

|

|