Система команд мк семейства нс08

Система команд CPU08 включает 90 инструкций.

Длина кода команды в байтах определяется типом инструкции и способом адресации. Команды CPU08 могут иметь однобайтовый, двухбайтовый, трехбайтовый и четырехбайтовый формат. Однобайтовыми командами в соответствии с теорией являются команды с неявной адресацией (INH) и с индексной адресацией без смещения (IX: LDA, х). В двухбайтовом формате представлены команды с непосредственной (IMM: LDA #орг), прямой (DIR: LDA орг) и индексной с однобайтовым смещением (1X1: LDA орг,х) адресацией. Трехбайтовый формат имеют команды с прямой расширенной адресацией (EXT: LDA орг), индексной со смещением в два байта адресацией (IX2: LDA орг.х) и адресацией по ука-

зателю стека со смещением в один байт (SP1: LDA opr.SP). Четырехбайтовыми командами являются только команды с адресацией по указателю стека со смещением в два байта (SP2: LDA opr,SP).

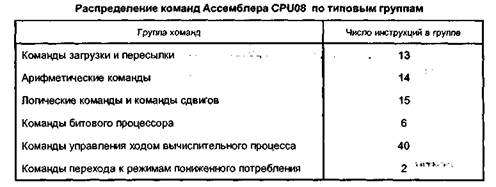

Множество команд делится на 6 традиционных групп, каждая из которых рассмотрена ниже. Распределение команд по группам приведено в табл. 4.22.

Таблица 4.22

|

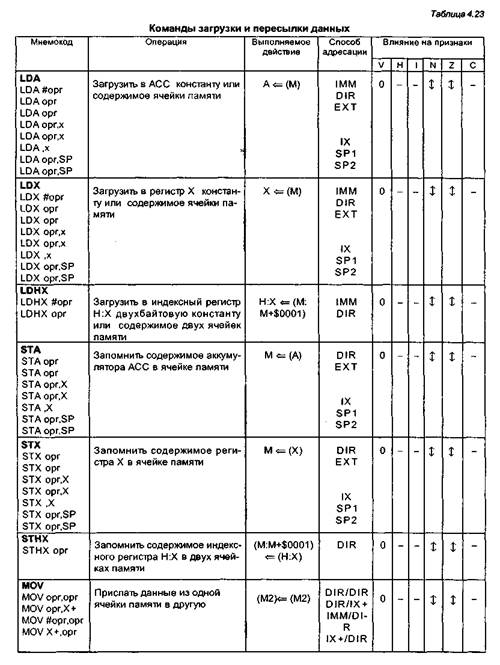

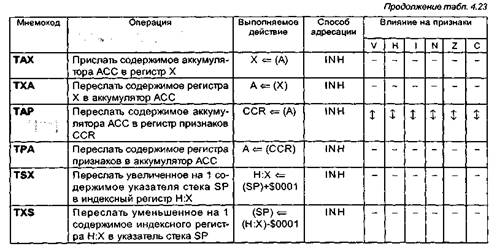

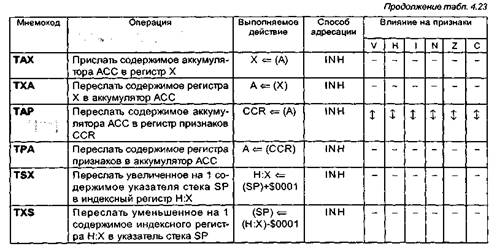

Команды загрузки и пересылки данных.Команды этой группы осуществляют перемещение данных между ячейками памяти и регистрами центрального процессора(табл.4.23).

|

Отличительная особенность команд загрузки и пересылки CPU08 - установка признаков нуля Z и знака N в соответствие со значением перемещаемого числа. Следует также обратить внимание на способы адресации, которые могут быть использованы в команде LDHX:

• двухбайтовый регистр индексной адресации Н:Х может быть загружен двухбайтовой константой;

• или содержимым двух ячеек памяти, но на адрес первой из этих ячеек наложено ограничение; этот адрес должен быть однобайтовым $00 - $FF.

Команда MOV выполняет пересылку данных из одной ячейки памяти в другую, минуя регистры центрального процессора. Команда MOV может быть использована в одной из четырех модификаций:

MOV #data,adr ; Загрузить константу в прямо адресуемую ячейку памяти.

MOV adrl ,adr2 ; Переслать данные из одной прямо адресуемой ячейки памяти в другую прямо адресуемую.

MOV x+, adr ; Переслать данные из ячейки памяти, адрес которой указан в индексном

;регистре Н:Х, в прямо адресуемую ячейку памяти.Содержимое

; Н:Х увеличивается на 1 после пересылки.

MOV adr,x+ ; Переслать данные из прямо адресуемой ячейки памяти в ячейку, адрес

;которой указан в индексном регистре Н:Х. Содержимое Н:Х увеличива-

;вается на 1 ; после пересылки.

Отметим, что одна из ячеек памяти (источник или приемник операнда) в формате команды обязательно прямо адресуемая, т. е. ее адрес может находиться в пределах от $00 до $FF. Именно это адресное пространство в МК семейства НС08 занимают регистры специальных функций периферийных модулей. Следовательно, команда MOV может быть органично использована для приема или передачи информации в регистры данных портов ввода/вывода, АЦП, последовательных портов и т. д.

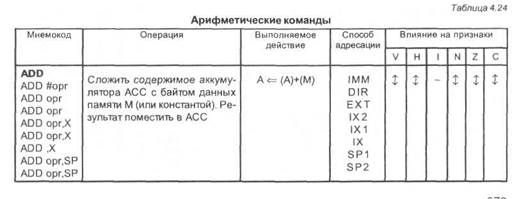

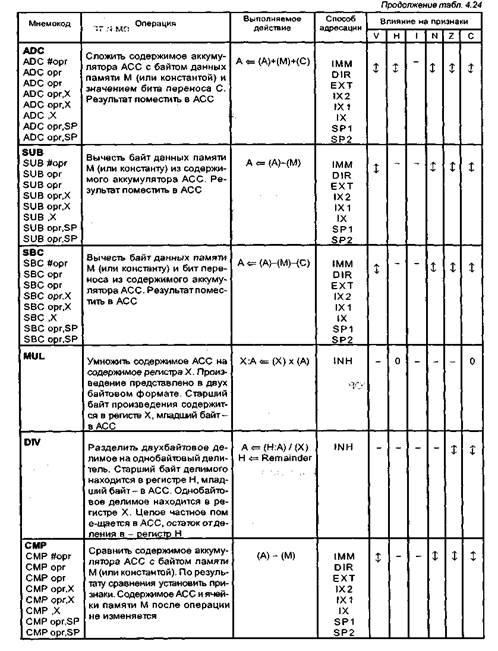

Арифметические команды.Данную группу образуют 14 команд (табл. 4.24), выполняющие операции сложения (ADD и ADC), вычитания (SUB и SBC), инкремента и декремента (INC и DEC), однобайтового и двухбайтового сравнения, умножения и деления (MUL и DIV). Команды сложения (ADD и ADC), вычитания (SUB и SBC) и однобайтового сравнения (CMP и СРХ) могут быть использованы с восемью различными способами адресации. Однако сравнение двухбайтового индексного регистра Н:Х может быть выполнено только с двухбайтовой константой, которая задана во втором и третьем байтах команды, или с содержимым двух ячеек памяти, адрес первой из которых равен $00 -$FF. Команда умножения MUL выполняет операцию целочисленного беззнакового умножения. Сомножители расположены в регистрах АСС и X, двухбайтовое произведение - в Н:АСС. Время выполнения операции составляет 5 машинных циклов. Команда деления DIV выполняет целочисленное беззнаковое деление двухбайтового делимого (Н:АСС) на однобайтовый делитель (X). Целое частное расположено в АСС, остаток - в Н. Делитель X сохраняется без изменения. Время выполнения операции - 7 машинных циклов.

Следует обратить внимание на формат представления операнда в командах AIX и AIS. Однобайтовый операнд должен быть представлен в дополнительном коде со знаком:

AIX #$FF ; Вычесть 1 из содержимого двухбайтового индексного регистра Н:Х.

AIX #$80 ; Вычесть 128 из содержимого двухбайтового индексного регистра Н:Х.

AIS #$01 ; Увеличить на 1 указатель стека SP.

AIS #$FF ; Вычесть 1 из указателя стека SP.

Несмотря на то, что инструкции инкремента и декремента над содержимым двухбайтовых регистров центрального процессора в системе команд CPU08 отсутствуют, эти операции могут быть выполнены с использованием команд AIX и AIS.

Фрагмент программы вычисления однобайтовой контрольной суммы таблицы из однобайтовых чисел:

TABLE: equ $7000 ;Определить начальный адрес таблицы.

org $6EOO ; Определить начальный адрес программы.

LDHX #511 ;Задать число элементов таблицы.

CLRA ;Очистить регистр контрольной суммы.

ADDLOOP: ADD TABLE.x ; Получить частичную контрольную сумму.

AIX #$FF ;Уменьшить число элементов на 1.

СРНХ #0 ;Проверка: все элементы перебраны? Команда AIX не

;устанавливает признаки, поэтому следует применить

; команду СРНХ.

BPL ADDLOOP ; Продолжить, если не все элементы перебраны

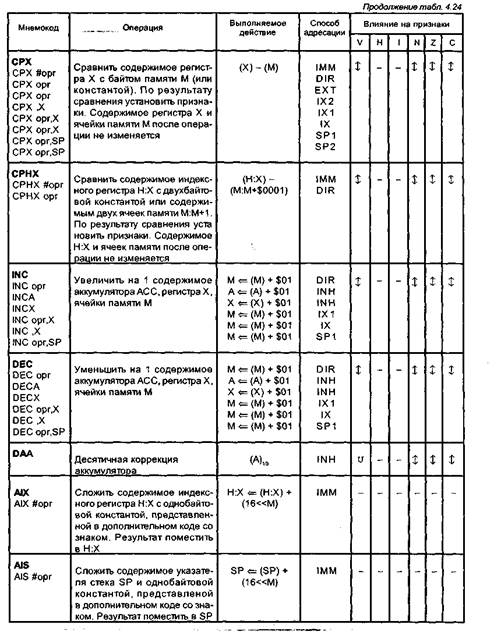

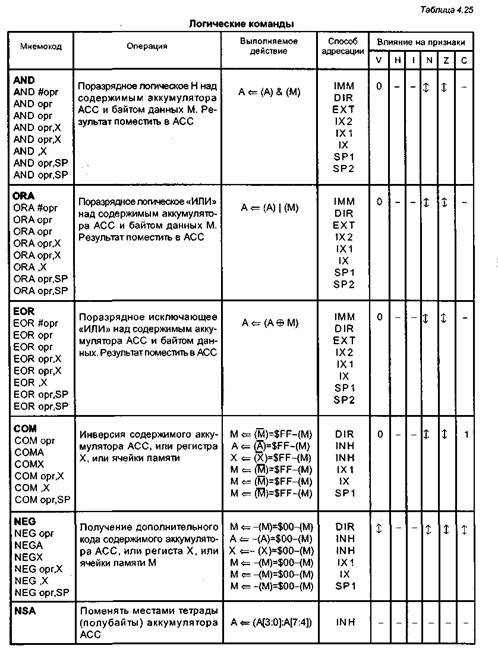

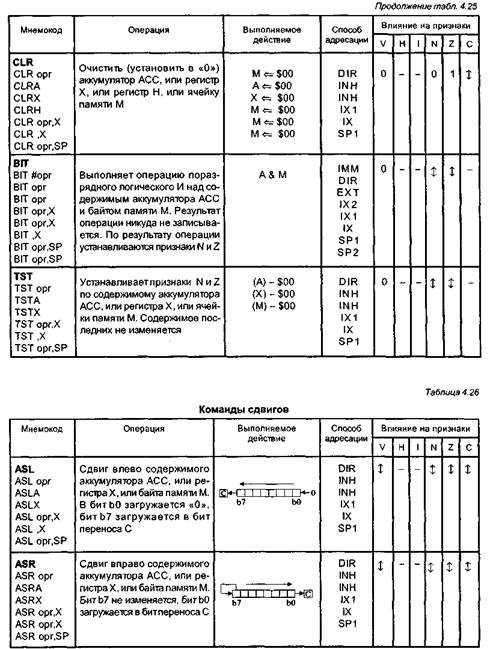

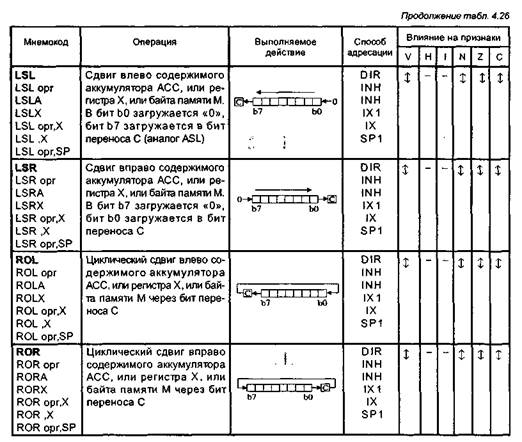

Логические команды и операции сдвига. Данную группу образуют 15 команд, которые выполняют операции логического И, ИЛИ, Исключающего ИЛИ, различные операции сдвига, операции взятия обратного и дополнительного кода. Следует обратить внимание на специальные команды установки признаков без изменения содержимого тестируемых регистров и ячеек памяти (TST и BIT). Все логические команды модифицируют флаги в регистре признаков. Типы инструкций данной группы приведены в таблицах 4.25 и 4.26

|

.

|

|

|

|

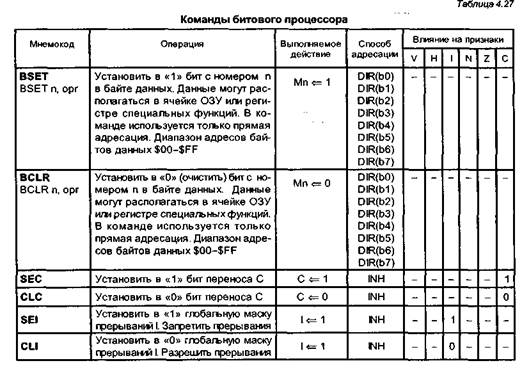

Команды битового процессора.Данную группу образуют 6 команд (табл. 4.27). Совокупность этих команд называют битовым процессором. Наличие команд битового процессора позволяет существенно сократить управляющие программы по объему кода и времени выполнения. Обратите внимание, что команды BSET и BCLR действуют только на ячейки памяти с однобайтовыми адресами $00 -$FF и не действуют на регистры центрального процессора. Следует правильно указывать операнды в командах BSET и BCL:

BSET 3,$35 ;Установить в 1 бит D3 в ячейке памяти с адресом $35.

BSET 0,$FF ;Установить в 1 бит DO в ячейке памяти с адресом $FF.

BCLR 3,$35 ;Сбросить (установить в 0) бит D3 в ячейке памяти с адресом $35.

Команды условного перехода по значениям отдельных битов BRSET и BRCLR могут быть отнесены как к группе команд битового процессора, так и к группе команд управления.

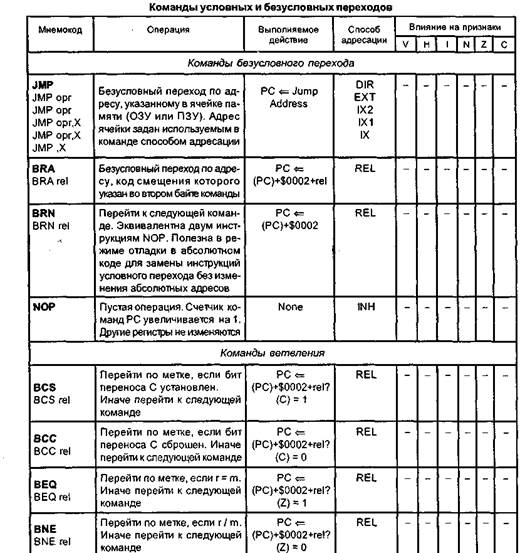

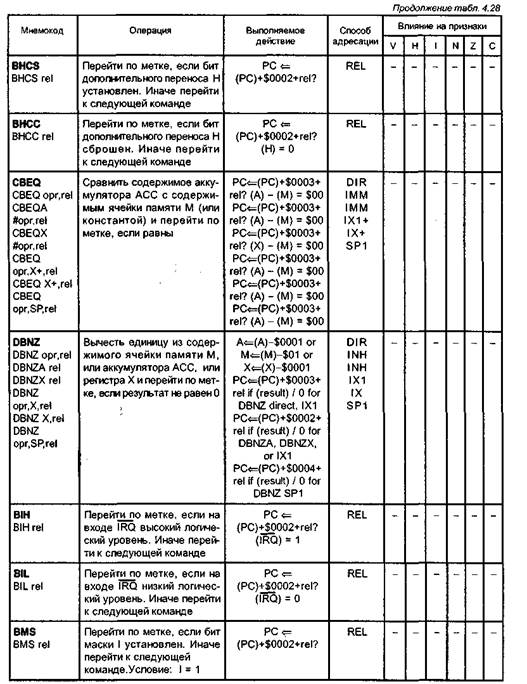

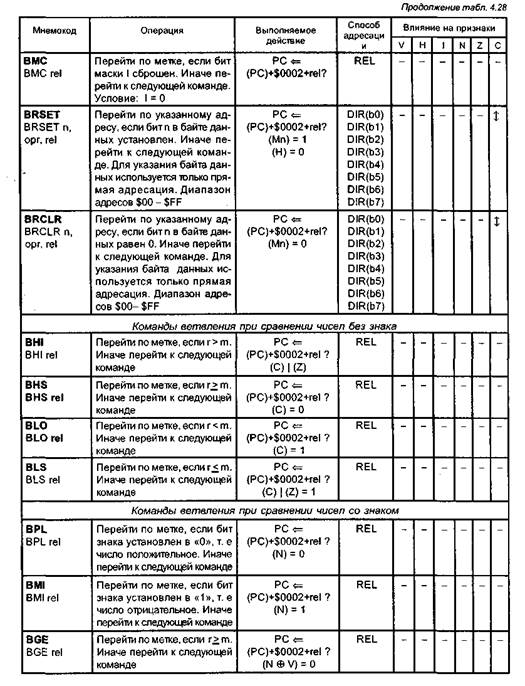

Команды передачи управления.Группа команд передачи управления является самой многочисленной группой. Она содержит 40 инструкций, которые делятся на две под

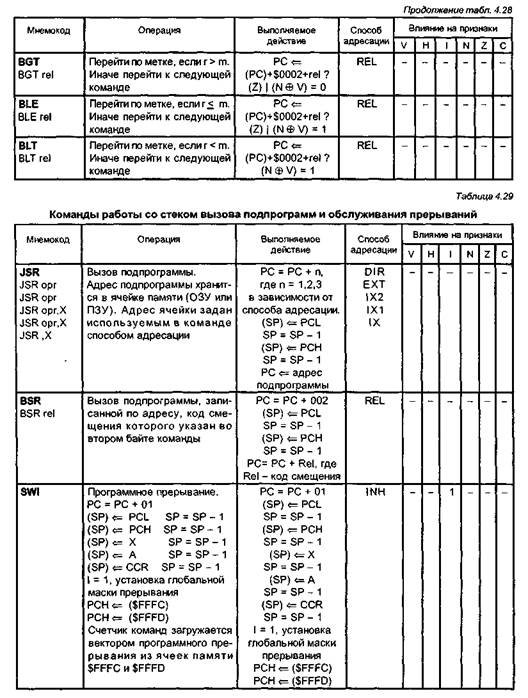

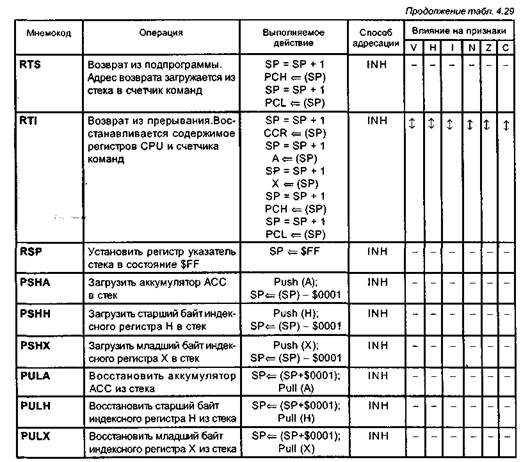

группы: команды условных и безусловных переходов (табл. 4.28), команды вызова подпрограмм и обслуживания прерываний(табл.4.29).

Центральный процессор CPU08 может использовать три команды условного перехода: традиционную трехбайтовую команду JMP и две двухбайтовых команды BRA и BRN. Команда JMP отличается расширенным набором способов задания адреса перехода. Этот адрес может быть в том числе определен одним из способов индексной адресации, что позволяет разместить изменяемый в ходе выполнения программы адрес в одной из ячеек ОЗУ. Двухбайтовая команда BRA реализует безусловный переход в пределах смещения от -128 до +127 относительно текущего адреса. Эта команда позволяет более экономно расходовать память. Команда BRN аналогична команде NOP, но имеет двухбайтовый формат. Значение смещения, которое указано во втором байте команды, смысла не имеет. Эта команда полезна для режимов отладки программного обеспечения в абсолютном коде. Она позволяет заменить инструкцию ветвления на инструкцию NOP без изменения байта смещения rel в формате команды условного перехода.

Центральный процессор CPU08 может использовать три команды условного перехода: традиционную трехбайтовую команду JMP и две двухбайтовых команды BRA и BRN. Команда JMP отличается расширенным набором способов задания адреса перехода. Этот адрес может быть в том числе определен одним из способов индексной адресации, что позволяет разместить изменяемый в ходе выполнения программы адрес в одной из ячеек ОЗУ. Двухбайтовая команда BRA реализует безусловный переход в пределах смещения от -128 до +127 относительно текущего адреса. Эта команда позволяет более экономно расходовать память. Команда BRN аналогична команде NOP, но имеет двухбайтовый формат. Значение смещения, которое указано во втором байте команды, смысла не имеет. Эта команда полезна для режимов отладки программного обеспечения в абсолютном коде. Она позволяет заменить инструкцию ветвления на инструкцию NOP без изменения байта смещения rel в формате команды условного перехода.

Группа команд ветвления чрезвычайно широка. Кроме переходов по традиционным условиям С, Z, N, Н, реализованы переходы по комбинациям флагов С и Z для сравнения операндов в прямом коде без знака, а также по комбинациям флагов С, Z, и У для сравнения операндов в дополнительном коде со знаком.

Группа команд ветвления чрезвычайно широка. Кроме переходов по традиционным условиям С, Z, N, Н, реализованы переходы по комбинациям флагов С и Z для сравнения операндов в прямом коде без знака, а также по комбинациям флагов С, Z, и У для сравнения операндов в дополнительном коде со знаком.

Особое внимание следует обратить на команды CBEQ и DBNZ:

CBEQ opr.rel ; Сравнить аккумулятор АСС с содержимым прямоадресуемой

; ячейки памяти и перейти по метке, если они равны.

CBEQ x+,rel ; Сравнить аккумулятор АСС с содержимым ячейки памяти,

;адрес которой содержится в индексном регистре и перейти

;по метке, если они равны. Содержимое индексного регистра Н:Х

;увеличивается на 1 после выполнения сравнения.

DBNZ x.rel ; Уменьшить на 1 содержимое ячейки памяти, адрес которой ..............

; указан в индексном регистре Н;Х, и перейти по метке, если

; результат не равен 0.

DBN2A rel ; Уменьшить на 1 содержимое аккумулятора АСС и перейти по

;метке, если результат не равен 0.

Команды CBEQ и DBNZ имеют достаточно широкий набор способов адресации(см. табл. 4.28).

Таблица 4.28

|

|

|

|

Среди команд вызова подпрограмм и обслуживания прерываний следует выделить команду программного немаскируемого прерывания SWI. Механизм программного прерывания позволяет обратиться к какой-либо подпрограмме прерывания по ходу выполнения прикладной программы и воспользоваться подпрограммой прерывания как обычной подпрограммой. Наличие в системе команд инструкции программного прерывания SWI предоставляет такую возможность. Эта команда автоматически загружает в стек регистры CCR, АСС, X и увеличенное на единицу содержимое счетчика команд PC, а затем осуществляет переход по адресу, который указан в ячейках памяти $FFFC и $FFFD сегмента векторов прерывания. Этот адрес может быть начальным адресом подпрограммы прерывания или же находиться внутри нее. При выходе из подпрограммы прерывания команда RTI восстановит содержимое регистров центрального процессора, и МК продолжит выполнение прикладной программы с команды, которая была следующей за командой SWI. Таким образом, программисту предоставляется возможность обращения в произвольный момент времени к фрагменту подпрограммы прерывания, который начинается с произвольно выбранной инструкции внутри подпрограммы прерывания, но заканчивается обязательно командой RTI.

|

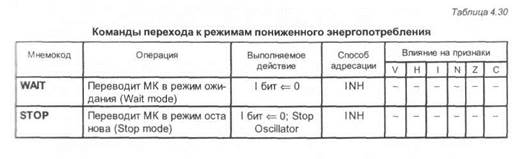

Команды управления режимами энергопотребления.Команды WAIT и STOP переводят МК в один из режимов пониженного энергопотребления(табл.4.30).