Порты ввода/вывода мк 8051 ан

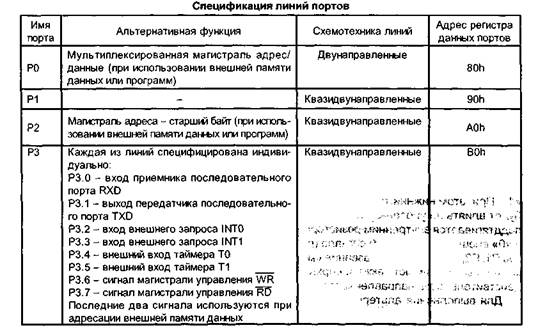

Линии ввода/вывода МК 8051 АН сгруппированы в четыре 8-разрядных параллельных порта РО, Р1, Р2 и РЗ. Эти порты могут использоваться как для обмена данными с внешними устройствами в параллельном коде, так и для выполнения альтернативных функций. Спецификация линий ввода/вывода МК 8051 АН приведена в табл.4.17.

Таблица 4.17

При использовании по своему прямому назначению каждая линия любого порта может быть задействована для ввода или для вывода информации независимо от направления передачи других линий этого же порта. Каждый порт отображается в карте памяти МК регистром специальных функций с тем же именем (РО, Р1, Р2, РЗ). Для обращения к портам ввода/вывода следует использовать те же команды, что и для регистров специальных функций с побитным доступом, например:

MOV А, Р1 ;Считать состояние линий порта Р1 и переслать данные в АСС.

MOV P3, #67h ;Выдать на линии порта РЗ код 67h.

SETB P0,2 ; Установить в 1 линию 2 порта РО.

Обратите внимание: обращаться к регистрам данных портов РО - РЗ следует с использованием прямой адресации. Как и для других регистров специальных функций, обращение с использованием косвенной адресации по указателям @RO и @R1 не приведет к успеху. Все регистры данных портов допускают прямую побитную адресацию. Отдельные линии портов ввода/вывода могут быть установлены и сброшены с использованием команд битового процессора.

На рис. 4.3 и 4.4 приведены функциональные схемы аппаратных средств для одной линии портов Р0 и РЗ. Порты Р1 и Р2 имеют такую же схемотехнику, что и порт РЗ. Все линии портов имеют защелки на основе D-триггеров, которые объединены в группы по восемь и составляют регистры данных портов Р0 - РЗ. Драйвер каждой линии имеет в своем составе также формирователь выходного уровня и входной буфер. Из рис. 4.3 следует, что на внутреннюю магистраль данных может быть прочитано как состояние линии ввода, так и содержимое одноименного разряда защелки. Часть МК во время выполнения читают именно защелку. Такие команды относятся к группе команд «чтение-модификация-запись». Режим «чтение-модификация-запись» автоматически реализуется, когда порт одновременно является операндом и местом назначения результата, например:

ANL Р1,А ; Логическое И над содержимым порта Р1 и АСС. Результат - в порт.

ORL Р2,А ; Логическое ИЛИ над Р2 и АСС. Результат - в порт Р2.

XRL РЗ,А ; Исключающее ИЛИ над РЗ и АСС. Результат - в порт РЗ.

JBC P2.3,Label ; Переход, если в адресуемом бите Р2.3 единица и последующий сброс

; этого бита.

INC РО ; Инкремент порта РО.

DEC Р1 ; Декремент порта Р1.

DJNZ Р2, Label ; Декремент порта Р2 и переход, если его содержимое не равно 0.

SETB Р1.2 ; Установить бит Р1.2.

CLR Р1.3 ;Сбросить бит Р1.3.

Последние две команды также относятся к рассматриваемой группе, хотя это и не очевидно.

Порты ввода/вывода МК 8051 АН не имеют специальных регистров направления передачи данных. Для перевода линии в режим ввода следует записать в ее защелку «1». При этом нижний транзистор драйвера линии перейдет в закрытое состояние и не будет влиять на уровень сигнала входной линии. При этом у портов Р1, Р2, и РЗ линия поддтягивается внутренним резистором RPULLUP к уровню «1», но может быть переведена в «О» внешним источником сигнала (рис. 4.4). Благодаря такой схемотехнике линии портов Р1, Р2, и РЗ получили название «квазидвунаправленных». Драйверы линий порта Р0, кроме нижнего, имеют также и верхний транзистор. Поэтому линии порта Р0 являются действительно двунаправленными.

Для выполнения альтернативных функций линиями порта РЗ следует в соответствующий разряд регистра порта записать «1». Во время обращения к внешней памяти во все разряды порта Р0 автоматически записываются «1», значения защелок порта Р2не изменяются. Нагрузочная способность линий портов МК 8051 АН невелика: выходные линии портов Р1, Р2, РЗ могут работать на одну TTL-схему, линии порта Р0 - на две.

ТАЙМЕРЫ

Микроконтроллер 8051 АН имеет два 16-разрядных таймера-счетчика, которые именуют таймер 0 и таймер 1. Каждый из них может работать как в режиме программируемого таймера, так и в режиме счетчика событий (см. п. 4.1.6). При работе в режиме таймера на вход счетчика поступает импульсная последовательность с частотой fBUS, т. е. период тактирования счетчика равен длительности машинного цикла. При работе в режиме счетчика событий на вход счетчика таймера поступает импульсная последовательность со входов Т0/Р3.5 и Т1/Р3.6 соответственно. Максимальная частота этой внешней последовательности импульсов составляет fBUS/2. Каждый из модулей таймер 0 или таймер 1 - имеет четыре режима работы.

В режиме 0 модуль таймера представляет собой 8-разрядный счетчик ТНх, на вход которого поступает импульсная последовательность с выхода программно недоступного делителя на 32 (х - номер модуля таймера, ТН0 для таймера 0, ТН1 для таймера 1). Последний выполнен на основе младшего байта счетчика TLx (рис. 4.38). При переполнении счетчик ТНх изменяет состояние с 0FFh на 00h и продолжает счет. Одновременно устанавливается триггер переполнения TFx. Коэффициент счета счетчика в режиме 0 составляет 256. Изменение коэффициента счета требует записи начального кода под управлением прикладной программы каждый раз после наступления события переполнения.

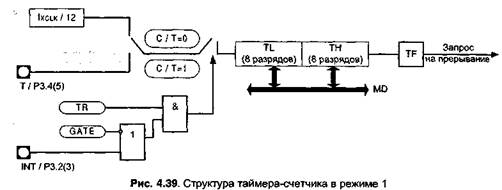

В режиме 1 таймер представляет собой 16-разрядный счетчик. Регистр ТНх - старший байт этого счетчика, TLx - младший байт (рис. 4.39). При переполнении состояние счетчика изменяется с FFFFh на 0000h, устанавливается триггер переполнения TFx, 16-разрядный счетчик продолжает счет поступающих импульсов. Коэффициент счета счетчика в режиме 1 составляет 216. Как и в режиме 0, изменение этого коэффициента требует «программного вмешательства» на каждом периоде работы счетчика.

В режиме 2 работа таймера организована таким образом, что переполнение 8-разрядного счетчика TLx приводит не только к установке флага TFx, но и автоматически перезагружает в TLx содержимое старшего байта счетчика таймера ТНх, которое было задано предварительно (рис. 4.40). Перезагрузка оставляет содержимое ТНх неизменным.

В этом режиме появляется возможность задания пользователем коэффициента счета счетчика в диапазоне от 1 до 256. При этом в процессе работы счетчик не будет требовать программного обслуживания, если коэффициент счета не изменяется.

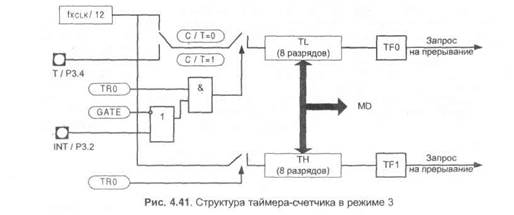

В режиме 3 может работать только таймер 0, таймер 1 блокирован, как если бы бит разрешения работы таймера 1 TR1 был сброшен. Таймер 0 распадается на два независимых 8-разрядных счетчика, причем TLO управляется битами управления таймера 0, а ТНО - битами управления таймера 1 (рис. 4.41).

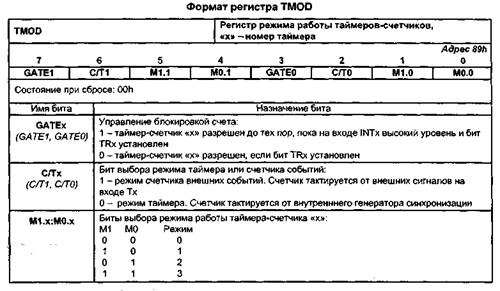

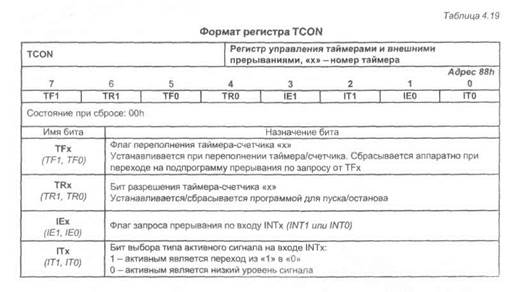

Режимы работы таймеров задают два регистра специальных функций:

TMOD - регистр режима работы таймеров-счетчиков;

TCON - регистр управления таймерами и внешними прерываниями.

Формат этих регистров приведен в табл. 4.18 и 4.19. Кроме того, таймер 0 и таймер 1 имеют по два программно доступных 8-разрядных регистра: ТН0 и TL0 для таймера 0, ТН1 и TL1 для таймера 1.

Таблица 4.18

|

|

|

АСИНХРОННЫЙ ПОРТ

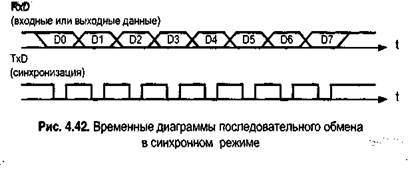

Режим 0.В этом режиме информация и передается и принимается через внешний вывод входа приемника RXD. Принимаются или передаются 8 бит данных. Через внешний вывод передатчика TXD выдаются импульсы синхронизации, которые сопровождают каждый принимаемый или передаваемый бит. Частота синхросигналов равна fBUS, т. е. скорость обмена в синхронном режиме равна частоте внутренней шины МК. Временные диаграммы обмена в синхронном режиме приведены на рис. 4.42.

Режим 1.В этом режиме передаются через TXD или принимаются из RXD 10 бит информации: старт-бит, 8 бит информации, стоп-бит (см. рис. 4.20). Скорость приема/ передачи - величина переменная и задается таймером.

Режим 2.В этом режиме передаются через TXD или принимаются из RXD 11 бит информации: старт-бит, 8 бит данных, программируемый девятый бит и стоп-бит (см. рис. 4.21). При передаче девятый бит может принимать произвольное значение 0 или 1, но чаще этот бит используется для повышения достоверности обмена путем контроля по четности. Для этого при передаче информации в него помещается значение признака Р из регистра PSW. После приема информации другим МК признак четности для 8 бит данных вычисляется снова и сравнивается с принятым в девятом бите признаком Р. Если они совпадают, то считается, что обмен произошел без нарушения исходных данных. Частота приема/передачи выбирается программно: либо 1/32, либо 1/64 частоты кварцевого резонатора fXCLK, который используется в качестве времязадающего элемента генератора синхросигналов МК.

Режим 3.Совпадает с режимом 2 во всех деталях, за исключением частоты приема/ передачи. Последняя является величиной переменной и задается таймером.

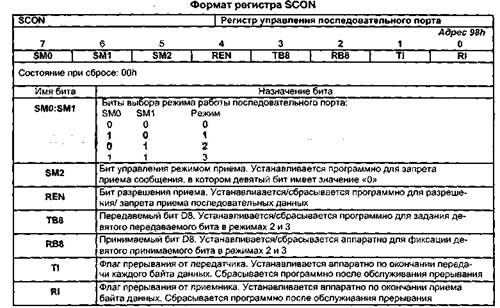

Два регистра специальных функций используются для работы с последовательным портом в МК MCS-51:

SCON - регистр управления последовательного порта (табл. 4.20);

SBUF - регистр данных последовательного порта.

Таблица 4.20

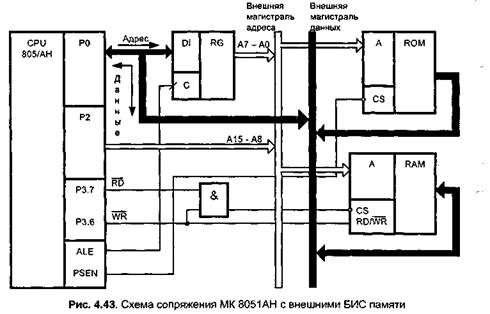

4.2.8. ОРГАНИЗАЦИЯ ДОСТУПА К ВНЕШНЕЙ ПАМЯТИ

В микропроцессорных системах, построенных на основе МК MCS-51, возможно использование двух типов внешней памяти (см. п. 4.2.1): постоянной памяти программ и постоянной или оперативной памяти данных. Доступ к внешней памяти программ осуществляется с использованием специального управляющего сигнала стробирования PSEN. Доступ к внешней памяти данных обеспечивают сигналы RD/P3.7 и WR/P3.6 внешней магистрали управления МК (см. рис. 4.32).

При обращении к внешней памяти программ МК формирует двухбайтовый адрес. Доступ к внешней памяти данных возможен как с использованием двухбайтового адреса (MOV A,@DPTR), так и с однобайтовым адресом (MOVX A,@Ri). В цикле обращения к памяти старший байт двухбайтового адреса фиксируется в регистре-защелке порта Р2. При этом ранее записанное в порт Р2 значение восстанавливается в следующем цикле. Если используется однобайтовый адрес внешней памяти, то содержимое порта Р2 не претерпевает изменений.

Функциональная схема сопряжения МК 8051 АН с внешними БИС ПЗУ программ и ОЗУ данных приведена на рис. 4.43. Через порт 0 в режиме мультиплексирования во времени выдается сначала младший байт адреса, а затем осуществляется передача данных. Сигнал ALE должен быть использован для записи младшего байта адреса во внешний регистр-защелку. Выходы регистра-защелки и линии порта Р2 составляют внешнюю 16-разряднуу магистраль адреса для БИС памяти. В качестве сигнала стробирования чтения памяти программ используется сигнал PSEN. При обращении к внешней памяти данных в качестве стробирующих используются сигналы RD и WR.